Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

101 - 120 / 333

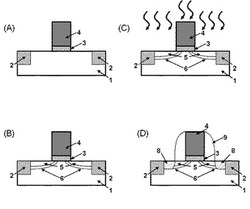

半導体装置の製造方法

【課題】不純物の高活性化を図るとともに、半導体装置の性能の低下を防止できる半導体装置の製造方法を提供すること。

【解決手段】基板1上に、シリコン酸化膜よりも比誘電率の高い材料により構成された高誘電率絶縁膜を有するゲート絶縁膜3を形成する工程と、前記ゲート絶縁膜3上に金属を有するゲート電極4を形成する工程と、前記ゲート電極4をマスクとして、前記基板に不純物を注入して、エクステンション領域5を形成する工程と、前記不純物が注入された前記基板1をフラッシュランプアニールあるいはレーザアニールにより、熱処理する工程とを含む。熱処理する工程は、前記基板1に対し所定のピーク強度のパルス光を照射する第一の工程と、前記第一の工程のパルス光のピーク強度よりも低いピーク強度のパルス光を照射する第二の工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

CMISトランジスタの製造方法

【課題】本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供する。

【解決手段】ゲート絶縁膜103とN−metal104と多結晶シリコン106とが当該順に積層した第一のゲート構造G1を形成する。ゲート絶縁膜103と多結晶シリコン106とが当該順に積層した第二のゲート構造G2を形成する。第一、二のゲート構造G1,G2をマスクした状態で、各ゲート構造G1,G2の両脇における半導体基板101上を、シリサイド化させる。そして、第一、二のゲート構造G1,G2を構成する多結晶シリコン106を、シリサイド化させる。

(もっと読む)

半導体装置

【課題】メタルをゲート電極材料に用いたCMIS素子の閾値を低減する。

【解決手段】p型MISトランジスタQpのゲート絶縁膜5上に設けられたp型ゲート電極7は、順に、カチオン比でAlが10%以上50%以下のTiAlNから構成される第1金属膜30と、TiNから構成され、膜厚が5nm以下の第2金属膜31と、Siを主成分として含有する導電体膜32とが積層された構造を有している。また、n型MISトランジスタQnのゲート絶縁膜5上に設けられたn型ゲート電極6は、順に、第2金属膜31と、導電体膜32とが積層された構造を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

(もっと読む)

窒化ジルコニウム界面層を有するキャパシター構造

【課題】

下部電極の材料がTiNまたはTiであり、かつ誘電体層がZrとAlとOとを主成分とする複合酸化物の誘電体を含む層であるキャパシターの場合、誘電体に変質反応に生じ、キャパシターの静電容量が低下する。

【解決手段】

積層された多層の薄膜より成るキャパシター構造において、下部電極層と、下部電極界面層と、誘電体層と、上部電極層が順次積層された構造を持ち、前記下部電極層の材料がTiNまたはTiであり、前記下部電極界面層の材料がZrを主成分とする窒化物であり、前記誘電体層がZrとAlとOとを主成分とする複合酸化物の誘電体を含む層であることにより、キャパシターの静電容量を向上させる。

(もっと読む)

半導体装置及びその製造方法

【課題】MIPS構造のデュアル・メタルゲートを有する半導体装置において高集積化を進展させつつ、PN境界部配線の断線や高抵抗化等の問題を防止できる半導体装置及びその製造方法を提供する。

【解決手段】NMISトランジスタのゲート電極122aは、第1の金属含有導電膜104aと、第1の金属含有導電膜104a上に形成された第3の金属含有導電膜113とから構成されており、PMISトランジスタのゲート電極122bは、第2の金属含有導電膜104bと、第2の金属含有導電膜104b上に形成された第3の金属含有導電膜113とから構成されている。第3の金属含有導電膜113は、第1の金属含有導電膜104a及び第2の金属含有導電膜104bのそれぞれと接するように、第1の金属含有導電膜104a上から素子分離領域102上を経て第2の金属含有導電膜104bの上まで連続的に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】精度良く形成された第1,第2のゲート電極を実現すると共に、ゲート幅方向の幅が縮小化された素子分離領域を実現する。

【解決手段】第1のMISトランジスタは、第1のゲート絶縁膜13a上に形成された第2の金属膜30aからなる第1のゲート電極30Aと、第1のゲート電極の側面上から第1の活性領域10aにおける第1のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第2のMISトランジスタは、第2のゲート絶縁膜13b上に形成され第1の金属膜14bと第1の金属膜上に形成された導電膜30bとからなる第2のゲート電極30Bと、第2のゲート電極の側面上から第2の活性領域における第2のゲート電極の側方に位置する領域の上面上に跨って形成された絶縁膜27とを備え、第1の金属膜と第2の金属膜とは、互いに異なる金属材料からなり、第1,第2のゲート電極の上面上には絶縁膜が形成されていない。

(もっと読む)

半導体装置およびその製造方法

【課題】同一導電型のチャネル領域を有し、かつ閾値電圧の異なる複数の半導体素子を有する半導体装置を提供する。

【解決手段】閾値電圧が互いに異なる2つのトランジスタが同一半導体基板上に形成された半導体装置において、トランジスタのゲート電極は、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成された、第2金属を含み第1金属を主成分とする金属層とを含み、更に、一方のトランジスタが、ゲート絶縁膜と金属層との間に、第2金属の酸化膜を含む。

(もっと読む)

窒化金属膜作製装置、窒化金属膜作製方法及び窒化金属膜

【課題】窒化金属膜及び該窒化金属膜を作製する窒化金属膜作製装置及び作製方法を提供する。

【解決手段】基板3を支持台2に載置して収容したチャンバ1の内部において、ヘリウムで希釈した塩素ガスプラズマにより、タンタルで形成した被エッチング部材14をエッチングして塩化タンタルガスからなる前駆体17を生成し、基板3の温度を被エッチング部材14の温度よりも低くして前駆体17を基板3に吸着させ、塩素ガスプラズマにより吸着した前駆体17を還元してタンタル成分を基板3に成膜する際に、窒素ガスをプラズマ化して得られる窒素ガスプラズマによりタンタル成分を窒化して、基板3に窒化金属膜18を成膜する窒化金属膜作製方法において、窒素ガスの供給量を制御して窒素ガス/ハロゲンガス流量比を0より大きく0.1以下とし、窒化金属膜18の窒素原子と金属原子の原子組成比であるN/M比を0より大きく1以下となるようする。

(もっと読む)

半導体素子及びその製造方法

【課題】 オーミック電極とバリアメタル層の密着強度を向上させる。

【解決手段】 半導体素子の製造方法は、(a1)半導体積層構造を準備する工程と、(b1)前記半導体積層構造上にオーミック電極層を成膜する工程と、(c1)前記オーミック電極層上にAuを含む接着層を成膜する工程と、(d1)前記工程(c1)から大気開放せずにバリアメタル層を成膜する工程とを含む。

(もっと読む)

デュアルゲート半導体装置の製造方法およびその構造

【課題】2つのゲート配線間の接続を容易に、かつ低抵抗で行えるデュアルゲート半導体装置を提供する。

【解決手段】半導体基板を準備する工程と、半導体基板上に、それぞれがゲート絶縁膜と第1ゲート金属膜とを含む、第1および第2の電極を形成する工程と、第1および第2の電極を埋め込むように、層間絶縁層を形成する工程と、第1および第2の電極の上部を層間絶縁層から露出させる工程と、第2の電極の第1ゲート金属膜を選択的に除去する工程と、第1および第2の電極を覆うように、層間絶縁層上に、第2ゲート金属膜およびゲート配線膜を堆積する工程と、第2ゲート金属膜とゲート配線膜をパターニングして、第1ゲート電極と第2ゲート電極とを形成するとともに、第1ゲート電極と第2ゲート電極とをゲート配線膜で接続する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】ゲート長に依存する仕事関数の変動を抑えることができる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜14上の多結晶シリコン膜を露出した後、半導体基板11を400℃まで加熱し、その温度が安定した後に、その温度を保持したまま、例えばスパッタリング法によりニッケル膜21を全面に形成する。ニッケル膜21の厚さは、シリコン酸化膜20上で60nmとする。この結果、シリコン酸化膜20上にはニッケル膜21が形成されるが、多結晶シリコン膜の表面に到達してきたニッケルは、そこに堆積するのではなく、多結晶シリコン膜と反応し、多結晶シリコン膜の全体がニッケルシリサイド膜22に変化する。従って、pMOS領域1には、p型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成され、nMOS領域2には、n型不純物を含有するニッケルシリサイド膜22からなるゲート電極が形成される。

(もっと読む)

半導体装置

【課題】曲げ等の外力が加わり応力が生じた場合であってもトランジスタ等の損傷を低減する半導体装置を提供することを目的とする。

【解決手段】可撓性を有する基板上に設けられた第1の島状の補強膜と、第1の島状の補強膜上に、チャネル形成領域と不純物領域とを具備する半導体膜と、チャネル形成領域の上方にゲート絶縁膜を介して設けられた第1の導電膜と、第1の導電膜及びゲート絶縁膜を覆って設けられた第2の島状の補強膜とを有している。

(もっと読む)

スパッタターゲットの製造方法

【課題】ヒロック、エッチング残渣、ITO等との電気化学反応の発生を防止した低抵抗な配線膜を再現性よく成膜することができ、かつスパッタ時におけるダスト発生を抑制したスパッタターゲットの製造方法を提供する。

【解決手段】Y、Sc、La、Ce、Nd、Sm、Gd、Tb、Dy、Er、Th、Sr、Ti、Zr、V、Nb、Ta、Cr、Mo、W、Mn、Tc、Re、Fe、Co、Ni、Pd、Ir、Pt、Cu、Ag、Au、Cd、Si、PbおよびBから選ばれる少なくとも1種の第1の元素を0.001〜30原子%の範囲で含み、残部がAlからなるインゴットまたは焼結体を、大気溶解法、真空溶解法、急冷凝固法、粉末冶金法で作製するにあたって、インゴットまたは焼結体にCを第1の元素量に対して20原子ppm〜37.8原子%の範囲で含有させ、得られたインゴットや焼結体を加工してスパッタターゲットを作製する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型MOSFETの特性を劣化させることなく、pチャネル型MOSFETの閾値電圧を低減した相補型半導体装置する。

【解決手段】相補型半導体装置の製造方法が、シリコン基板を準備する工程と、ゲート絶縁膜を形成する工程と、ゲート絶縁膜を覆うようにAl含有膜を形成する工程と、nチャネル型MOSFET形成領域の上のAl含有膜を、過酸化水素水を用いて選択的に除去する工程と、シリコン基板の上にゲート導電層を形成する工程と、ゲート絶縁膜、Al含有膜、およびゲート導電層をエッチングして、ゲート絶縁膜、Al含有膜、およびゲート導電層を含むpチャネル型MOSFETのゲート電極と、ゲート絶縁膜、およびゲート導電層を含むnチャネル型MOSFETのゲート電極とを形成する工程と、pチャネル型MOSFETのゲート電極において、Al含有膜のAl元素をゲート絶縁膜中に拡散させる工程とを含む。

(もっと読む)

液晶表示装置及び電子機器

【課題】低比抵抗を有し、且つ上記ゲッタリング工程に十分耐えうる電極構造の必要に応じ、新規な電極構造を有する液晶表示装置を提供する。

【解決手段】絶縁表面を有する基板上に、多層構造を有するゲート電極と、前記基板、前記ゲート電極の上面および側面を覆う保護膜と、前記保護膜を覆って形成されたゲート絶縁膜と、前記ゲート絶縁膜上に接して、ソース領域と、ドレイン領域と、前記ソース領域と前記ドレイン領域の間に形成されたチャネル形成領域と、を有する半導体素子からなる半導体回路を備える。保護膜は、高温処理を施した場合、基板からの不純物の拡散を抑えることができ、基板の不純物濃度に左右されることなく、良好なTFT特性を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

半導体装置およびその製造方法

【課題】nウエル及びpウエルに形成されたpMOS及びnMOSトランジスタのしきい値を精密に制御し、かつ製造容易にする。

【解決手段】nウエル2及びpウエル3上にゲート絶縁膜5を形成し、nウエル2上のゲート絶縁膜5上にpMOSトランジスタ11のしきい値制御用の第1金属膜6を、pウエル3上のゲート絶縁膜5上に第1金属膜6と異なる材料からなるnMOSトランジスタ12のしきい値制御用の第2金属膜7を形成する。そして、第1金属膜6上に高融点金属シリサイドからなる第1ゲート電極8pを、第2金属膜7上に高融点金属シリサイドからなる第2ゲート電極8nを形成する。しきい値は金属膜6、7で定まるから安定する。この金属膜6は薄く、容易にパターニングできる。

(もっと読む)

窒化物系半導体装置用多層電極構造

【課題】窒化物系半導体層に対する優れた付着力を有しかつ電解液に対する優れた耐腐食性をも有する窒化物系半導体装置用多層電極構造を提供する。

【解決手段】窒化物系半導体装置用多層電極構造は、窒化物系半導体層(101)上に順次積層される第1、第2、第3、および第4の電極層(102、103、104、105)を含み、第1電極層(102)は金属窒化物を含み、第2電極層(103)は相対的に低い標準電極電位を有する金属を含み、第4電極層(105)は相対的に高い標準電極電位を有する金属を含み、第2と第4の電極層に挟まれた第3電極層(104)は相対的に中間の標準電極電位を有する金属を含んでいることを特徴としている。

(もっと読む)

101 - 120 / 333

[ Back to top ]