Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

121 - 140 / 333

窒化物半導体用電極および窒化物半導体装置

【課題】窒化物半導体を用いた窒化物半導体装置における電極の信頼性を向上することができる窒化物半導体用電極およびそれを含む窒化物半導体装置を提供する。

【解決手段】窒化物半導体上に形成される電極であって、窒化物半導体上に形成される金属窒化物層と、金属窒化物層上に形成される第1金属層と、第1金属層上に形成される第2金属層とを備え、第1金属層は、金属窒化物層に含まれる金属と同一の金属元素を含む窒化物半導体用電極とおよびそれを含む窒化物半導体装置である。

(もっと読む)

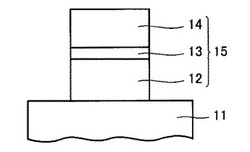

半導体装置の製造方法および半導体装置

【課題】仕事関数が所望の値に制御されたメタルゲート電極を備える半導体装置を提供する。

【解決手段】半導体基板2上に、ゲート絶縁膜4を介して、N等を含有する仕事関数制御層5、SiまたはAlを含んだ中間層6、およびMoN層等の低抵抗層7が積層された構造を有するメタルゲート電極を形成する。その形成時には、ゲート絶縁膜4上に仕事関数制御層5、中間層6および低抵抗層7の各層の積層後、ゲート加工を行い、LDD領域9、サイドウォール8およびソース・ドレイン領域10を順に形成して、半導体基板2に導入した不純物の活性化アニールを行う。仕事関数制御層5と低抵抗層7との間に中間層6を設けたことにより、仕事関数制御層5へのあるいは仕事関数制御層5からのN等の拡散が抑制され、その仕事関数の変動が抑制されるようになる。

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

nチャネルMOSトランジスタおよびその製造方法、半導体装置

【課題】ゲートファーストプロセスで形成できる、金属化合物をゲート電極パターンとして使うnチャネルMOSトランジスタにおいて、pチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物に対し、前記nチャネルMOSトランジスタのゲート電極パターンに使われる金属化合物の仕事関数差を増大させる。

【解決手段】nチャネルMOSトランジスタは、p型シリコン活性領域上にゲート絶縁膜を介して形成された導電性金属窒化物よりなるゲート電極パターンと、前記p型シリコン活性領域中、前記ゲート電極パターンの一方および他方の側にそれぞれ形成されたn型のソースおよびドレイン領域と、を含み、前記導電性金属窒化物は、SiおよびV族元素を含む。

(もっと読む)

半導体装置の製造方法

【課題】p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

(もっと読む)

半導体ウエハ上に膜を構築するためのチャンバ

【課題】抵抗率が改善された、共形性の高い拡散バリアの、インシチュウによる構築を遂行する。

【解決手段】本発明の一態様では、処理チャンバと、シャワーヘッドと、ウエハ支持体と、RFシグナル手段とを有していてもよい。シャワーヘッドを具備することにより、処理チャンバ内にガスを供給する。ウエハ支持体は、処理チャンバ内でウエハを支持するために具備される。シャワーヘッドに第1のRFシグナルを供給しまたウエハ支持体に第2のRFシグナルを供給するために、RFシグナル手段がシャワーヘッドとウエハ支持体の両方に結合していてもよい。あるいは、RFシグナル手段は、ウエハ支持体にRFシグナルを供給するためにウエハ支持体だけに結合していてもよい。本発明の態様を実施することによりアルミニウムや銅等のコンタクトメタルの拡散を防止する拡散バリアの能力を、向上させることができる。

(もっと読む)

半導体装置の製造装置

【課題】メタルキャップ層の製造工程におけるパーティクルの発生や組成比の変動を抑制させて、半導体装置の信頼性と生産性を向上させた半導体装置の製造装置に関するものである。

【解決手段】成膜チャンバ33は、第1カソード40aと第2カソード40bを備え、各カソード40a,40bに、それぞれZrを含む第1ターゲット42aと、BNを主成分とする第2ターゲット42bを搭載する。そして、成膜チャンバ33は、各外部電源を駆動して第1ターゲット42aと第2ターゲット42bとを同時にスパッタし、第1絶縁層の表面と第1配線の表面、又は、第2絶縁層の表面と第2配線の表面に、ZrBNを主成分とするメタルキャップ層を成膜させる。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETとpチャネル型MISFETで異なる金属膜を使用する場合であっても、両方のゲート電極を同時に加工できる技術を提供する。

【解決手段】pチャネル型MISFET形成領域に改質膜11を形成している。改質膜11は、ポリシリコン膜9にリンを導入することにより形成されている。この改質膜11は、ポリシリコン膜9よりもエッチング速度が速くなる性質がある。このことから、pチャネル型MISFET形成領域において、改質膜11とポリシリコン膜9をすべてエッチングする際、nチャネル型MISFET形成領域においては、ポリシリコン膜9がすべてエッチングされずに一部が残存する。これにより、pチャネル型MISFET形成領域に形成されている膜の総膜厚と、nチャネル型MISFET形成領域に形成されている膜の総膜厚の差が緩和される。

(もっと読む)

ショットキーダイオードを備える相変化メモリ素子

【課題】相変化メモリ素子を提供する。

【解決手段】基板上に一方向に延伸しているワードラインと、ワードライン上に位置する第1半導体パターンと、第1半導体パターン上に位置するノード電極と、第1半導体パターンとノード電極との間に形成されたショットキーダイオードと、ノード電極上に位置する相変化抵抗体と、を備える半導体メモリ素子。

(もっと読む)

半導体素子およびその製造方法

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】空気の層に基づくパッシベーションの膜の不整合性による不連続性の問題を解決し、高耐圧特性に優れたトランジスタの提供を課題とする。

【解決手段】III−V族窒化物からなる半導体層と、その上に、ソース/ドレイン電極と、両サイドを前記ソース/ドレイン電極に挟まれ、かつゲート電極を備えるIII−V族窒化物からなる半導体よりも高い誘電率を有する誘電体膜とが形成されており、前記ゲート電極が、前記誘電体膜の一部を窒化したものであり、さらにセカンドメタルで被覆されていることを特徴とするヘテロ接合電界効果型トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極構造が異なるNch絶縁ゲート型電界効果トランジスタとPch絶縁ゲート型電界効果トランジスタのゲート電極形状を安定化させる。

【解決手段】半導体装置50には、Nch MISFETとPch FMISFETが半導体基板1上に設けられる。半導体基板1上に、Nch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜8、及び絶縁膜10が積層形成される。半導体基板1上に、Pch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜9、及び絶縁膜10が積層形成される。ゲート電極膜9はゲート電極膜8よりもゲート電極膜同時加工時での補正膜厚分だけ薄く形成されている。

(もっと読む)

半導体装置の製造方法

【課題】N−chトランジスタとP−chトランジスタとの境界の寸法制御性に優れ、工程数の増加を最小限に抑制しながら、N−chトランジスタ及びP−chトランジスタのゲートパターンの高さが可能な限り揃った構造を実現する。

【解決手段】基板上のHigh−k膜よりなる絶縁膜上にポリシリコンを形成する。該ポリシリコン膜をエッチングする際にハロゲン系ガスを用いた低バイアス処理を施すことにより、下地のHigh−k膜の膜質を改善しながら、N−chトランジスタ及びP−chトランジスタに独立した仕事関数を持つ金属電極を形成する。

(もっと読む)

半導体素子及びその製造方法

【課題】MOSFET等のデバイスのための高誘電率膜の製造方法を提供する。

【解決手段】Si基板101上のSiO2膜(又はSiON膜)102上にHf金属膜103をスパッタし、それを熱酸化処理してHfSiO膜104を形成する。その上にTi金属膜105をスパッタし、それを熱酸化処理して、TiO2膜106を形成する。TiO2膜106上に、TiN金属膜107を堆積させる。これら一連の処理は、大気に晒すことなく真空中で一貫して行われる。形成されたTiN/TiO2/HfSiO/SiO2/Si構造は、EOT<1.0nm, 低リーク電流, ヒステリシス<20mVを満たしている。

(もっと読む)

金属ケイ素窒化物の被着方法

【課題】金属アミド、ケイ素前駆体及び窒素源ガスガスを前駆体として用いてプラズマ雰囲気下で循環式膜被着によって金属ケイ素窒化物膜を形成するための方法を提供する。

【解決手段】金属アミド前駆体をパルス送りする工程、未反応金属アミドをパージ除去する工程、プラズマ雰囲気下で反応チャンバ内に窒素源ガスを導入する工程、未反応窒素源ガスをパージ除去する工程、ケイ素前駆体をパルス送りする工程、未反応ケイ素前駆体をパージ除去する工程、プラズマ雰囲気下で反応チャンバ内に窒素源ガスを導入する工程、及び未反応窒素源ガスをパージ除去する工程を含む被着方法。

(もっと読む)

半導体素子及びそのゲート形成方法

【課題】高誘電定数を有する物質からなるゲート絶縁膜を有する半導体素子及びそのゲート形成方法を提供する。

【解決手段】素子分離膜202によりアクティブ領域が画定されている半導体基板200を提供する段階と、前記アクティブ領域上にゲート絶縁膜204を形成する段階と、前記ゲート絶縁膜204上にキャッピング膜206を形成する段階と、前記キャッピング膜206及び前記ゲート絶縁膜204を有する半導体基板200に対してアニール工程を施す段階と、前記アクティブ領域の一部にフルシリサイドゲート208を形成する段階とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のMISトランジスタと第2のMISトランジスタとで相異なる絶縁材料からなるゲート絶縁膜を精度良く実現する。

【解決手段】N型MISトランジスタNTrは、半導体基板100における第1の活性領域100a上に形成された第1のゲート絶縁膜105aと、第1のゲート絶縁膜上に形成された第1のゲート電極108aとを備え、P型MISトランジスタPTrは、半導体基板における第2の活性領域100b上に形成され、第1のゲート絶縁膜とは異なる絶縁材料からなる第2のゲート絶縁膜103bと、第2のゲート絶縁膜上に形成された第2のゲート電極108bとを備え、第1のゲート電極と第2のゲート電極とは、素子分離領域上において、上部領域が互いに電気的に接続されていると共に、下部領域が互いに第1のゲート絶縁膜と同じ絶縁材料からなる側壁絶縁膜105xyを挟んで分離されている。

(もっと読む)

凹部充填方法

【課題】凹部を隙間無く充填する。

【解決手段】本発明は基板11の表面の凹部12が形成された面に、金属膜15を形成する成膜工程と、金属膜にエッチングガスのイオンを入射させるエッチング工程とを交互に繰り返す。成膜工程で凹部12に突き出すように形成されるオーバーハング部19はエッチング工程で除去されるので、次の成膜工程の時に凹部12の開口は塞がれておらず、凹部12内部の金属膜15を成長させることができる。

(もっと読む)

拡散バリアフィルムを含む半導体素子の形成方法

【課題】電気抵抗が低く、下部導電体と上部導電体間の拡散を防止する、拡散バリアフィルムの形成方法を提供する。

【解決手段】下部導電体102を含む基板100上に層間絶縁膜104を形成する。これに形成された開口部106に補助拡散バリア膜108を形成する。この上に拡散バリアフィルム120を形成する。この膜は、金属有機化学気相蒸着法による金属窒化物で形成され、部分的にプラズマ処理される。この結果、プラズマ処理された層とプラズマ処理されない層の積層膜となる。これにより、拡散バリアフィルムの比抵抗を減少させると共に、優れたバリア特性を有することができる。さらにこの上に粘着金属層122、第1アルミニウム膜130、第2アルミニウム膜132を形成する。これらの膜をパターンニングして上部導電体とプラグとする。

(もっと読む)

アクティブマトリクス表示装置及びその製造方法

【課題】製造工程数を削減すると共に生産性を向上させる。

【解決手段】TFTアレイ基板11は、絶縁基板21を備えている。絶縁基板21上には、一部にポリシリコン層22が形成されている。このポリシリコン層22は、TFT素子14を構成する、チャネル領域22a、ソース領域22b及びドレイン領域22cを有している。ポリシリコン層22上には、ソース領域22b及びドレイン領域22cのそれぞれ一部を覆うように配線層23が形成されている。配線層23並びに配線層23が積層されていないポリシリコン層22には、両者の表面を覆うようにゲート絶縁膜24が形成されている。ゲート絶縁膜24上には、ゲート絶縁膜24を介してチャネル領域22aに対向する位置にゲート電極層25が形成されている。ゲート絶縁膜24表面の一部には、キャパシタ上部電極層26が形成されている。

(もっと読む)

121 - 140 / 333

[ Back to top ]