Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

141 - 160 / 333

金属窒化物を乾式エッチングする方法及びシステム

【課題】チタン窒化物等の金属窒化物をエッチングする方法及びシステムについて開示している。

【解決手段】そのエッチングの処理は、Cl2、HBr又はBCl2等のハロゲン含有ガス、及び化学式CxHyFzを有するフルオロカーボンガスであって、x及びzは1に等しいか又は1より大きく、yは0に等しいか又は0より大きい、フルオロカーボンガスを有する処理成分を導入する段階を有する。

(もっと読む)

マグネトロンスパッタリング装置および半導体装置の製造方法

【課題】ウェーハ外周部のスルーホールやトレンチ内における被覆性を向上できるマグネトロンスパッタ装置および半導体装置の製造方法を提供する。

【解決手段】サセプタ3に接続された高周波電源8と、スパッタ室2の外側であって、ターゲットの中心軸C1と同軸のプレート9と、中心軸を中心Cにプレートを回転させる回転移動手段と、プレートの一面においてS極端をターゲットに向けたS極マグネット10Sと、プレートの一面においてN極端をターゲットに向けた第1及び第2のN極マグネット10Nと、を備え、第1のN極マグネットと第2のN極マグネットとの磁束密度がS極マグネットの磁束密度より大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】従来のCMISデバイスにおいては、価電子帯端近くの高い仕事関数を有する金属は、還元雰囲気アニール後に実効仕事関数が低下する。

【解決手段】半導体装置は、ソースとドレイン間のN型半導体層上に形成された金属元素を含むゲート絶縁膜と、ゲート絶縁膜上に形成され、膜厚が3nm以下であるカーボン層と、カーボン層上に形成されたゲート電極とを有し、ゲート電極/ゲート絶縁膜界面へのカーボン層による仕事関数の上昇効果により、還元雰囲気アニール耐性のない価電子帯端近くの高い仕事関数を有する金属を用いずとも、PMISFETに必要な実効仕事関数を得ることができ、低い閾値電圧を実現する。

(もっと読む)

MIS型半導体装置の製造方法およびMIS型半導体装置

【課題】微細化してもリーク電流の少ない、信頼性に優れたフルシリサイド化ゲート電極を備えたMIS型半導体装置の製造方法を提供することにある。

【解決手段】シリコン基板1上に、ゲート絶縁膜4及び多結晶シリコン膜5からなるゲート領域を形成した後、プラズマ窒化処理を行って、多結晶シリコン膜5の側面に窒素を導入する。その後、ゲート領域をマスクに、シリコン基板表面にソース、ドレイン領域10、11を形成した後、多結晶シリコン膜5上に金属膜14、17を形成し、然る後、多結晶シリコン膜5と金属膜14、17とをシリサイド化反応させて、多結晶シリコン膜5の全領域がフルシリサイド化されてなるゲート電極15、18を形成する。

(もっと読む)

CMOS半導体素子及びその製造方法

【課題】デュアルメタルゲートCMOS半導体素子を提供する。

【解決手段】金属窒化物層及び多結晶シリコンキャッピング層を備え、nMOS領域及びpMOS領域の金属窒化物層は同種物質で形成され、相異なる不純物含有量により相異なる仕事関数を持つデュアルメタルゲートCMOS半導体素子。同種の金属窒化物層によりメタルゲートを形成するので、工程が単純化して収率が向上すると共に、高性能のCMOS半導体素子を得ることができる。

(もっと読む)

半導体構造、複数のラインを形成する方法、および高密度構造と低密度構造を単一フォトマスクで形成する方法

いくつかの実施形態は、犠牲材料に沿ったポリマースペーサーの形成、犠牲材料の除去、および集積回路の製造中におけるマスクとしてのポリマースペーサーの利用、を含む。ポリマースペーサーマスクは、例えばフラッシュメモリアレイのフラッシュゲートをパターン化するために利用されてもよい。いくつかの実施形態では、ポリマーは大きな犠牲構造と小さな犠牲構造にわたって同時に形成される。ポリマーは、小さな犠牲構造にわたってよりも、大きな犠牲構造にわたっての方が厚く、こうした厚さの差を利用して、高密度構造と低密度構造を単一フォトマスクで製造する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極層の除去に伴うトランジスタの性能の低下を抑制すること。

【解決手段】第1及び第2導電型のトランジスタをそれぞれ基板上の第1及び第2領域に形成する半導体装置の製造方法であって、前記第1及び第2領域にわたってゲート絶縁膜と犠牲層とを堆積し、前記第1領域から前記犠牲層を除去し、前記第1領域に露出した前記ゲート絶縁膜上及び前記第2領域に残存する前記犠牲層上に第1のゲート電極層を堆積し、前記第2領域から前記第1のゲート電極層と前記犠牲層とを除去し、前記第2領域に露出した前記ゲート絶縁膜上に第2のゲート電極層を堆積し、前記ゲート絶縁膜と前記第1のゲート電極層とを含む前記第1導電型のトランジスタを形成し、前記ゲート絶縁膜と前記第2のゲート電極層とを含む前記第2導電型のトランジスタを形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法及び半導体装置の製造装置

【課題】メタルキャップ層の信頼性と生産性を向上させた半導体装置の製造方法及び半導体装置の製造装置を提供する。

【解決手段】第2層間絶縁膜と第1配線、あるいは、第2配線層とハードマスクをシリコン基板2の表面に形成し、そのシリコン基板2を反応室Sに搬送させ、その反応室Sに、マイクロ波によって励起されたN2ガスを導入する。そして、供給タンクTに収容されるZr(BH4)4をArガスによってバブリングし、Zr(BH4)4を含むArガスをZr(BH4)4ガスとして反応室Sに導入する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化されても良好な品質を有するゲート絶縁膜を備え、信頼性が高く、高速に動作可能な半導体装置およびその製造方法を提供する。

【構成】半導体装置は、半導体基板1001内に形成されたp型活性領域1003およびn型活性領域1004と、p型活性領域1003の上面に形成されたゲート絶縁膜1006と、上部におけるLaの濃度がその他の部分のLaの濃度よりも大きい第1の電極形成膜1015を含む第1のゲート電極とを有するp型MISFETとを備えている。さらに、n型活性領域1004の上面に形成されたゲート絶縁膜1006と、上部におけるAlの濃度がその他の部分のAlの濃度よりも大きい第2の電極形成膜1014を含む第2のゲート電極とを有するn型MISFETとを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホール内に形成される銅プラグの接合リークの増加を抑制し、銅プラグの良好なコンタクトを達成できる半導体装置の製造方法を提供することである。

【解決手段】シリサイド層32を有する半導体基板1の上に絶縁膜38を形成し、さらに、シリサイド層32上の絶縁膜38にホール38fを形成し、ホール38f内とシリサイド層32の表面をクリーニングし、ホール38fの底面及び内周面に化学気相成長法によりチタン層41を形成し、銅拡散防止用のバリア層42をホール38f内のチタン層41上に形成し、銅層44をホール38f内に埋め込む工程を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体基板とは格子定数の異なる半導体層からチャネル部に対して効果的に応力を印加することが可能でこれによりキャリア移動度の向上を図り高機能化の達成が可能な半導体装置を提供する。

【解決手段】半導体基板3上にゲート絶縁膜5を介して設けられたゲート電極7と、ゲート電極7の両脇において半導体基板3の表面を掘り下げた部分にエピタキシャル成長によって形成された半導体層(応力印加層)9とを備えた半導体装置1において、半導体層9は、半導体基板3とは格子定数の異なる層であり、ゲート絶縁膜5およびゲート電極7は、半導体層9間において半導体基板3の表面を掘り下げた部分を埋め込む状態で設けられている。半導体基板3の表面に対するゲート絶縁膜5の深さ位置d2は、半導体層9の深さ位置d1よりも浅いこととする。

(もっと読む)

半導体装置およびその製造方法

【課題】空乏化を生じず、また、製造工程における酸化、薬液による腐食、含有する金属による熱処理装置の汚染を抑えることのできるゲート電極を有し、且つトランジスタのオン電流の低下を抑えることのできる半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された金属含有層、並びに前記金属含有層の上面および側面を覆う不純物イオンを含んだ多結晶シリコン層からなるゲート電極と、を有する。

(もっと読む)

半導体素子及びその形成方法、半導体クラスタ装備

【課題】電気的な特性が向上される半導体素子の形成方法を提供する。

【解決手段】この方法は、導電パターン105を有する半導体基板100の上に絶縁膜110を形成する。絶縁膜をパターニングして導電パターンの一部を露出する開口部115を形成し、開口部の内壁及び絶縁膜の上部面に予備拡散防止膜120を形成する。予備拡散防止膜に酸素原子等を供給して第1拡散防止膜120aを形成する。第1拡散防止膜により囲まれている開口部を埋める金属膜152を形成する。この方法により製造された半導体素子及び半導体素子の製造に利用する半導体クラスタ装備を提供する。

(もっと読む)

原子層蒸着法を用いた薄膜形成方法

【課題】原子層蒸着法を用いた薄膜形成方法。

【解決手段】反応チャンバに金属元素及びリガンドを含む第1反応物を注入して基板上に第1反応物を化学吸着させ、不活性ガスでパージして物理吸着された第1反応物を除去し、水酸化基を含まない第2反応物を注入して第1反応物と第2反応物との化学反応によって、第2反応物の酸素と金属元素が結合し、第1反応物からリガンドを分離して化学吸着された第1反応物を金属−酸素原子層とし、不活性ガスでパージして物理吸着された第2反応物を除去し、第3反応物を注入して化学吸着された第1反応物の残余分と第3反応物との化学反応によって第3反応物の構成要素である酸素と金属元素が結合し、第1反応物からリガンドを分離することにより化学吸着された第1反応物の残余分を金属−酸素原子層として、水酸化基の生成が抑止された状態で原子層単位の金属酸化膜を形成する。

(もっと読む)

半導体装置用電極膜

【課題】スパイク発生を解消する電極膜を提供する。

【解決手段】裏面電極膜5は、コレクタ層31の表面に、密着層11と拡散防止層12とバリア層13と電極本体層14と親和層15とがこの順序で形成されており、親和層15は、低融点金属層16によってステージに接続される。密着層11はアルミニウム合金であり、拡散防止層12はTi,Zr,Hf,V,Nb,Ta,Cr,Mo,Ta,W,Coのうち、1種類を含む金属であり、電極本体層14はNi合金であり、バリア層13は拡散防止層12の金属の窒化物である。

(もっと読む)

多重拡散防止膜を備える半導体素子の製造方法

【課題】ゲートスタックのシート抵抗及びコンタクト抵抗が小さいながらも、不純物の外部拡散を効果的に抑制することのできる拡散防止膜を備える半導体素子の製造方法を提供すること。

【解決手段】本発明に係る半導体素子の製造方法は、第1導電層(21)上に、少なくとも第1金属膜(22A)および窒素含有の金属シリサイド膜(22C)を含む積層構造で拡散防止膜を形成するステップと、該拡散防止膜上に第2導電層(23)を形成するステップとを含む。

(もっと読む)

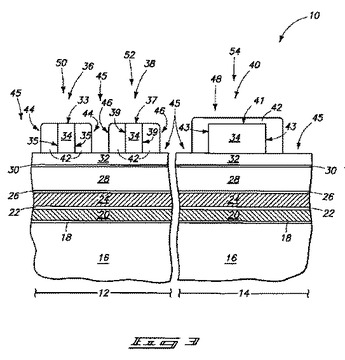

複数の誘電体を備えた半導体装置の製造方法

【課題】複数の誘電体を備えた半導体装置を製造するためのより良い方法を提供する。

【解決手段】基板200上に、第1制御電極誘電体材料202を設けること、基板200の少なくとも第1領域210aに、第1誘電体材料202を覆うパターン化した犠牲層を設けること、第1領域210aではパターン化した犠牲層を覆い、第2領域210bでは第1誘電体材料202を覆う第2誘電体材料203を設けること、但し、第2領域210bは、第1領域210aと異なっており、第2誘電体材料203をパターン化して、パターン化した第2誘電体材料が、第2領域210bでは第1誘電体材料202を覆い、第1領域210aではパターン化した犠牲層を覆わないようにすること、パターン化した犠牲層を除去することを含む。

(もっと読む)

多重拡散防止膜を備える半導体素子

【課題】ゲートスタックのシート抵抗及びコンタクト抵抗が小さいながらも、不純物の外部拡散を効果的に抑制することのできる拡散防止膜を備える半導体素子を提供すること。

【解決手段】第1導電層(211)と、第1導電層(211)上に形成され、且つ金属シリサイド膜(212A)及び窒素含有の金属膜(212B)の順に積層された第1拡散防止膜と、該第1拡散防止膜上の少なくとも窒素含有の金属シリサイド膜(212D)を含む第2拡散防止膜と、該第2拡散防止膜上の第2導電層(213)とを備える。

(もっと読む)

半導体装置

【課題】大画面化しても低消費電力、歩留まり及び信頼性の向上を実現するための半導体装置の構造及びその作製方法を提供する。

【解決手段】画面で使われる画素薄膜トランジスタを逆スタガ型薄膜トランジスタで作製する。その逆スタガ型薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と逆スタガ型薄膜トランジスタ、画素電極と逆スタガ型薄膜トランジスタをつなぐ金属配線を同一工程で作製する。

(もっと読む)

半導体装置の製造方法

【課題】p型MOSFETとn型MOSFETとの間で異なる所望のしきい値を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板上にHf、 Zrの少なくとも1つと、Si、O、Nを含むゲート絶縁膜を形成し、第1、第2のゲート電極層を形成し、第1のゲート電極層上および第2のゲート電極層上に、第1の金属含有層を形成し、第2の金属含有層を形成し、保護膜を形成し、保護膜を選択的に除去し、残存する保護膜をマスクとして、第1の金属含有層および第2の金属含有層を選択的に除去し、第1の金属含有層および第2の金属含有層が選択的に除去された第2のゲート電極層上に、第3の金属含有層を成膜し、加熱処理により、第1のゲート電極層を合金化するとともに、第2のゲート電極層を合金化し、異なる組成のゲート電極を形成する。

(もっと読む)

141 - 160 / 333

[ Back to top ]