Fターム[4M104BB29]の内容

Fターム[4M104BB29]の下位に属するFターム

Fターム[4M104BB29]に分類される特許

161 - 180 / 333

主電極を含むドープされた金属を含む半導体装置

【課題】良好な半導体装置およびそのような半導体装置を作製するための良好な方法を提供する。

【解決手段】半導体装置は、主電極(4)と主電極(4)に接触した誘電体(3)を含み、主電極(4)は、所定の仕事関数を有する材料と、主電極(4)の材料の仕事関数を予め決められた値に向かって変調する仕事関数変調元素(6)とを含み、更に、主電極(4)は、仕事関数変調元素(6)が誘電体(3)に向かっておよび/または誘電体(3)中に拡散するのを防止する拡散防止ドーパント元素(5)を含む。

(もっと読む)

半導体素子への金属含有膜の集積方法

【課題】 本発明は、半導体プロセスに関する。より具体的には、本発明は、化学気相成長法によって形成される金属含有膜を半導体素子に集積する方法に関する。

【解決手段】 たとえばゲートスタックのような、半導体素子中の金属含有膜を集積する方法。一の実施例では、当該方法は、処理チャンバ内に基板を供する手順、その基板をタングステンカルボニル含有ガスに曝露することによって、その基板上に、第1基板温度でタングステン含有膜を成膜する手順、第1基板温度よりも高温である第2基板温度でタングステン含有膜を熱処理することで、そのタングステン含有膜から一酸化炭素を除去する手順、及びその熱処理されたタングステン含有膜上にバリヤ層を形成する手順、を有する。タングステン含有膜の例には、W、WN、WSi、及びWCが含まれる。他の実施例は、Ni、Mo、Co、Rh、Re、Cr又はRuを含む金属含有膜を、各金属元素に対応した金属カルボニル先駆体から堆積する手順を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】 ダマシンゲート技術等を用いてゲート電極が作製される半導体装置において、半導体装置の微細化等を可能にする。

【解決手段】 N型MISトランジスタ及びP型MISトランジスタそれぞれのゲート電極が半導体基板に形成された凹部内にゲート絶縁膜を介して形成されている半導体装置であって、N型MISトランジスタ及びP型MISトランジスタの一方のゲート電極は第1の金属含有膜F1及び第1の金属含有膜上の第2の金属含有膜F2の積層構造によって構成され、N型MISトランジスタ及びP型MISトランジスタの他方のゲート電極は第3の金属含有膜F3及び第3の金属含有膜上の第2の金属含有膜F2の積層構造によって構成されている。

(もっと読む)

埋込み層に低抵抗コンタクトを形成する打込み領域を含んだ半導体デバイスの製作方法および関連したデバイス

半導体デバイスを製作する方法は、第1のドーパント濃度を有する第1の伝導型の第1の半導体層を形成すること、および第1の半導体層上に第2の半導体層を形成することを含む。第2の半導体層は、第1のドーパント濃度よりも低い第2のドーパント濃度を有する。第2の半導体層を貫通して延びて第1の半導体層に接触する第1の伝導型の打込み領域を形成するように、第2の半導体層中にイオンが打ち込まれる。第1の電極が第2の半導体層の打込み領域上に形成され、第2の電極が、第2の半導体層の非打込み領域上に形成される。関連したデバイスも述べられる。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】本発明では、酸素欠損を低減させ、信頼性を改善した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】第1の発明の半導体装置は、基板と、基板に形成された半導体領域と、半導体領域上に形成され、1種以上の第1金属元素の酸化物で形成された絶縁膜と、絶縁膜上に形成され、酸化物の生成自由エネルギーについて第1金属元素よりも大でありかつ金属状態である第2金属元素、および第1金属元素の酸化物で形成された遷移層と、遷移層上に形成された電極と、電極をゲート長方向に挟む半導体領域に形成されたソース・ドレイン領域とを備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】ランタンアルミニウム酸化物を絶縁膜として用いた半導体装置において、この絶縁膜に積層する電極として必要な特性を満たすと共に、各種半導体装置製造過程を経てもその絶縁膜特性を劣化させることのないゲート電極を見出し、微細化に対応可能なスタック構造を有する半導体装置を提供する。

【解決手段】本発明の一実施形態に係るCMOS回路は、nMISは、ランタンアルミニウム酸化物を用いたゲート絶縁膜19、LaxAl1−x(但し0.21≦x≦0.33)で表されるランタンアルミニウム合金を用いたゲート電極21、及びソース及びドレイン領域35とを具備し、pMISは、ランタンアルミニウム酸化物を用いたゲート絶縁膜19、LaxAl1−xNyHz(但し0.21≦x≦0.33、0.15≦y≦0.5、0≦z≦0.1)で表されるランタンアルミニウム合金を用いたゲート電極21を具備する。

(もっと読む)

有機金属前駆体化合物

本発明は、式(L1)yM(L2)z−y(ここで、Mは第5族金属又は第6族金属であり、L1は置換又は非置換アニオン性6電子供与体リガンドであり、L2は同じか異なり、かつ、(i)置換若しくは非置換アニオン性2電子供与体リガンド、(ii)置換若しくは非置換カチオン性2電子供与体リガンド、又は(iii)置換若しくは非置換中性2電子供与体リガンドであり、yは整数1であり、zはMの原子価であり、Mの酸化数とL1及びL2の電荷との合計は0に等しい)で表される有機金属化合物、有機金属化合物を製造する方法並びに有機金属前駆体化合物の熱的又はプラズマ強化解離により基体上に金属及び/又は金属炭化物/窒化物層を堆積する方法に関する。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】セル面積の縮小化とともに、シェアードコンタクト形成時のゲート電極側部に形成されたサイドウォールの膜減りによる半導体基板への突き抜けを防止する。

【解決手段】半導体基板上にゲート絶縁膜を介してゲート電極13が形成され、その両側にサイドウォール15,16が形成され、ゲート電極13両側の半導体基板にソース・ドレイン17,18が形成されている半導体基板上に、ゲート電極13、ソース・ドレイン17,18等を被覆する犠牲膜23を形成する工程と、犠牲膜23にゲート電極13上から一方側のソース・ドレイン18上を開口するシェアードコンタクト24を形成する工程と、シェアードコンタクト24の内部にゲート電極13と一方側のソース・ドレイン18に接続する導電性プラグ26を形成する工程と、犠牲膜23を除去する工程とを備えたことを特徴とする。

(もっと読む)

集積回路のメタライゼーションスキームにおけるバリア層のボトムレス堆積方法

【課題】デュアルダマシンメタライゼーションにおいて、Cu配線構造のバリア材料を絶縁層の表面上のみに選択的に形成し、接続構造部のエレクトロマイグレーションを抑制するとともに、下層導電層との接続抵抗を低減する選択的堆積方法を提供する。

【解決手段】Cu層20上の絶縁層14,15をエッチングしてトレンチとビアを開孔する。ビア底部のCu層の表面10に原子層成長(ALD)ブロック層を形成する。この後、原子層成長(ALD)法を用いてTiNバリア材料26を絶縁層表面12、13に堆積する。ブロック層により、ビア底部のCu層の表面にはバリアは形成されないため、ビア底部のCuは露出した状態のままである。開口部内にCu18を充填するとCu層に直接接続することが出来る。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の材料のメタルゲート電極をn型MOS領域およびp型MOS領域に用いて高精度で仕事関数を制御することができるCMOS型の半導体装置を提供すること。

【解決手段】半導体基板10の主面に形成されたnMOS領域37およびpMOS領域38を含むCMOS型の半導体装置であって、nMOS領域37は、WSi膜17を含むメタルゲート電極23を有し、pMOS領域38は、WSiN膜35を含むメタルゲート電極25を有し、WSiN膜35のN量を制御してその仕事関数を制御し、pMOS領域38におけるゲート電極25の閾値を制御する。

(もっと読む)

半導体装置の製造方法

【課題】素子が微細化されても優れたプロセス安定性を有し、かつシリサイドが形成された領域での抵抗増大を抑制する。

【解決手段】基板主表面側に絶縁膜によって区分されたシリコン領域を形成する工程と、このシリコン領域表面にシリコン酸化膜を形成する工程と、このシリコン酸化膜を形成した基板上に第1の金属及び第2の金属の混合膜を形成する工程と、熱処理によりシリコン領域に形成されたシリコン酸化膜を第2の金属によって還元する工程と、熱処理により第1の金属とシリコン領域のシリコンとを反応させてシリコン領域の表面にのみシリサイド膜を形成する工程とを有し、第1の金属はCo、Ni、Pt又はPdであり、第2の金属はTi、Zr、Hf、V、Nb、Ta又はCrである。

(もっと読む)

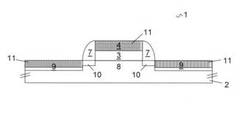

表示装置及びその製造方法

【課題】簡便な構成で、チャネル活性層として結晶性シリコン層を有する薄膜トランジスタの特性のバラツキを抑制した表示装置を提供する。

【解決手段】本発明の一態様に係る表示装置は、絶縁基板1上に形成されたポリシリコン層2と、絶縁基板1上に、ソース線を含み、ポリシリコン層2のソース領域2a及びドレイン領域2cの上に形成された配線層3と、ポリシリコン層2及び配線層3上に形成されたゲート絶縁層4と、ゲート絶縁層4上に形成され、ゲート線と、ポリシリコン層2のチャネル領域2bに対応して形成されたゲート電極5と、配線層3の一部に対応して形成されたキャパシタ電極6とを含むゲート電極層11と、ゲート電極層11上に形成された層間絶縁層7と、層間絶縁層7上に形成され、ゲート絶縁層4及び層間絶縁層7に設けられたコンタクトホール9を介してドレイン領域2cに接続された画素電極を含む画素電極層8とを備えるものである。

(もっと読む)

半導体発光装置および同装置の製造方法

【課題】II-Vグループ(またはII-IV-Vグループ)化合物接触層のある半導体発光装置および同装置の製造方法を提供する。

【解決手段】基板、第1伝導型半導体材料層、発光層、第1電極、第2伝導型半導体材料層、II-Vグループ(またはII-IV-Vグループ)化合物接触層、透明伝導層および第2電極が含まれ、II-Vグループ(またはII-IV-Vグループ)化合物接触層が存在することによって、第2伝導型半導体材料層および透明伝導層の間のオーム接触を改善する。

(もっと読む)

半導体装置の製造方法、半導体装置の製造装置、半導体装置及び記憶媒体

【課題】銅膜とその下地膜との密着性がよく、配線間の抵抗の小さな半導体装置の製造方法等を提供する。

【解決手段】大気中の水分を吸収した多孔質の絶縁層(SiOC膜11)にトレンチ100の形成された基板(ウエハW)を処理容器内に載置し、バルブメタルからなる第1の下地膜(Ti膜13)を被覆する。絶縁層から放出された水分により、絶縁層と接する第1の下地膜の表面が酸化されてパッシベーション膜13aが形成される。一方、第1の下地膜の表面をバルブメタルの窒化物または炭化物からなる第2の下地膜に被覆し、その表面に銅の有機化合物を原料とするCVDにより銅膜15を成膜する。

(もっと読む)

半導体発光素子

【課題】高出力及び高輝度、高寿命の半導体発光素子を提供する。

【解決手段】第1/第2導電型半導体層上に其々第1/第2電極を、同一面側に備えた半導体発光素子であり、第1電極は、第1台座部とこれを基点として同方向に延びる2以上の第1延伸部とを備え、第2電極は、第2台座部とこれから第1台座部に近づくように第1延伸部と略同方向に延びる第2延伸部とを備え、2以上の第1延伸部は、其々同方向部分に、第2電極における第1台座部から最も遠い端部を越えて素子外周方向に配置された終端部を有し、一方の第1延伸部は同方向部分に第1台座部が設けられ、他方の第1延伸部は同方向部分で、第1電極と第2電極との間隔が最短となるように配置され、第2延伸部は、他方の第1延伸部の同方向部分と第2台座部との最短間隔及び他方の第1延伸部の同方向部と第2延伸部との最短間隔が同じになるように第2台座部から延伸してなる半導体発光素子。

(もっと読む)

半導体構造

【課題】BTS試験の影響のない半導体構造を有する高電圧MOS素子を提供する。

【解決手段】高電圧MOS素子は、基板上に横たわった第1高電圧ウェル(HVW)領域24と、基板上に横たわった第2HVW領域26と、基板上に横たわり、第1・第2HVW領域の導電型とは反対の導電型となり、かつ、少なくとも一部が第1HVW領域と第2HVW領域との間に設けられる第3HVW領域28と、第1・第2・第3HVW領域の中に設けられた絶縁領域30と、第1HVW領域から第2HVW領域まで覆いかつ延伸するゲート誘電体と、ゲート誘電体上に設けられたゲート電極38と、絶縁領域上に設けられ、前記ゲート電極から電気的に絶縁された遮蔽パターン42と、を備える。ゲート電極と遮蔽パターンとの間隔は、好ましくは約0.4μm未満である。遮蔽パターンは、好ましくはゲート電極に印加されるストレス電圧よりも低い電圧に接続される。

(もっと読む)

半導体装置およびその製造方法

【課題】E―FETおよびD−FETのそれぞれに求められる特性を両立する。

【解決手段】本発明に係る半導体装置100は、半導体基板101上に形成されるチャネル層104と、チャネル層104上に形成される電子供給層105と、電子供給層105上に形成される第1のショットキー層107と、第1のショットキー層107上に形成される第2のショットキー層108と、第1のショットキー層107上に形成され、第1のショットキー層107とショットキー接合する第1のゲート電極114と、第1のゲート電極114を挟むように形成されるオーミック電極115cと、第2のショットキー層108上に形成され、第2のショットキー層108とショットキー接合し、第1のゲート電極114と異なる材料で形成される第2のゲート電極115aと、第2のゲート電極115aを挟むように形成されるオーミック電極115dとを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】CVD法により上部電極を成膜する際の下地層へのダメージを防止する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板11上の層間絶縁膜16に設けられた凹部17の内壁を覆う状態で、層間絶縁膜16上にゲート絶縁膜18を形成する工程と、ゲート絶縁膜18上に、仕事関数を制御する第1ゲート電極層19aを形成する第1工程と、第1ゲート電極層19a上に、下地層へのバリア性を有する第2ゲート電極層19bを形成する第2工程と、第2ゲート電極層19bが設けられた凹部17を埋め込む状態で、第2ゲート電極層19b上に、化学的気相成長法により、第1ゲート電極層19aよりも抵抗の低い第3ゲート電極層19cを形成する第3工程とを行うことを特徴とする半導体装置の製造方法と半導体装置である。

(もっと読む)

半導体デバイス

【課題】金属−絶縁物−半導体電界効果トランジスタの製造において、基板材料のバンドギャップの中間付近の仕事関数を有し、フッ素による問題を除去し、ボロンのしみ込みを防ぎ、また、複雑かつ余計な工程段階を使用することのない、ゲート電極を形成する。

【解決手段】金属半導体窒化ゲート電極(40、70)が、半導体デバイス(60)において使用するために形成される。ゲート電極(40、70)は、スパッタデポジション、低圧化学蒸着(LPCVD)またはプラズマエンハンスト化学蒸着(PECVD)により形成できる。その材料は、シリコン含有化合物の類をエッチングし、従来のハロゲン基エッチング化学物質にエッチングされる。金属半導体窒化ゲート電極(40、70)は、比較的安定であり、従来のゲート電極よりも比較的薄く形成できる。また、基板(12)の物質のバンドギャップの中間付近の仕事関数を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ビアホールを有する半導体装置及びその製造方法において、ビアホール内におけるバリア層の被覆不足防止とビア抵抗を制御することの両者を同時に達成することを目的とする。

【解決手段】その表面上にパッド電極3を有する半導体基板1を準備する。次に、半導体基板1の裏面から表面方向にエッチングし、パッド電極3を露出させるビアホール8を形成する。次に、スパッタリング法またはPVD法、及び逆スパッタリング(エッチング)によりビアホール8内に第1のバリア層11を形成する。この逆スパッタリングによりビアホール8底部のバリア層が除去され、パッド電極3が露出される。次に、ビアホール内で露出したパッド電極3上に第2のバリア層12を形成する。第2のバリア層12の膜厚のみを調節することでビア抵抗を制御する。

(もっと読む)

161 - 180 / 333

[ Back to top ]