Fターム[4M104BB32]の内容

Fターム[4M104BB32]に分類される特許

41 - 60 / 978

半導体装置及び発光装置

【課題】側壁スペーサを形成することなく、且つ、工程数を増やすことなく、自己整合的にLDD領域を少なくとも一つ備えたTFTを提供する。また、同一基板上に、工程数を増やすことなく、様々なTFT、例えば、チャネル形成領域の片側にLDD領域を有するTFTと、チャネル形成領域の両側にLDD領域を有するTFTとを形成する作製方法を提供する。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルをゲート電極形成用のフォトリソグラフィ工程に適用して膜厚の厚い領域と、該領域より膜厚の薄い領域を片側側部に有する非対称のレジストパターンを形成し、段差を有するゲート電極を形成し、ゲート電極の膜厚の薄い領域を通過させて前記半導体層に不純物元素を注入して、自己整合的にLDD領域を形成す

る。

(もっと読む)

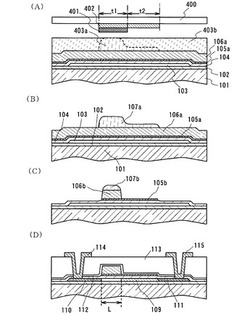

半導体装置及びその製造方法

【課題】ダミーゲート電極の除去により形成されたゲート溝へのゲート電極材料の埋め込み性を改善することにより、適切な閾値電圧を持つ電界効果型トランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】ゲート電極111bは、それぞれ金属又は導電性金属化合物からなる第1導電膜108b、第2導電膜109b及び第3導電膜110bが下から順に形成された積層構造を有し、ゲート電極111aは、第2導電膜109a及び第3導電膜110aが下から順に形成された積層構造を有する。第1導電膜108bの仕事関数と第2導電膜109a、109bの仕事関数とは異なっている。第1導電膜108bは板状に形成されており、第2導電膜109a、109bは凹形状に形成されている。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】メタルゲート電極とポリシリコン抵抗素子とを同じ半導体基板に混載するとともに、半導体装置の設計の自由度を向上し、また、半導体装置の小型化を図る。

【解決手段】半導体基板1の主面上にゲート絶縁膜を介してMISFET用のメタルゲート電極が形成され、また、半導体基板1の主面上に積層パターンLPを介してポリシリコン抵抗素子用のシリコン膜パターンSPが形成されている。メタルゲート電極は金属膜とその上のシリコン膜とを有し、積層パターンLPは絶縁膜3aとその上の金属膜4aとその上の絶縁膜5aとを有し、絶縁膜3aは、前記ゲート絶縁膜と同層の絶縁膜により形成され、金属膜4aはメタルゲート電極の金属膜と同層の金属膜により形成され、シリコン膜パターンSPは、メタルゲート電極のシリコン膜と同層のシリコン膜により形成されている。シリコン膜パターンSPは、平面視で絶縁膜5aに内包されている。

(もっと読む)

半導体装置およびその作製方法

【課題】In−Sn−Zn−O系半導体を用いた半導体装置を作製する際の加工技術を確立する。

【解決手段】Cl2または、BCl3または、SiCl4などの塩素を含むガスを用いたドライエッチングによりIn−Sn−Zn−O系半導体層を選択的にエッチングする。In−Sn−Zn−O系半導体層上に接して形成する導電層を選択的に除去してソース電極層及びドレイン電極層を形成する場合、塩素を含むガスに加えて酸素を含むガス、またはフッ素を含むガスを用い、In−Sn−Zn−O系半導体層がほとんど除去されないように導電層を選択的にエッチングすることができる。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】シリサイド層を有するトランジスタにおいて、オン電流の高いトランジスタを得ることを課題とする。さらに、加熱処理等の工程を増やさずにオン電流の高いトランジスタを得ることを課題とする。

【解決手段】チャネル形成領域、不純物領域及びシリサイド層を有するシリコン膜と、ゲート絶縁膜と、ゲート電極と、不純物領域にシリサイド層を介して電気的に接続する配線とを有し、シリサイド層断面は、チャネル形成領域側の端点から膜厚が増加している第1領域と、第1領域と比べて膜厚が一定である第2領域とを有する半導体装置において、第1領域と第2領域は、シリサイド層断面の端点を通り、水平線とθ(0°<θ<45°)の角度をなす直線がシリサイド層と不純物領域の界面と交わる点を通り、且つ水平線に対し垂直な線で分けられ、シリコン膜の膜厚に対する第2領域の膜厚比は0.6以上である。

(もっと読む)

半導体装置の作製方法

【課題】高い電界効果移動度を有し、しきい値電圧のばらつきが小さく、かつ高い信頼性を有する酸化物半導体を用いたトランジスタを提供する。また、該トランジスタを用い、これまで実現が困難であった高性能の半導体装置を提供する。

【解決手段】トランジスタに、インジウム、スズ、亜鉛およびアルミニウムから選ばれた二種以上、好ましくは三種以上の元素を含む酸化物半導体膜を用いる。該酸化物半導体膜は、基板加熱しつつ成膜する。また、トランジスタの作製工程において、近接の絶縁膜または/およびイオン注入により酸化物半導体膜へ酸素が供給され、キャリア発生源となる酸素欠損を限りなく低減する。また、トランジスタの作製工程において、酸化物半導体膜を高純度化し、水素濃度を極めて低くする。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

表示装置

【課題】信頼性の高い表示装置を提供する。

【解決手段】酸化物半導体を有するトランジスタを有し、酸化物半導体の下に設けられた絶縁膜と、酸化物半導体の上に設けられた絶縁膜とを有する。平坦性を持たせるため、有機材料を含む絶縁膜をさらに設ける。シール材は、有機材料を含む絶縁膜と重なることはなく、絶縁膜と接している。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体基板の製造方法

【課題】サイドエッチ発生の可能性を軽減させた半導体基板の製造方法を提供する。

【解決手段】絶縁膜の形成後、シード膜の形成の前に配線パターンの形成を行う。次いで、シード膜の形成後、配線パターン用レジストの剥離を行う。次いで、メッキマスクレジストの形成を行なったのち、半導体基板の表面からのメッキ電流により、ウエットエッチング工法を行うこと無く、配線パターンの形成を行う。

(もっと読む)

半導体電極構造

【課題】半導体装置の製造工程で高温下に曝された場合であっても、ヒロックの発生が抑制されて耐熱性に優れ、かつ膜自体の電気抵抗率が低く抑えられたAl合金膜を有する半導体電極構造を提供する。

【解決手段】基板上に少なくとも、基板側から順に、高融点金属の窒化物薄膜と、Al合金膜とを備えた半導体電極構造であって、前記Al合金膜は、500℃で30分間保持する加熱処理を行った後に下記(a)〜(c)を全て満たし、かつ膜厚が300nm〜5μmであることを特徴とする半導体電極構造。(a)Alマトリックスの最大粒径が1μm以下(b)ヒロック密度が1×109個/m2未満(c)電気抵抗率が10μΩcm以下

(もっと読む)

二重仕事関数金属ゲート構造体及びその製造方法

【課題】二重金属ゲートを有する構造体において金属膜の仕事関数を調整する為の改善した方法および半導体素子を提供する。

【解決手段】半導体素子は単一金属膜に対し、NMOSにおいてはフッ素、PMOSにおいては炭素をそれぞれ選択的にドーピングすることによって形成される二重仕事関数の金属ゲート電極108’、109’を有する。

(もっと読む)

無電解薄膜析出法により平坦化銅相互接続層を形成する方法および装置

【課題】基板に定形された形態部の内部に、表面が平坦化された導電性材料を形成する方法を提供する。

【解決手段】平坦化表面を形成する方法であって、狭小形態部と幅広形態部が形成された基板上に、第1のプロセスでは電気めっき法により狭小形態部および幅広形態部の少なくとも一部を充填し、第1の層を形成し、第2のプロセスでは無電解めっき法により幅広形態部のに対応する第1の層中の孔および第1の層上に第2の層を充填形成し、表面が平坦な上層部110を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】さらなる微細化に対しても適正な閾値電圧Vtが得られるデュアルメタルゲート構造を実現する。

【解決手段】ゲート電極120bは、第1の仕事関数を有する第1の金属含有膜114bと、第1の金属含有膜114b上に形成されており且つ第2の仕事関数を有する第2の金属含有膜117bとを含む。ゲート電極120aは、第1の金属含有膜114を含まないと共に第2の金属含有膜117aを含む。ゲート電極120bにおける第1の金属含有膜114bと第2の金属含有膜117bとの間に拡散防止層115bが形成されている。

(もっと読む)

複数の開口部を備える基板上への層の蒸着方法

【課題】多孔性低誘電率絶縁膜のトレンチおよびビア内にカバレージ良くライニング層を形成する半導体装置の製造方法を提供する。

【解決手段】第1パルス期間に供給される第1反応物と、第2パルス期間に供給される第2反応物とを利用する原子層堆積(ALD)プロセスにより成膜する。まずシーリング層を低コンフォマリティーを有する条件で成膜し、ポアをブロックする。この後、接着層を高いコンフォマリティーを有する条件で成膜する。

(もっと読む)

41 - 60 / 978

[ Back to top ]