Fターム[4M104BB34]の内容

Fターム[4M104BB34]に分類される特許

201 - 220 / 257

埋没接点を有するトランジスタとその形成方法

第1の電流電極領域(32)、第2の電流電極領域(34)、およびチャネル領域(37)を含む半導体構造の形成方法であって、チャネル領域(37)は第1の電流電極領域(32)と第2の電流電極領域(34)との間に配置され、チャネル領域(37)は半導体構造のフィン構造(36)内に配置され、チャネル領域内のキャリア輸送は概して第1の電流電極領域(32)と第2の電流電極領域(34)との間で水平方向に行われる方法。該方法は、第1の接点(66)を形成することを含み、第1の接点(66)を形成することは、半導体構造の第1の部分を除去して、第1の電流電極領域(32)に開口部(54)を形成すること、開口部に接点材料(66)を形成することを含む。  (もっと読む)

(もっと読む)

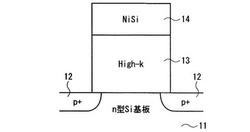

不揮発性半導体メモリ装置

【課題】

駆動電圧を低下させても、書き込み/消去動作後の電荷保持状態での電荷デトラップによる閾値電圧変動を抑制させることによって書き込み/消去、読み出し、および記憶保持において十分な性能を有し信頼性の高い不揮発性半導体メモリ装置を提供すること。

【解決手段】

本発明は、n型半導体領域11に設けられたp型ソース・ドレイン領域12と、前記p型ソース・ドレイン領域間12に設けられた高誘電率材料の電荷蓄積層13と、前記電荷蓄積層13上に設けられた、n型Si、金属系導電性材料及び、SiとGeの少なくとも一方を含むp型半導体材料から選択される制御ゲート電極14とを具備することを特徴とする不揮発性半導体メモリ装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】好適な特性を有するゲート絶縁膜及びゲート電極からなるP型FET及びN型FETを備える半導体装置を提供する。

【解決手段】P型FET形成予定領域とN型FET形成予定領域とにわたって、基板上にゲート絶縁膜を形成し、ゲート絶縁膜上にP型FET用のゲート電極層を形成し、P型FET形成予定領域とN型FET形成予定領域とにおいて、P型FET用のゲート電極層を加工することにより、P型FET形成予定領域にP型FET用のゲート電極を形成すると共に、N型FET形成予定領域にダミーゲート電極を形成し、N型FET形成予定領域において、ゲート絶縁膜上からダミーゲート電極を除去することにより、溝を形成し、溝にゲート電極材料を埋め込むことにより、ゲート絶縁膜上にN型FET用のゲート電極を形成することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】導電性が良好でありながらも銅の拡散を十分に防止することが可能な銅配線の埋め込み構造を備えた半導体装置およびその製造方法を提供する。

【解決手段】第1絶縁膜13に形成された配線溝13a内、第2絶縁膜22および第3絶縁膜に形成された配線溝24aと接続孔22a内に、拡散防止層15,25を介して銅配線17a,26aが埋め込まれた半導体装置27において、拡散防止層15,25は、ルテニウムカーバイト(RuCx)、ルテニウムシリサイド(RuSix)、またはルテニウム合金(RuTa)を用いて構成されたことを特徴とする。

(もっと読む)

電解めっき装置及び電解めっき方法

【課題】銅と同等以上の抵抗率の導電層(シード層)を有した基板に対して、より均一な膜厚で、全面に亘って膜質の良好なめっき膜を成膜できるようにする。

【解決手段】基板保持部で保持した基板表面の周縁部に当接して該周縁部をシールするシール材90と、基板保持部で保持した基板の表面に形成した導電層に接触して通電させるカソード接点88と、内部にめっき液に浸漬させるアノード98を収納し、基板保持部で保持した基板と対向する開口端部に多孔質構造体110を配置してめっき液室100を区画形成したハウジング94を有し、めっき液室100は仕切り板150で複数の部屋154a,154bに仕切られ、アノード98は複数に分割された分割アノード98a,98bから構成されて、各分割アノード98a,98bはめっき液室100の各部屋154a,154bの内部に独立しためっき電流が流せるように配置されている。

(もっと読む)

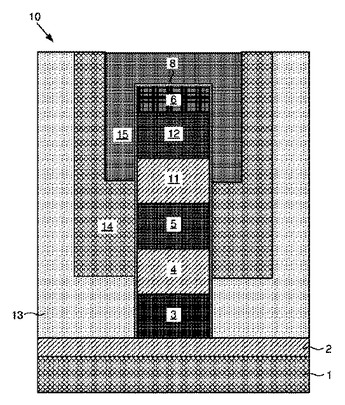

半導体装置およびその製造方法

【課題】ゲート絶縁膜に高誘電率膜を使用し、ゲート電極に金属を含む導体膜を使用するpチャネル型MISFETにおいて、生産性向上を図ることができる技術を提供することにある。そして、金属を含む導体膜の仕事関数値が酸化シリコン膜に接するとした場合にシリコンの価電子帯近傍の値から離れたものであっても、pチャネル型MISFETのしきい値電圧を下げることができる技術を提供する。

【解決手段】半導体基板1上に形成されたpチャネル型MISFETQ1は、酸化ハフニウム膜よりなるゲート絶縁膜10を有し、このゲート絶縁膜10上に、酸化アルミニウム膜よりなる金属酸化物膜11を有する。そして、金属酸化物膜11上に窒化タンタル膜よりなるゲート電極12を有している。ここで、金属酸化物膜11は、ゲート電極12の仕事関数値をシフトする機能を有している。

(もっと読む)

低エネルギープラズマシステムを用いた高誘電率トランジスタゲートを製造するための方法及び装置

本発明は、一般的には、基板上に高品質誘電体ゲート層を形成するように適合されている方法及び装置を提供する。実施形態は、標準窒化プロセスの代わりに金属プラズマ処理プロセスを用いて、基板上に高誘電率層を形成する方法を企図するものである。実施形態は、更に、二酸化シリコンのようなゲート誘電体層に対するイオン衝撃損傷を減少させるとともに金属原子の下に横たわるシリコンへの混入を避けるために比較的低エネルギーの金属イオンを“注入”するように適合された装置を企図するものである。一般に、プロセスには、高k誘電体を形成するステップと、次に、堆積された物質を処理して、ゲート電極と高k誘電物質との間の良好な接合部を形成するステップとを含む。実施形態は、また、高k誘電物質を形成し、高k誘電物質の表面を終了させ、望ましい後処理ステップを行い、ゲート層を形成するように適合されているクラスタツールを提供するものである。 (もっと読む)

半導体デバイスの製造において直接銅めっきし、かつ充填して相互配線を形成するための方法及び組成物

【課題】半導体デバイスの製造において直接銅めっきし、かつ充填して相互配線を形成するための方法及び組成物の提供。

【解決手段】本発明は、半導体デバイスの製造において直接銅めっきし、かつ充填して相互配線を形成するための方法及び組成物を目的としている。本発明によれば、上記方法とは、銅イオン源を45〜200mM、好ましくは45〜100mMの濃度で、及び2〜4つのアミン官能基を有する脂肪族ポリアミンである少なくとも1種の銅錯化剤を30〜200mM、好ましくは60〜200mMの濃度で溶媒中の溶液に含有し;かつ上記銅/錯化剤のモル比が0.2〜2、好ましくは0.3〜1.5である銅電解槽を調製し、基板の銅拡散バリア層を上記銅電解槽に接触させ、上記基板に、銅が電気めっきされる厚みに従い調整された時間中、電気的バイアスを印加し、上記基板を上記銅電解槽から取り出す方法である。

(もっと読む)

半導体装置の製造方法

【課題】P型MOSFETの閾値のバラつきを抑制して高品質の半導体装置を形成することができ、また、製品開発のコストを抑制することができる半導体装置の製造方法を提供する。

【解決手段】シリコン基板上100にゲート絶縁膜102を形成する第1の工程と、ゲート絶縁膜102上に、ゲート電極104を構成する導電体膜103を、有機材料を用いた形成法によって形成する第2の工程と、導電体膜103が形成されたシリコン基板100を、酸化性雰囲気である水蒸気と、還元性雰囲気である水素との混合雰囲気中で加熱する第3の工程と、を備えた半導体装置の製造方法であって、第3の工程における水蒸気に対する水素の分圧比が、炭素が酸化され、かつ、導電体膜104を構成する金属材料が還元される分圧であることを特徴とする。

(もっと読む)

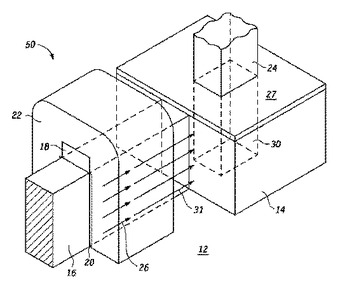

MOSデバイスおよびMOSデバイスの製造方法

本発明は、多数の積重された半導体領域を有する突起部またはフィン構造を備える三次元積層フィン型金属酸化物半導体(SF−MOS)デバイスを提供するもので、第2半導体領域が分離領域によって第1半導体領域から分離されている。ゲート分離層が少なくとも突起部の側壁に延在し、ゲート電極がゲート分離層に延在する。ゲート電極は複数のゲート領域を備え、各ゲート領域が他の半導体領域にわたって延在する。これにより、各ゲート領域が他の半導体領域の伝導チャネルに影響を与え、その結果SF−MOSデバイスの性能を最適化し得る他の自由度を付加する。本発明は、さらに本発明に係るSF−MOSデバイスを製造する方法を提供する。  (もっと読む)

(もっと読む)

熱およびプラズマ増強蒸着のための装置および操作方法

【課題】 熱およびプラズマ増強蒸着のための装置および操作方法を提供することである。

【解決手段】 第1の温度で蒸着システムの第1のアセンブリを維持し、第1の温度より低く低下された温度で蒸着システムの第2のアセンブリを維持し、基板を第2のアセンブリの移送空間から真空アイソレートされる第1のアセンブリの処理空間に配置し、基板上に材料を堆積させる、基板上の蒸着のための方法、コンピュータ読み取り可能なメディア、および、システムである。

(もっと読む)

半導体装置

【課題】 本発明は、適切な仕事関数を有する半導体装置を提供することを目的とする。

【解決手段】 第1の発明の半導体装置は、基板と、基板に形成されたN型半導体層とN型半導体層上に形成された第1ゲート絶縁層と第1ゲート絶縁層上に形成され膜厚が1nm以上5nm以下でありTaの炭化物を有する第1下層ゲート電極と第1下層ゲート電極上に形成され真空仕事関数が4.6eV以上5.2eV以下の金属珪化物を有する第1上層ゲート電極とを有するP型MISFETと、基板に形成されたP型半導体層とP型半導体層上に形成された第2ゲート絶縁層と第2ゲート絶縁層上に形成され膜厚が1nm以上5nm以下でありTaの炭化物を有する第2下層ゲート電極と第2下層ゲート電極上に形成され、真空仕事関数が4.0eV以上4.5eV以下の金属珪化物を有する第2上層ゲート電極とを有するN型MISFETと、を具備することを特徴とする。

(もっと読む)

原子層成長及び化学気相成長による薄膜形成方法

【課題】原子層成長と気相化学成長を連続して同一の反応装置に実行することにより、従来できなかった高品質膜を形成する。

【解決手段】上部室と、上部室の下側に配置され、シャワーヘッドの軸方向に見て上部室により覆われ、かつ上部室とガス連通しない下部室とを含むシャワーヘッドを使って、基板上に薄膜を形成する方法は、原子層成長(ALD)膜及び化学気相成長(CVD)膜を連続して形成するか、または熱ALD膜及びプラズマALD膜を連続して形成する工程を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造方法が容易なデュアルメタルゲート構造を実現することができ、CMOSデバイス等の特性向上に寄与する。

【解決手段】 基板上に、pチャネルMISトランジスタ51とnチャネルMISトランジスタ52を具備した半導体装置であって、pチャネルMISトランジスタ51のゲート電極32の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は80%以上であり、nチャネルMISトランジスタ52のゲート電極53の膜厚方向に対するTaC(111)面の結晶配向比率[TaC(111)面/{TaC(111)面+TaC(200)面}]は60%以下である。

(もっと読む)

熱およびプラズマ増強蒸着のための装置および操作方法

【課題】 熱およびプラズマ増強蒸着のための装置および操作方法を提供することである。

【解決手段】 基板上の蒸着のための方法、コンピュータ読み取り可能なメディアおよびシステムであって、処理システムの移送空間から真空アイソレーションされた処理システムの処理空間に基板を配置し、移送空間から真空アイソレートが維持されている間、処理空間の第1の位置または第2の位置のいずれかで基板を処理し、前記第1の位置または第2の位置のいずれかで前記基板に材料を堆積させる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを用いた半導体装置の製造方法において、RPTの短縮、ゲート寸法の加工精度の向上を図る半導体装置の製造方法を提供する。

【解決手段】半導体基板上にダミーゲートを形成する工程、前記ダミーゲートをマスクとして前記半導体基板に不純物を導入して、ソース・ドレイン拡散領域を形成する工程、前記ダミーゲートの周囲に絶縁膜を形成する工程、前記ダミーゲートを除去して開口部を形成する工程、及び前記開口部にゲート絶縁膜を介してゲート電極を形成する工程を具備する方法である。前記ダミーゲートは、前記半導体基板上に、炭素と水素との原子比(C/H)が1以上であり、かつ炭素の絶対量が50%以上である炭素過剰の組成のポリマーを塗布してポリマー膜を形成する工程、前記ポリマー膜上にフォトレジストパターンを形成する工程、及び前記フォトレジストパターンを前記ポリマー膜に転写する工程により形成されることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】シリコンCMOSデバイス等におけるシングルメタルゲート構造を実現することができ、デバイス特性揺らぎの低減及び高信頼化をはかる。

【解決手段】基板上に、pチャネルMISトランジスタ41とnチャネルMISトランジスタ42を備えた半導体装置であって、pチャネルMISトランジスタ41とnチャネルMISトランジスタ42の各ゲート電極32はTaとCの合金で形成され、ゲート電極32のTaに対するCのモル比(C/Ta)が2以上4以下である。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲート電極をメタルの凝集なく仕事関数変調により形成する。

【解決手段】本発明の例に関わる半導体装置の製造方法は、半導体基板100上にゲート絶縁層102を形成する工程と、ゲート絶縁層102上に第1メタル層103を形成する工程と、第1メタル層103上に第2メタル層104を形成する工程と、第2メタル層104上に第2メタル層104よりも高い融点を持つ材料からなるキャップ層105を形成する工程と、熱処理により第2メタル層104内の元素をゲート絶縁層102と第1メタル層103との界面に析出させて析出層107を形成する工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 nMISおよびpMIS形成領域の高誘電率ゲート絶縁膜上に設けられたデュアルメタルゲート電極の仕事関数の変化を抑制して、信頼性の高い半導体装置を製造する方法を提供する。

【解決手段】 単結晶シリコン基板100のnMISおよびpMIS形成領域に高誘電率ゲート絶縁膜102を形成し、ゲート絶縁膜102上にシリコンおよびゲルマニウムを含まない第一の金属膜103を形成し、pMIS形成領域のゲート絶縁膜上に第一の金属膜103を残して、nMIS形成領域の第一の金属膜103を除去する。次に、nMIS形成領域のゲート絶縁膜102および第一の金属膜103上にシリコンまたはゲルマニウムを含む第二の金属膜104を形成し、第一および第二の金属膜103、104を加工してゲート電極Gn、Gpをそれぞれ形成する。また、第一の金属膜103と第二の金属膜104に含まれる主の金属元素は周期律表における同族金属元素とする。

(もっと読む)

電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法

【課題】絶縁破壊電界が高く、熱伝導率が極めて良好で放熱性に優れ、化学的にも安定であり、またバンドギャップが大きいというダイヤモンド半導体の特性を最大限に活用するために、ダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス及びその製造方法を提供する。

【解決手段】半導体ダイヤモンドの表面と電極の表面が同一面となるように、半導体ダイヤモンドに設けた溝に電極が埋め込まれた構造を有することを特徴とするダイヤモンドデバイスの電界集中による電極の破壊電圧を抑制するためのダイヤモンド電極構造を備えたデバイス。

(もっと読む)

201 - 220 / 257

[ Back to top ]