Fターム[4M104BB34]の内容

Fターム[4M104BB34]に分類される特許

241 - 257 / 257

金属ゲート電極半導体デバイス

高誘電率ゲート誘電体を有するNMOS及びPMOSトランジスタを含む相補型金属酸化物半導体集積回路が半導体基板上に形成される。ゲート誘電体上に金属障壁層が形成される。金属障壁層上に仕事関数設定金属層が形成され、仕事関数設定金属層上にキャップ金属層が形成される。  (もっと読む)

(もっと読む)

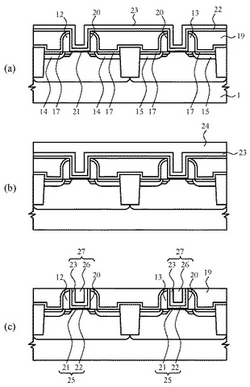

MIS型FETの製造方法

【課題】 ダマシン構造のゲート電極を備えたMIS型FETにおいて、高い電流駆動能力と低消費電力とを有するMIS型FETの製造方法を提供する。

【解決手段】 シリコン基板1の表面部にソース/ドレイン拡散層(14,15)を形成し、その表面にシリサイド層17を形成する。そして、ゲート側壁(12,13)で区画されたゲート開口溝20底部のシリコン基板1表面に、550℃以下の温度で界面層21を形成し、ゲート開口溝20内、界面層21および層間絶縁膜19を被覆するようにHigh−k膜22を堆積させ、酸化性雰囲気中550℃以下の温度での熱処理を施す。そして、全面を被覆する導電体膜23およびメタル膜24を形成した後、CMP法により層間絶縁膜19上の不要部分を研磨除去しダマシン構造のメタルゲート電極を備えたMIS型FETを形成する。

(もっと読む)

半導体装置及びかかる半導体装置の製造方法

本発明は、金属及び更なる元素の両方を含有する化合物を含むゲート領域(1D、2D)を有するNMOST1及びPMOST2を備えるCMOSデバイス(10)に関する。本発明によれば、第1及び第2導電材料はいずれも、モリブデン及びタングステンを含むグループから選択される金属を前記金属として含む化合物を備えると共に、炭素、酸素、カルコゲナイドを含むグループから選択される元素を前記更なる元素として含んでいる。第1及び第2導電材料はいずれも、モリブデン及び炭素または酸素から成る化合物を含むことが好ましい。また本発明は、かかるデバイスを製造する魅力的な方法も提供する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【目的】 点欠陥の集合によるボイドがCu配線内に形成しないようにすることを目的とする。

【構成】 基体上に絶縁膜を形成する絶縁膜形成工程(S102〜S110)と、前記絶縁膜に開口部を形成する開口部形成工程(S112)と、前記絶縁膜表面と前記開口部とにシード膜を形成するシード膜形成工程(S116)と、前記シード膜を電極として第1の電流密度となる電流を流し、前記開口部に導電性材料をめっき法により堆積させる第1のめっき工程(S118)と、前記第1のめっき工程後、前記第1の電流密度より小さい第2の電流密度となる電流を流し、前記絶縁膜表面上に前記導電性材料をめっき法により堆積させる第2のめっき工程(S120)と、前記第2のめっき工程後、前記導電性材料が堆積した基体をアニール処理するアニール工程(S124)と、を備えたことを特徴とする。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

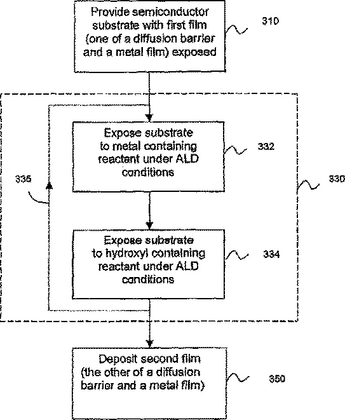

酸素架橋構造及び方法

拡散バリア膜と金属膜との間の接着性を改善するための方法が提唱される。拡散バリア膜及び金属膜の両方は、いずれかのシークエンスで、半導体基板上へ堆積される。拡散バリア膜又は金属膜のいずれか一方である第一膜(第一膜は、基板の表面領域の少なくとも一部で暴露される)を有する基板は、酸素含有リアクタントに暴露され、第一膜の露出部分に酸素含有基又は酸素原子の約1の単層の表面終端を生成する。次いで、第二膜(これは、拡散バリア膜及び金属膜のうち他方である)が基板上に堆積される。さらに、酸素架橋構造が提唱され、該構造は、拡散バリア膜及び該拡散バリア膜との界面を有する金属膜を含む(ここで、界面は、酸素原子の単層を含有する)。

【課題】

【解決手段】  (もっと読む)

(もっと読む)

原子層蒸着による銅フィルムの蒸着のための銅(II)錯体

本発明は、新規な1,3−ジイミンおよび1,3−ジイミン銅錯体ならびに原子層蒸着法における基材上または多孔性固体中もしくは多孔性固体上での銅の蒸着のための1,3−ジイミン銅錯体の使用に関する。 (もっと読む)

原子層蒸着による銅フィルムの蒸着のための銅(II)錯体

本発明は、新規な1,3−ジイミン銅錯体および原子層蒸着法における基材上または多孔性固体中もしくは多孔性固体上での銅の蒸着のための1,3−ジイミン銅錯体の使用に関する。 (もっと読む)

半導体装置及びその製造方法

【課題】 機械的強度に優れると共に、低抵抗であって且つ絶縁膜に対する密着性の高いバリアメタル膜を有する半導体装置を提供する。

【解決手段】 基板(1)上に形成された絶縁膜(6)と、絶縁膜(6)中に形成された埋め込み金属配線(10)と、絶縁膜(6)と金属配線(10)との間に形成されたバリアメタル膜(A1)とを備えた半導体装置において、バリアメタル膜(A1)は、絶縁膜(6)が存在している側から金属配線(10)が存在している側へ向かって順に積層されている金属酸化物膜(7)、金属化合物膜(8)及び金属膜(9)よりなる。金属化合物膜(8)の弾性率は、金属酸化物膜(7)の弾性率よりも大きい。

(もっと読む)

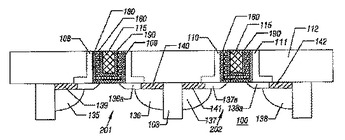

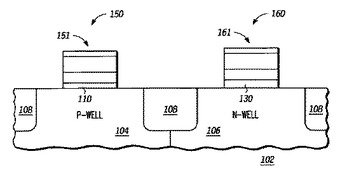

2種類の金属酸化物ゲート誘電体に1種類の金属ゲート電極が設けられる半導体プロセス及び集積回路

半導体形成プロセスでは、第1及び第2トランジスタを第1及び第2ウェル領域のそれぞれの上に形成し、第1トランジスタは第1ゲート誘電体を有し、そして第2トランジスタは第1ゲート誘電体とは異なる第2ゲート誘電体を有する。第1トランジスタは第1ゲート電極を有し、そして第2トランジスタは第2ゲート電極を有する。第1及び第2ゲート電極は組成が同じである。第1ゲート誘電体及び第2ゲート誘電体は共に、酸化ハフニウム及び酸化アルミニウムのような高k誘電体を含むことができる。第1及び第2ゲート電極は共に、ゲート電極層を該当するゲート誘電体の上に含む。ゲート電極層は、TaSiN及びTaCのいずれかであることが好ましい。第1及び第2ゲート電極は共に、導電層をゲート電極層の上に含むことができる。このような一の実施形態では、導電層はポリシリコン及びタングステンからなる。  (もっと読む)

(もっと読む)

金属からなるゲート電極を形成するための方法

一の実施形態では、ゲート誘電体層(18)を基板(10)の上に形成し、次に第1金属層(26)を、ゲート誘電体層(18)の内、第1素子タイプが形成される予定の部分の上に選択的に堆積させる。第1金属層(26)とは異なる第2金属層(28)は、ゲート誘電体層(18)の内、第2素子タイプが形成される予定の露出部分の上に選択的に形成される。第1及び第2素子タイプの各々は異なる仕事関数を有することになる、というのは、第1及び第2素子タイプの各々が、ゲート誘電体と直接コンタクトする異なる金属を含むことになるからである。一の実施形態では、第1金属層(26)の選択的堆積は、ALDにより、かつ阻止層(24)を使用することにより行なわれ、阻止層は、第1金属層(26)を、ゲート誘電体層(18)の内、阻止層(24)によって覆われない部分の上にのみ選択的に堆積させることができるようにゲート誘電体層(18)の上に選択的に形成される。 (もっと読む)

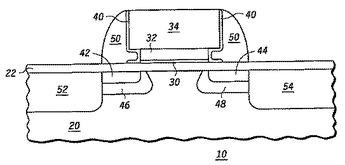

切り欠き制御電極及び当該電極の構造を有する半導体素子の製造方法

半導体素子(10)を形成する方法では、一の表面を有する基板(20)を設け、絶縁層(22)を基板(20)の表面の上に形成し、第1パターニング済み導電層(30)を絶縁層(22)の上に形成し、第2パターニング済み導電層(32)を第1パターニング済み導電層(30)の上に形成し、パターニング済み非絶縁層(34)を第2パターニング済み導電層(32)の上に形成し、そして第1及び第2パターニング済み導電層(30,32)の一部分を選択的に除去して、半導体素子(10)の切り欠き制御電極を形成する。  (もっと読む)

(もっと読む)

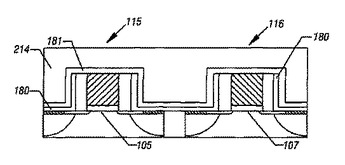

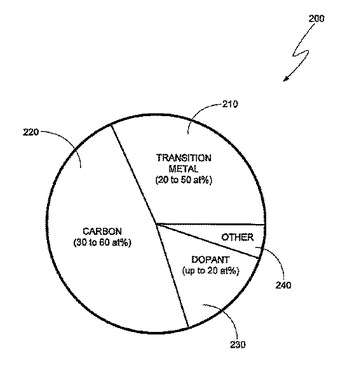

半導体構造、二重仕事関数のCMOSデバイス、二重仕事関数のCMOS回路、および基板上に二重仕事関数のCMOSデバイスを形成する方法(炭化金属ゲート構造および形成方法)

【課題】 炭化金属を含むゲート電極を含む少なくとも1つのFETを含む相補型金属酸化膜半導体(CMOS)などの半導体デバイスおよび形成方法を提供することにある。

【解決手段】 このCMOSは、ある金属とある金属の炭化物によって二重仕事関数が与えられる、二重仕事関数の金属ゲート電極を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

ソース/ドレイン領域の少なくともその幅が最も大きい部分では半導体領域の幅よりも大きく、かつソース/ドレイン領域の最上部側から基体側に向かって連続的に幅が大きくなっている傾斜部を有し、該傾斜部表面にシリサイド膜が形成されていることを特徴とする半導体装置とする。  (もっと読む)

(もっと読む)

ゲート電極として使用される遷移金属合金およびこれらの合金を取り入れた装置

高温で顕著に変化しないn型またはp型の仕事関数を有する遷移金属合金の実施例を示した。示された遷移金属合金は、トランジスタのゲート電極として使用しても良く、ゲート電極の一部を構成しても良い。これらの遷移金属合金を用いて、ゲート電極を形成する方法についても示した。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

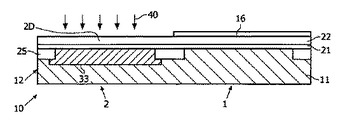

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

241 - 257 / 257

[ Back to top ]