Fターム[4M104BB34]の内容

Fターム[4M104BB34]に分類される特許

21 - 40 / 257

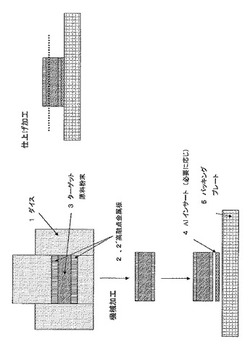

高融点金属合金、高融点金属珪化物、高融点金属炭化物、高融点金属窒化物あるいは高融点金属ホウ化物の難焼結体からなるターゲット及びその製造方法並びに同スパッタリングターゲット−バッキングプレート組立体及びその製造方法

【課題】機械加工が難しい高融点金属合金、高融点金属珪化物、高融点金属炭化物、高融点金属窒化物あるいは高融点金属ホウ化物の難焼結体からなるターゲットを比較的容易に製造できるようにすると共に、ターゲット製造時及びハイパワースパッタリング時の割れの発生を効果的に抑制し、またターゲット原料のホットプレス時におけるダイスとの反応を抑制し、さらにターゲットの反りを低減できるターゲット及びその製造方法を提供する。

【解決手段】高融点金属合金、高融点金属珪化物、高融点金属炭化物、高融点金属窒化物あるいは高融点金属ホウ化物の難焼結体からなるターゲット材3とターゲット材以外の高融点金属板2,2’とが接合された構造を備えていることを特徴とする高融点金属合金、高融点金属珪化物、高融点金属炭化物、高融点金属窒化物あるいは高融点金属ホウ化物の難焼結体からなるターゲット。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】nチャネル型MISFET用のメタルゲート電極であるゲート電極GE1とpチャネル型MISFET用のダミーゲート電極GE2とを形成してから、nチャネル型MISFET用のソース・ドレイン領域とpチャネル型MISFET用のソース・ドレイン領域をそれぞれ形成する。その後、ダミーゲート電極GE2を除去し、ダミーゲート電極GE2が除去されたことで形成された凹部にpチャネル型MISFET用のメタルゲート電極を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置およびその製造方法

【課題】Ge半導体層に、極浅かつ高濃度のキャリアからなるn型不純物領域を形成する。

【解決手段】n型とp型のうちの一方の導電型の半導体基板と、半導体基板表面に選択的に設けられ、一方の導電型と異なる導電型の一対の不純物拡散領域と、一対の不純物拡散領域により挟まれた半導体基板上に設けられたゲート絶縁層と、ゲート絶縁層の上に設けられたゲート電極とを備え、不純物拡散領域の少なくとも一部は、基板に含まれる不純物と同じ導電型で、かつ基板の不純物濃度より高い不純物濃度を有する。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】熱処理装置のメンテナンス頻度を低減できると共に、電極表面荒れを防止しつつオーミックコンタクトの低抵抗化を図る炭化珪素半導体装置の製造方法を提供する。

【解決手段】P型SiC層10上に電極材料としてのAl−Ti合金11を堆積し、その上にTiNの保護膜12を形成する。その後、Alの融点を超える温度の熱処理を行い、Al−Ti合金11をP型SiC層10と反応させて合金化し、電極とP型SiC層10とのオーミックコンタクトを得る。保護膜12により、上記熱処理においてAl−Ti合金11からのAlの蒸発・飛散が防止される。

(もっと読む)

半導体装置及びその製造方法

【課題】可能な限り従来の設備及び加工プロセスを継承してコストの上昇を抑制するも、Ta含有の導電材料を難除去性の残留付着物を発生せしめることなく所望に加工し、容易且つ確実に信頼性の高い半導体装置を実現する。

【解決手段】半導体基板上に、Ta含有層、TiN層、及び多結晶シリコン膜等のドライエッチング可能な層を順次積層し、TiN層をエッチングストッパーとして多結晶シリコン膜をドライエッチングして所定形状に残し、TiN層及びTa含有層をSPM、APM等を用いてウェットエッチングして多結晶シリコン膜下で所定形状に残す。

(もっと読む)

マルチゲート電界効果トランジスタのゲート電極およびその製造方法

【課題】マルチゲート電界効果トランジスタにおいて、新規なゲート電極構造と製造方法を提供する。

【解決手段】マルチゲート電界効果トランジスタ102のゲート電極100は、半導体基板104と、前記半導体基板上の誘電体層106と、前記誘電体層上のフィン108と、前記フィンの側面上のゲート絶縁膜であって、前記フィンの側面上に形成されるゲート絶縁膜と接する誘電体層の上面部分を除き、前記誘電体層の上面上には形成されないゲート絶縁膜110と、フィン上のゲート電極層112と、前記フィンを覆うように形成されるポリシリコン層114とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】非酸化雰囲気下でなくても、良好なオーミック電極を形成可能な技術を提供する。

【解決手段】オーミック電極を有する半導体装置の製造方法であって、半導体基板50上に金属層30eを形成する工程と、金属層30e上に透過膜30fを形成する工程と、透過膜30fを通して金属層30eに電磁波を照射して、金属層30eを加熱する工程と、透過膜30fを除去する工程を有する。

(もっと読む)

ゲート電極及びその製造方法

【課題】フラットバンド電圧を制御できるとともに、半導体デバイス製造プロセスで使用される高温に曝されても特性の劣化が少ない、nMOSFETのゲート電極を与える。

【解決手段】炭化タンタルにイットリウムを添加した材料でゲート電極を作成する。このゲート電極はイットリウムの添加量に従ってフラットバンド電圧を調節できるとともに、600℃程度の熱処理を受けても特性の劣化が少ない。

(もっと読む)

タンタルチューブとPIT炭素芯の製造方法、タンタルチューブとPIT炭素芯、タンタル炭化物配線の製造方法及びタンタル炭化物配線

【課題】簡易な方法で、所定の形状のタンタルと炭素との固相拡散接合を可能とし更に、タンタルと炭素の固相拡散接合を行う場所以外のタンタル表面に炭化物を形成する方法を提供する。

【解決手段】タンタル若しくはタンタル合金をチューブ状の形状に加工し、チューブの中に炭素粉末を圧入し、その後、チューブをコイル形状に加工した後に真空熱処理炉内に設置し、タンタル若しくはタンタル合金表面に形成されている自然酸化膜であるTa2O5を除去した後、タンタル若しくはタンタル合金チューブ内面と前記炭素粉末PITを固相拡散結合で分子接合させるとともに、前記真空熱処理炉内に炭素源を導入してタンタル若しくはタンタル合金チューブの外表面に炭素を侵入させてTaCを形成する。

(もっと読む)

半導体装置の製造方法

【課題】高誘電率ゲート絶縁膜とメタルゲート電極を有するCMISFETを備えた半導体装置において、nチャネル型MISFETおよびpチャネル型MISFETのしきい値電圧の上昇を防ぐことができる技術を提供する。

【解決手段】CMISFETのしきい値を調整する目的で、高誘電率ゲート絶縁膜であるHf含有絶縁膜5に希土類元素またはアルミニウムを導入する際に、酸素をほとんど含まないランタン膜からなるしきい値調整層8bおよび酸素をほとんど含まないアルミニウム膜からなるしきい値調整層8aをnMIS形成領域1BおよびpMIS形成領域1AのHf含有絶縁膜5上にそれぞれ形成する。これにより、しきい値調整層8aおよびしきい値調整層8bからHf含有絶縁膜5および半導体基板1の主面に酸素が拡散することを防ぐ。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】素子分離領域13は、溝11に埋め込まれた酸化シリコン膜からなり、上部が半導体基板1から突出しており、半導体基板1から突出している部分の素子分離領域13の側壁上に、窒化シリコンまたは酸窒化シリコンからなる側壁絶縁膜SW1が形成されている。MISFETのゲート絶縁膜は、ハフニウムと酸素と低しきい値化用の元素とを主成分として含有するHf含有絶縁膜5からなり、メタルゲート電極であるゲート電極GEは、活性領域14、側壁絶縁膜SW1および素子分離領域13上に延在している。低しきい値化用の元素は、nチャネル型MISFETの場合は希土類またはMgであり、pチャネル型MISFETの場合は、Al、TiまたはTaである。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

カーボンナノチューブの形成方法及びカーボンナノチューブ成膜装置

【課題】被処理体上のビアホールや配線用溝等の開口部に高密度にカーボンナノチューブ膜を埋め込むことができるカーボンナノチューブの形成方法を提供する。

【解決手段】表面に1又は複数の開口部を有し、当該開口部底面に触媒金属層が形成された被処理体を準備し(STEP1)、触媒金属層に酸素プラズマ処理を施し(STEP2)、酸素プラズマ処理後の触媒金属層に水素含有プラズマ処理を施して、触媒金属層の表面を活性化し(STEP3)、その後、触媒金属層の上にプラズマCVDによりカーボンナノチューブを成長させて、被処理体の開口部内をカーボンナノチューブで充填する(STEP5)。

(もっと読む)

酸化表面層のハイブリッドその場ドライクリーニングプロセス

【課題】 集積回路における酸化表面層の洗浄を行うための新しいドライクリーニングプロセスの提供。

【解決手段】 一の実施例によると、当該方法は、酸化表面層を有する金属含有バリア層を含む基板を供する工程、前記酸化表面層を活性化させるために、プラズマ励起されたアルゴン気体を含む第1処理気体流へ前記酸化表面層を曝露する工程、及び、前記の第1処理気体流へ酸化表面層を曝露する工程中に基板バイアス電力を印加する工程を有する。当該方法は、非プラズマ励起された水素気体を含む第2処理気体へ前記の活性化した酸化表面層を曝露する工程をさらに有する。前記の第1処理気体流へ酸化表面層を曝露する工程は、前記酸化表面層を活性化させるのに加えて、水素気体を含む前記第2処理気体による、前記活性化した酸化表面層の還元を助ける。前記金属含有バリア層の厚さは、ハイブリッドその場ドライクリーニングプロセスによって実質的には変化しない。

(もっと読む)

半導体装置

【課題】メタルゲート電極内に基板面に対して平行な金属とシリコンなどとの境界又はシリサイドとシリコンなどとの境界を含むメタルゲート電極において、トランジスタの接続抵抗が小さく、高速動作時のトランジスタの遅延又はトランジスタ特性のばらつきなどの特性劣化の懸念がなく、且つ、低コストな構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101上に、ゲート絶縁膜105と、pMIS用金属材料109又はnMIS用金属材料111と、ゲート電極材料112と、ゲート側壁メタル層122とを備えている。

(もっと読む)

21 - 40 / 257

[ Back to top ]