Fターム[4M104BB34]の内容

Fターム[4M104BB34]に分類される特許

101 - 120 / 257

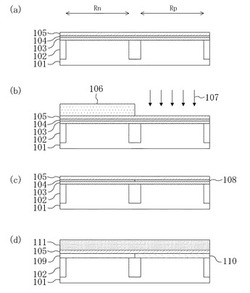

半導体装置及びその製造方法

【課題】STI幅の増加や信頼性の低下を招くことなく、所定の導電型トランジスタ領域において最適なHigh-kゲート絶縁膜を実現する。

【解決手段】N型トランジスタ領域RnとP型トランジスタ領域Rpとを含む半導体基板101上の全面にHigh-k絶縁膜103、N型トランジスタ用キャップ膜104及び金属含有膜105を順次堆積する。P型トランジスタ領域Rpに位置するN型トランジスタ用キャップ膜104にイオン107を導入することにより、P型トランジスタ用キャップ膜108を形成する。金属含有膜105上にポリシリコン膜111を堆積した後、パターニングにより、N型トランジスタ用ゲート電極113及びP型トランジスタ用ゲート電極114を形成する。

(もっと読む)

半導体装置、及びその製造方法

【課題】 金属層と半導体層との接続抵抗の上昇を抑えた積層ゲート電極を有する半導体装置、及びその製造方法を提供する。

【解決手段】 半導体装置10は、半導体基板11に形成された第1導電型のソース領域及びドレイン領域14と、ソース領域とドレイン領域との間に形成されたチャネル領域16と、チャネル領域上に形成されたゲート絶縁膜21とを有する。半導体装置10は更に、ゲート絶縁膜上に形成された金属ゲート電極層22と、金属ゲート電極層上に形成された、第1導電型とは逆の導電型である第2導電型の半導体ゲート電極層23とを有する。

(もっと読む)

バリア蒸着のための液相分子自己組織化および形成構造

マイクロ電子構造を形成する方法及びその形成構造について記載する。無水溶媒に金属前躯体を溶液槽にて溶解し、配線開口を有する基板を溶液槽に配置して、金属前躯体により配線開口内に単分子層を形成する。また、基板を共反応体の混合液中に配置して、共反応体と金属前躯体とを反応させて薄いバリア層を形成する。 (もっと読む)

半導体装置及びその製造方法

【課題】高速動作が可能なMIPS構造を持つメタルゲートを含む半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜3と、該ゲート絶縁膜3の上に順次形成され、TiN膜4とポリシリコン膜5とにより構成されたゲート電極20の第2のゲート電極部20bと、半導体基板1の上にゲート電極20を覆うように形成された層間絶縁膜8とを有している。層間絶縁膜8及びポリシリコン膜5を貫通して形成されたコンタクト9は、TiN膜4と直接に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、第1のゲート絶縁膜13aと、第1の下層導電膜14a及び第1のシリコン膜18aを有する第1のゲート電極19aとを備えた第1導電型の第1のトランジスタが形成されており、半導体基板10の第2の活性領域10b上には、第2のゲート絶縁膜13bと、第2の下層導電膜14b及び第2のシリコン膜18bを有する第2のゲート電極19bとを備えた第2導電型の第2のトランジスタが形成されている。第1のゲート絶縁膜13aは高誘電体材料と第1の金属とを含有し、第1の下層導電膜14aは導電材料と第1の金属とを含有し、第2の下層導電膜14bは第1の下層導電膜14aと同一の導電材料を含有している。

(もっと読む)

半導体装置

【課題】ゲート金属起因の閾値変調効果が制御されたCMISFETを提供する。

【解決手段】半導体基板上に設けられたCMISFETにおいて、pMISFETのゲート電極は、第1のゲート絶縁膜上に形成された第1の金属層と、その上に形成されたIIA族及びIIIA族に属する少なくとも1つの金属元素を含む第1の上部金属層とを具備し、nMISFETのゲート電極は、第2のゲート絶縁膜上に形成された第2の金属層と、第2の金属層上に形成され、前記第1の上部金属層と実質的に同一組成の第2の上部金属層とを具備し、第1の金属層が第2の金属層よりも厚く、第1及び第2のゲート絶縁膜は前記金属元素を含み、第1のゲート絶縁膜に含まれる前記金属元素の原子密度が、第2のゲート絶縁膜に含まれる前記金属元素の原子密度よりも低い。

(もっと読む)

半導体装置及びその製造方法

【課題】メタルゲート形成用等の金属原子が半導体基板、特にゲート絶縁膜に残存することによるゲートリーク電流の増大又はゲート電極の形成材料における仕事関数の変動を防止できるようにする。

【解決手段】まず、N型電界効果トランジスタを形成するNFET形成領域50NとP型電界効果トランジスタを形成するPFET形成領域50Pとを有する半導体基板1の上に、ゲート絶縁膜3を形成する。続いて、ゲート絶縁膜3の上に、第1のポリシリコン膜4を形成し、形成した第1のポリシリコン膜4におけるPFET形成領域に含まれる部分を除去することにより、PFET形成領域50Pからゲート絶縁膜3を露出する。その後、PFET形成領域50Pにおけるゲート絶縁膜3の上に窒化チタン膜6を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】

歪み技術を用いたMOSトランジスタにおいて、リーク電流を抑える。

【解決手段】

半導体装置は、第1の格子定数を有する第1の半導体で形成された半導体基板に形成され、活性領域を画定する素子分離領域と、活性領域の中間位置を横断して、半導体基板上方にゲート絶縁膜を介して形成されたゲート電極と、ゲート電極側壁上に形成されたサイドウォールスペーサとを含むゲート電極構造と、ゲート電極構造両側の活性領域と素子分離領域との界面が半導体基板の表面に表出した境界の一部を覆って半導体基板の表面上方に配置された他のゲート電極構造であって、他のゲート電極と該他のゲート電極の側壁上に形成された他のサイドウォールスペーサとを含む他のゲート電極構造と、ゲート電極構造と他のゲート電極構造の間の活性領域をエッチして形成されたリセスと、リセスを埋めてエピタキシャル成長され、第1の格子定数と異なる第2の格子定数を有する第2の半導体で形成された半導体層と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成する際に、ゲート絶縁膜に金属原子が注入されることを抑制し、ゲートリーク電流の増加や閾値電圧の不安定化等を防止する。

【解決手段】MOSトランジスタを備える半導体装置の製造方法である。半導体基板11上にゲート絶縁膜12を形成する。ゲート絶縁膜12上に金属原子を複数個含むクラスタのイオン13を堆積させ、ゲート電極14の少なくとも最下層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

トレンチゲート型半導体装置およびその製造方法

【課題】ワイドバンドギャップ半導体を主たる半導体基板として用い、セルピッチを縮小することができ、良好なオーミック接触が得られ、トレンチ底の絶縁膜に過大な電界が印加されないトレンチゲート型半導体装置およびその製造方法を提供すること。

【解決手段】交差トレンチ10pの形成方法として、二重トレンチ構造としたゲートトレンチ10bを形成した後に、当該ゲートトレンチ10bをマスク材料で埋め戻し、その後、当該マスク材料をパターニングして、交差トレンチを形成するためのマスクとして用い、ゲートトレンチに交差する交差トレンチ10pをゲートトレンチ10bよりも深く設け、交差トレンチ10p底部にショットキー電極24を設けるトレンチゲート型MOSFETの製造方法とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極である金属膜/多結晶シリコン膜間の接触抵抗が大きい場合であっても、ゲートコンタクトプラグに印加した電界を十分な速度で十分に金属膜に伝えることができる半導体装置、およびその製造方法を得ることを目的とする。

【解決手段】本発明の一実施形態における半導体装置は、半導体基板1と、半導体基板1上に形成されたゲート絶縁膜3と、ゲート絶縁膜3上に形成された金属膜4、当該金属膜4上に形成された多結晶シリコン膜5、を有するゲート電極6と、ゲート電極6上に形成された層間絶縁膜11と、層間絶縁膜11および多結晶シリコン膜5を貫通して金属膜4と接触するように形成されたコンタクトプラグ12と、を備える。

(もっと読む)

二重仕事関数半導体デバイスおよびその製造方法

【課題】簡単化した集積機構を備えた二重仕事関数半導体デバイスおよびその製造方法を提供する。

【解決手段】二重仕事関数半導体デバイスは、第1実効仕事関数を有する第1ゲートスタック111を含む第1トランジスタと、第1実効仕事関数とは異なる第2実効仕事関数を有する第2ゲートスタック112を含む第2トランジスタとを備える。第1ゲートスタック111は、第1ゲート誘電体キャップ層104、ゲート誘電体ホスト層105、第1金属ゲート電極層106、バリア金属ゲート電極層107、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2ゲートスタック112は、ゲート誘電体ホスト層105、第1金属ゲート電極層106、第2ゲート誘電体キャップ層108、第2金属ゲート電極層109を含む。第2金属ゲート電極層109は、第1金属ゲート電極層106と同じ金属組成からなる。

(もっと読む)

CMISトランジスタの製造方法

【課題】本発明は、PMISトランジスタ側とNMISトランジスタ側とでシリサイド層の組成のバラツキを防止でき、またトランジスタのゲート形状の不安定化を防止できる、CMISトランジスタの製造方法を提供する。

【解決手段】ゲート絶縁膜103とN−metal104と多結晶シリコン106とが当該順に積層した第一のゲート構造G1を形成する。ゲート絶縁膜103と多結晶シリコン106とが当該順に積層した第二のゲート構造G2を形成する。第一、二のゲート構造G1,G2をマスクした状態で、各ゲート構造G1,G2の両脇における半導体基板101上を、シリサイド化させる。そして、第一、二のゲート構造G1,G2を構成する多結晶シリコン106を、シリサイド化させる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Hf−O系絶縁膜上に、TaCx膜を用いたメタルゲート電極を備えたMISトランジスタの実効仕事関数を制御する。

【解決手段】SOI基板1のシリコン層1c側よりゲート絶縁膜2を形成する。次いで、ゲート絶縁膜2上に室温スパッタ法によってTaCx膜を堆積し、このTaCx膜から構成されるメタルゲート電極3を形成する。次いで、メタルゲート電極3上にアモルファス状態のシリコン膜を形成した後、メタルゲート電極3に熱処理を施す。次いで、前記シリコン膜を除去した後、メタルゲート電極3に酸素を添加する。

(もっと読む)

半導体装置

【課題】メタルをゲート電極材料に用いたCMIS素子の閾値を低減する。

【解決手段】p型MISトランジスタQpのゲート絶縁膜5上に設けられたp型ゲート電極7は、順に、カチオン比でAlが10%以上50%以下のTiAlNから構成される第1金属膜30と、TiNから構成され、膜厚が5nm以下の第2金属膜31と、Siを主成分として含有する導電体膜32とが積層された構造を有している。また、n型MISトランジスタQnのゲート絶縁膜5上に設けられたn型ゲート電極6は、順に、第2金属膜31と、導電体膜32とが積層された構造を有している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート絶縁膜の信頼性および半導体装置の性能を確保可能である半導体装置の製造方法および半導体装置を提供する。

【解決手段】本発明にかかる半導体装置の製造方法は、Si基板100上にゲート絶縁膜103を形成するゲート絶縁膜形成工程と、ゲート絶縁膜103上に第1の金属膜を形成する第1の金属膜形成工程と、第1の金属膜上に金属電極104を構成する第2の金属膜を形成する第2の金属膜形成工程と、熱処理を行なってゲート絶縁膜103と第1の金属膜との間にゲート絶縁膜103と第1の金属膜との反応膜118を形成する反応膜形成工程とを行なって、第1の金属膜形成工程時のゲート絶縁膜103の損傷を回復させている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数の半導体素子がそれぞれ所望の特性を有し、かつ信頼性の高い半導体装置およびその半導体装置を容易に製造することのできる半導体装置の製造方法を提供する。

【解決手段】ゲート絶縁膜6の上面上に、全面的に、3〜30nmの厚みのゲート電極用金属膜Mを形成する。次に、ゲート電極用金属膜Mの上面のうちでnFET領域Rn内に属する部分にのみ、全面的に、ゲート電極用金属膜Mとは異種材料の、10nm以下の厚みのn側キャップ層8Aを形成する。その上で、熱処理を行って、n側キャップ層8Aを、その直下のゲート電極用金属膜M内に拡散・反応させて、nFET領域Rn内にn側ゲート電極用金属膜MAを形成する。それ以降は、ポリSi層を堆積した上で、ゲート電極加工を施す。

(もっと読む)

半導体装置

【課題】高い反転層キャリア移動度を有するシングルメタルCMISFETを提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板上に形成されたpチャネルMISトランジスタとnチャネルMISトランジスタとを具備し、pチャネルMISトランジスタとnチャネルMISトランジスタは、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極層を夫々備え、pチャネルMISトランジスタとnチャネルMISトランジスタのゲート電極における、少なくともゲート絶縁膜と接する最下層は、TaとCを含む同一組成を有し、CとTaとの合計に対するTaのモル比(Ta/(Ta+C))が0.5より大であり、最下層は同一配向性を有することを特徴とする。

(もっと読む)

半導体装置

【課題】伝導不純物のエネルギー準位が動作温度に対応する熱励起エネルギーよりも深い位置にある半導体材料により形成した半導体素子に高密度の電流を流す。

【解決手段】この接合素子1では、半導体層2内に空乏層が形成されることにより、順方向に電圧が印加された際、電極層4に存在する電子は半導体層2に移動することができない。このため、半導体層3の正孔の大多数は半導体層2内の伝導電子と再結合によって消滅することなく、半導体層2に拡散しながら電極層4に到達する。これにより、抵抗値の影響を受けることなく正孔に対して良導体として作用することができ、SiやSiC半導体で形成された半導体素子と同等又はそれ以上の電流を流すことができる。

(もっと読む)

101 - 120 / 257

[ Back to top ]