Fターム[4M104BB34]の内容

Fターム[4M104BB34]に分類される特許

141 - 160 / 257

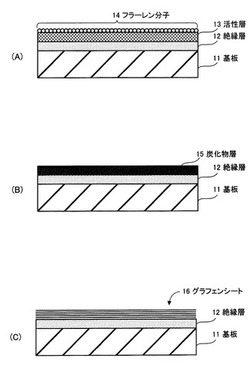

グラフェンシートの製造方法、半導体装置の製造方法および半導体装置

【課題】結晶性、層数を制御する。

【解決手段】基板11上に絶縁層12を介して形成した活性層13にフラーレン分子14を堆積する工程と、活性層13およびフラーレン分子14を加熱して炭化物層15を形成する工程と、炭化物層15をさらに加熱する工程と、を有するグラフェンシート16の製造方法によって、基板11上に絶縁層12を介して形成した活性層13にフラーレン分子14が堆積され、活性層13およびフラーレン分子14を加熱して炭化物層15が形成され、炭化物層15がさらに加熱されて、ドメイン数が少なく高い結晶性を持つグラフェンシート16が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】それぞれが最適なゲート絶縁膜及びゲート電極を有するp型MISFET及びn型MISFETを備え且つ不良の原因となるポリシリコン膜残渣が発生することがない半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板10の第1領域10Aの上に形成された第1のゲート絶縁膜13Aと、第1のゲート絶縁膜13Aの上に形成された第1のゲート電極14Aと、半導体基板10の第2領域10Bの上に形成された第2のゲート絶縁膜13Bと、第2のゲート絶縁膜13Bの上に形成された第2のゲート電極14Bとを備えている。第1のゲート絶縁膜13Aは、第1の金属を含む第1の材料からなる第1の絶縁膜を有し、第2のゲート絶縁膜13Bは、第1の材料と第2の金属を含む第2の材料とが混合された第2の絶縁膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル及びpチャネルのゲート構造が異なり且つメタルゲート電極を有する半導体装置において、ゲート電極パターン形成時のドライエッチングでゲート絶縁膜の突き抜けが発生しないようにする。

【解決手段】ゲート絶縁膜105と接する第2ゲート電極材料膜(TiN膜)111がゲート電極151の一部として形成されないnチャネル領域103上に、第2ゲート電極材料膜(TiN膜)111のエッチング時にオーバーエッチング吸収層として機能する第1ゲート電極材料膜(ポリシリコン膜)107を予め形成しておく。

(もっと読む)

半導体装置及びその製造方法

【課題】駆動能力を低下させることなく、半導体装置内部の高電界が与える影響によって生じるGIDLを低減する。

【解決手段】ゲート電極108は、ゲート電極108のチャネル長方向の中央部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第1の導電部108Aと、ゲート電極108のチャネル長方向の両端部に位置し且つ高誘電率膜107つまりゲート絶縁膜と接する第2の導電部108Bとを含む。第1の導電部108Aの第1の仕事関数と第2の導電部108Bの第2の仕事関数とが異なっている。

(もっと読む)

相補型半導体装置及びその製造方法

【課題】 メタルゲート電極及び高誘電率ゲート絶縁膜を用いたn型MISトランジスタとp型MISトランジスタの双方において適正なしきい値電圧を得る。

【解決手段】 半導体基板30の表面部に形成された第1及び第2の半導体領域10,20と、第1の半導体領域10上に形成された、La及びAlを含む第1のゲート絶縁膜11及び第1のゲート電極12を有するn型MISトランジスタと、第2の半導体領域20上に形成された、La及びAlを含む第2のゲート絶縁膜21及び第2のゲート電極22を有するp型MISトランジスタと、を備えた相補型半導体装置であって、第2のゲート絶縁膜22における原子濃度比Al/Laが、第1のゲート絶縁膜11における原子濃度比Al/Laよりも大きい。

(もっと読む)

半導体装置およびその製造方法

【課題】リーク電流の増大や被膜性の劣化やトランジスタ特性の劣化等のエッチングに伴う不具合を防ぐことが可能な半導体装置およびその製造方法を提供する。

【解決手段】CMOSトランジスタ500は、ゲート電極202を有するN型MOSトランジスタおよびゲート電極201を有するP型MOSトランジスタを同一の半導体基板1上に備え、ゲート電極202は、ゲート絶縁膜5と多結晶シリコン層61と金属層62と多結晶シリコン層63とを含み、ゲート電極201は、ゲート絶縁膜5と金属層62と多結晶シリコン層63とを含む。

(もっと読む)

デュアル仕事関数半導体デバイスおよびその製造方法

【課題】CMOSを製造するにおいて、1つまたは2つの誘電体を有するデュアル金属ゲートを形成する場合の、本質的な製造プロセスの複雑さや費用が増加しない、製造が容易で信頼性のある、デュアル仕事関数を有する半導体デバイスの製造方法を提供する。

【解決手段】1つの金属電極から開始するデュアル仕事関数デバイスの簡単な製造方法およびそのデバイスを開示する。シングル金属シングル誘電体(SMSD)CMOS集積スキームが開示される。ゲート誘電体層1と誘電体キャップ層2および誘電体キャップ層2’’とを含む1つの誘電体スタックと、誘電体スタックを覆う1つの金属層とが、最初に形成され、金属−誘電体界面を形成する。誘電体スタックと金属層を形成した後、誘電体キャップ層2’’の、金属−誘電体界面に隣接する少なくとも一部が、仕事関数変調元素6を加えることにより選択的に変調される。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化されても、EOTの増膜が抑制され、且つ、良好な品質を有する高誘電率膜を備えた信頼性の高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、半導体基板1内に形成された第1導電型の第1の領域3及び第2導電型の第2の領域4と、半導体基板1上であって、第1の領域3及び第2の領域4の上に形成されたゲート絶縁膜5と、ゲート絶縁膜5上に形成された保護膜6と、保護膜6のうち第1の領域3の上に設けられた部分上に形成され、金属からなる第1のゲート電極9と、保護膜6のうち第2の領域4の上に設けられた部分上に形成された第2のゲート電極12とを備えている。ゲート絶縁膜5及び保護膜6は、高誘電率膜からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】FinFETにおいて、従来のFinFETの構造に比してさらにチャネルに応力を印加することができる半導体装置を提供すること。

【解決手段】Si基板1と、フィン11、フィン11の延在方向に平行な面上にゲート絶縁膜13を介して形成される所定の幅のゲート電極14、およびフィン11の延在方向に平行な面上のゲート電極14の両側に形成されるソース/ドレイン領域を含むFinFET10n,10pと、を備え、ゲート電極14上に形成され、応力印加層31,32の形成温度と室温での線膨張係数の差が、フィン11の形成温度と室温での線膨張係数の差と異なる導電性材料によって形成される応力印加層31,32と、応力印加層31,32上に形成され、フィン11よりもヤング率の大きい導電性材料からなるプラグ層33,34と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】p−MISトランジスタとn−MISトランジスタとのゲート電極形状のばらつきが少ない半導体装置の製造方法を提供する。

【解決手段】第1および第2領域13、14にゲート絶縁膜17を介して第1金属を含む第1金属膜18を形成する工程と、第1領域13における第1金属膜18を保護膜で被覆し、第2領域14における第1金属膜18を除去してゲート絶縁膜17を露出させる工程と、第1金属膜18上およびゲート絶縁膜17上に第1金属と異なる第2金属を含む第2金属膜19を形成する工程と、ゲート電極パターンを有するマスク材を用いて第2金属膜19を異方性エッチングし、第2領域14に第2ゲート電極を形成する工程と、第1金属膜18および第2金属膜19の露出部に酸化処理を施す工程と、第1領域13における第1金属膜18を異方性エッチングし、第1領域13に第1ゲート電極を形成する工程とを具備する。

(もっと読む)

炭化珪素装置

【課題】炭化珪素基板との密着性がよく、ショットキーバリアハイトのばらつきが小さいとともに逆方向電圧印加時のリーク電流が少ない炭化珪素ショットキーバリアダイオードを実現することを課題とする。

【解決手段】炭化珪素と金属とのショットキー電極界面が炭化金属と金属シリサイド、金属とシリコンと炭素の3元系化合物又はこれらの混合物であることを特徴とするJBS(Junction Barrier controlled Schottky diode:接合障壁ショットキーダイオード)構造の炭化珪素ショットキーバリアダイオードである。

(もっと読む)

半導体装置の製造方法

【課題】 本発明は、金属元素を有する絶縁膜の界面特性を向上させる半導体装置の製造方法を提供することを目的とする。

【解決手段】 本発明の半導体装置の製造方法は、下層、Ge層、Ge酸化物層、上層の順に積層された構造を形成する工程と、熱処理を用いてGe酸化物層及びGe層を除去して、上層と下層とを直接接合させる工程とを有し、上層及び下層の何れかは金属元素を有する絶縁物で形成されることを特徴とする。

(もっと読む)

半導体装置

【課題】 ゲート電極上のシリサイド膜の断線を抑制する。

【解決手段】 ソース・ドレイン領域をデュアルシリサイド構造とし、ゲート電極の仕事関数はn型MISトランジスタ、p型MISトランジスタそれぞれの有するメタルゲート電極により定める構造とし、且つ、メタルゲート電極上の多結晶シリコン層は共通のn+ドーピング層とし、ゲート上シリサイド膜はn型領域に対しショットキー障壁が低くなる材料で形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造コストを低減する。

【解決手段】半導体装置の製造方法は、高誘電率膜が形成された基板を処理室内に搬入するステップと、前記処理室に接続されたプラズマユニットによるプラズマによって活性化した窒素原子を含むガスを前記処理室内に供給して前記高誘電率膜に対してプラズマ窒化処理を施すステップと、前記処理室内に成膜ガスを供給して前記プラズマ窒化処理後の高誘電率膜上に電極膜を形成するステップと、前記電極膜形成後の基板を前記処理室内から搬出するステップと、前記プラズマユニットによるプラズマによって活性化したクリーニングガスを前記処理室内に供給して前記処理室内をクリーニングするステップと、を有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】Pチャネル型トランジスタの閾値電圧を制御することができる半導体装置、およびその半導体装置の製造方法を提供する。

【解決手段】NTrとPTrとを含む半導体装置において、N型チャネル形成領域とP型チャネル形成領域とを有するN型半導体基板2上に絶縁膜Fが形成され、絶縁膜Fにゲート電極用溝A及びBとが形成され、ゲート電極用溝A及びBの内側表面上にゲート絶縁膜20が形成され、NTr領域におけるゲート絶縁膜20上にNTr仕事関数制御メタル膜21が形成され、NTr仕事関数制御メタル膜21及びゲート絶縁膜20上にフッ素がドープされたPTr仕事関数制御メタル膜23が形成され、PTr仕事関数制御メタル膜23の上層に、ゲート電極用溝に埋め込まれてゲート電極が形成されている構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極構造が異なるNch絶縁ゲート型電界効果トランジスタとPch絶縁ゲート型電界効果トランジスタのゲート電極形状を安定化させる。

【解決手段】半導体装置50には、Nch MISFETとPch FMISFETが半導体基板1上に設けられる。半導体基板1上に、Nch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜8、及び絶縁膜10が積層形成される。半導体基板1上に、Pch MISFETのソースとドレインの間にオーバラップしてゲート絶縁膜7、ゲート電極膜9、及び絶縁膜10が積層形成される。ゲート電極膜9はゲート電極膜8よりもゲート電極膜同時加工時での補正膜厚分だけ薄く形成されている。

(もっと読む)

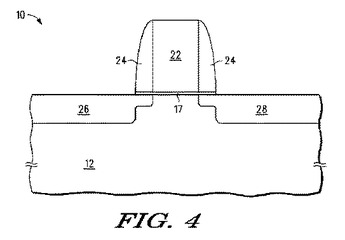

CETスケーリング用高k誘電体の処理方法

半導体装置(10)の作製方法は、上に重なるゲート電極(22)を有するゲート誘電体(17)を作製することを含む。半導体装置(10)は半導体層(12)上に作製される。ジルコン酸ハフニウムを含む高k誘電体(16)は半導体層上に蒸着される。高k誘電体は、水素と窒素を含む雰囲気中で650℃〜850℃の間の温度でアニーリングされる。ゲート電極(22)は高k誘電体上に形成される。高k誘電体機能は、ゲート誘電体(17)での使用のためである。一つの効果は、ゲート漏れのレベルを保持する、またはさらには改善させつつ、トランジスタの性能を向上させることである。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】N−chトランジスタとP−chトランジスタとの境界の寸法制御性に優れ、工程数の増加を最小限に抑制しながら、N−chトランジスタ及びP−chトランジスタのゲートパターンの高さが可能な限り揃った構造を実現する。

【解決手段】基板上のHigh−k膜よりなる絶縁膜上にポリシリコンを形成する。該ポリシリコン膜をエッチングする際にハロゲン系ガスを用いた低バイアス処理を施すことにより、下地のHigh−k膜の膜質を改善しながら、N−chトランジスタ及びP−chトランジスタに独立した仕事関数を持つ金属電極を形成する。

(もっと読む)

半導体装置

【課題】それぞれが適した閾値を有するフィン型MOSFETとプレーナ型MOSFETが混載され、且つ少ない工程で製造することができる半導体装置を提供する。

【解決手段】本発明の一態様に係る半導体装置は、第1のゲート電極と、前記第1のゲート電極にフェルミレベルピニングを発生させない第1のゲート絶縁膜と、を有するプレーナ型MOSFETと、第2のゲート電極と、前記第2のゲート電極にフェルミレベルピニングを発生させる第2のゲート絶縁膜と、を有するフィン型MOSFETと、を有する。

(もっと読む)

有機薄膜トランジスタアレイおよびその製造方法

【課題】有機TFTにおいて、電子注入効率とホール注入効率を改善した電極と有機半導体の組み合わせをそれぞれ判別する手法を提供し、また、n型チャネルTFTとp型チャネルFETの2種類のTFTを実現し、相補型有機薄膜トランジスタ(有機CTFT)および、有機CTFTによる所望の任意回路構成を形成する相補型有機TFTアレイを提供する。

【解決手段】半導体−電極界面、および、半導体−絶縁体界面におけるフェルミエネルギーの差の大きさを与える数式を用いて、TFT材料を変えずに上薬だけを選択的に変化してn型とp型のTFTを実現する。このとき、任意回路を構成するために、まずp型TFT用のソース電極15とドレイン電極16、および、n型TFT用のソース電極14とドレイン電極16をそれぞれすべて繋いでおいて、上記プロセスを行い、その後、光照射(走査型レーザー露光装置など)により不要配線を切断する。

(もっと読む)

141 - 160 / 257

[ Back to top ]