Fターム[4M104BB37]の内容

Fターム[4M104BB37]に分類される特許

21 - 40 / 284

金属酸化物粒子分散組成物

【課題】成膜後の金属酸化物粒子の緻密性を改善することができ、所望の性能を有する金属酸化物半導体薄膜や透明導電膜を形成することが可能な金属酸化物粒子分散組成物を提供する。

【解決手段】金属酸化物粒子と、金属塩及び/又は有機金属化合物と、溶媒とを含有する透明導電膜形成用の金属酸化物粒子分散組成物であって、前記金属酸化物粒子は、Zn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属の酸化物を含有し、かつ、前記金属塩及び/又は有機金属化合物は、Zn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属の金属塩及び/又はZn、Ga、In、Sn、Al、Sb、Cd及びFeからなる群より選択される少なくとも1種の金属を含む有機金属化合物である金属酸化物粒子分散組成物。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

半導体装置、半導体装置用基板および該基板の製造方法

【課題】電気的接続の信頼性を損なうことなく電気抵抗率を従来よりも低減できる埋め込み配線を有する半導体装置用基板および半導体装置を提供する。

【解決手段】本発明は、上記目的を達成するため、埋め込み配線を有する半導体装置用基板であって、前記埋め込み配線は、金属多結晶体からなり、平均結晶粒径が異なる少なくとも2層の領域を前記基板の厚さ方向に有し、前記埋め込み配線の開口面を含む層の平均結晶粒径が、前記埋め込み配線の他の層の平均結晶粒径よりも小さいことを特徴とする半導体装置用基板を提供する。また、本発明は、上記半導体装置用基板を用いたことを特徴とする半導体装置を提供する。

(もっと読む)

酸化物半導体用電極、その形成方法、及びその電極を備えた酸化物半導体装置

【課題】薄膜トランジスタなどの素子動作層をなす導電性インジウム含有酸化物半導体層に電気的接触抵抗が小さい金属電極を形成できるようにする。

【解決手段】インジウム含有酸化物半導体層とその層の上方に設けた素子動作電流を流通させる金属電極層との間に、酸化物半導体層をなすインジウム酸化物などを化学的に還元でき、且つ易酸化性の金属からなる金属膜を素材とした金属酸化物層と金属層とを設け、更に、金属酸化物層と金属層との境界には還元されたインジウムを蓄積したインジウム濃化層を設ける構成とする。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

ダイオード用半導体担持電極材料

【課題】良好な整流特性を示すショットキー型ダイオードデバイスに利用可能な、半導体層を担持した安価な材料を提供する。

【解決手段】Cr含有量が10.5〜32.0質量%であるFe−Cr系合金の母材21と、その母材を酸化性雰囲気に加熱することによって形成させた表面酸化皮膜22とが一体となった材料であって、AESによる前記酸化皮膜表面からの深さ方向分析において酸素濃度が最大酸素濃度の1/2となる深さ位置に対応するSiO2換算深さを当該酸化皮膜の膜厚とするとき、当該酸化皮膜は、膜厚が17〜50nmのn型半導体であり、かつ皮膜表面側から順にFe主体アモルファス酸化物、Cr濃化したFe−Cr結晶酸化物を形成して母材とオーミック接合で一体化しており、n型半導体中のドナー密度が1E16cm−3〜1E18cm−3の範囲で含まれているダイオード用n型半導体担持電極材料。

(もっと読む)

半導体集積回路装置用ルテニウムバリア膜とその作製方法及び該ルテニウムバリア膜を有する半導体集積回路装置とその製造方法

【課題】クレバスの面積比が小さく、低抵抗を維持した薄膜の状態で、配線層を構成する銅又はアルミニウム等の拡散を防止できるルテニウムバリア膜とその作製方法及び該ルテニウム膜を有する半導体集積回路装置とその製造方法を提供する。

【解決する手段】ルテニウムバリア膜は、ルテニウムを主成分とする金属からなり、表面上に観測されるクレバス(溝、割れ目又は深く鋭いくぼみ)の占める面積比が、前記バリア膜表面の全面積に対して15%以下であり、広角X線回折測定によって得られるX線回折プロファイルにおいて、ルテニウムの結晶配向面(002)及び(100)に起因するスペクトルのそれぞれのピーク強度比であるRu(002)/Ru(100)が10以上であり、また、スパッタリング法によって、温度を500℃以上に加熱した状態の半導体基板の配線溝上に成膜されることを特徴とする。

(もっと読む)

酸化物膜の製造方法

【課題】p型の導電膜及びp型の透明導電膜としての高性能な酸化物膜の、量産性に優れた製造方法を提供する。

【解決手段】

本発明の1つの酸化物膜の製造方法は、酸素を含むガスの雰囲気下で、反応性スパッタリング法により、銅(Cu)からなる第1ターゲット30a,30aとニオブ(Nb)およびタンタル(Ta)からなる群から選択される1種類の遷移元素からなる第2ターゲット30b,30bとを用いて交互にスパッタを行うことにより、基板10上に第1酸化物膜(不可避不純物を含み得る)を形成する工程、及びその第1酸化物膜を不活性ガス雰囲気中で加熱焼成することにより第2酸化物膜(不可避不純物を含み得る)を形成する工程を含む。従って、この製造方法によって形成された酸化物膜は、大型基板上への膜の形成が容易になることから、量産性に優れている。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体発光素子及びその製造方法

【課題】電気的特性が良好で加工性が良好な電極を有する半導体発光素子及びその製造方法を提供する。

【解決手段】実施形態によれば、第1導電形の第1半導体層と、第2導電形の第2半導体層と、発光部と、第1導電層と、第2導電層と、を備えた半導体発光素子が提供される。前記発光部は、前記第1半導体層と前記第2半導体層との間に設けられる。前記第1導電層は、第1平均粒径を有する多結晶を含み、前記発光部から放出される光に対して透過性である。前記第2導電層は、前記第2半導体層と前記第1導電層との間において前記第2半導体層と前記第1導電層とに接し、前記第1平均粒径よりも小さく150ナノメートル以下の第2平均粒径を有する多結晶を含み、前記光に対して透過性である。

(もっと読む)

半導体装置の製造方法

【課題】タングステン膜を使用した部分の抵抗を低減した半導体装置を提供する。

【解決手段】半導体装置の製造方法では、基板内に設けた開口部内、又は基板上にタングステン膜を形成する。タングステン膜の形成後、エッチバック又はエッチングを行う前にタングステン膜に対してアニール処理を行う。これにより、タングステン膜の結晶状態を変化させる。

(もっと読む)

成膜装置

【課題】表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンを成膜できる成膜装置を提供すること。

【解決手段】下地を有した被処理体1を収容する処理室101と、処理ガス供給機構114と、加熱装置133と、排気機構132と、コントローラ150とを具備し、コントローラ150が、加熱した下地にアミノシラン系ガスを流し、下地の表面にシード層を形成する工程と、加熱した下地の表面のシード層にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層上にアモルファスシリコン膜を形成する工程とが実施されるように処理ガス供給機構114、加熱装置133及び排気機構132を制御し、シード層を形成する工程における下地の加熱温度及び処理時間を、アモルファスシリコン膜を形成する工程におけるそれらよりも低く及び短くする。

(もっと読む)

電子部品の製造方法

【課題】高温で成膜される低融点金属の凝集を防止し、十分なバリア性及びぬれ性を有するバリア層を形成して、凹部に低融点金属を付け回り良く充填する。

【解決手段】電子部品の製造方法が、4Pa以上20Pa以下の圧力下で、被処理体306と接する電極301に第1のバイアス電力を印加し、プラズマ処理により被処理体306の上にTiNxからなる第1のバリア層404を成膜する手順と、4Pa以上20Pa以下の圧力下で、電極301に第1のバイアス電力よりも小さいイオン入射エネルギーを与える第2のバイアス電力を印加し、またはバイアス電力を印加しないで、プラズマ処理により第1のバリア層の上にTiNxからなる第2のバリア層405を成膜する手順と、第2のバリア層405の上に、Tiからなる第3のバリア層409を成膜する手順と、第3のバリア層409の上に低融点金属406を充填する手順と、を有する。

(もっと読む)

半導体装置の製造方法並びにコンタクトホール及び/又はラインの埋め込み方法

【課題】 表面ラフネスの精度をさらに改善でき、コンタクトホールやラインなどの微細化の進展に対応可能なアモルファスシリコン膜を成膜できる半導体装置の製造方法を提供すること。

【解決手段】 半導体装置内部のコンタクトホール5及び/又はラインが形成された層間絶縁膜である下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜4を形成する工程と、を備える。

(もっと読む)

半導体装置及びその作製方法

【課題】ノーマリーオフのトランジスタ、或いは当該トランジスタを含んで構成される回路を有する半導体装置を提供する。

【解決手段】チャネル形成領域として機能する第1の酸化物半導体層と、当該第1の酸化物半導体層と重なるソース電極層及びドレイン電極層と、当該第1の酸化物半導体層、当該ソース電極層、及び当該ドレイン電極層と接するゲート絶縁層と、当該ゲート絶縁層に接して当該第1の酸化物半導体層と重なる第2の酸化物半導体層と、当該第2の酸化物半導体層上に設けられたゲート電極層とを有する半導体装置及びその作製に関する。

(もっと読む)

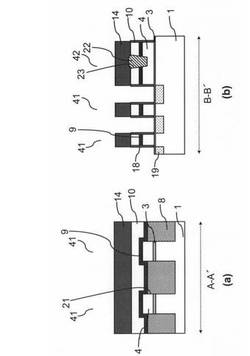

半導体装置及びその製造方法

【課題】NBTIを改善することのできるトランジスタ構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたn型ウェル領域102と、n型ウェル領域102上に形成され、ゲート絶縁膜104と、下部ゲート電極105、及び下部ゲート電極105上に形成された上部ゲート電極106を含むゲート電極120とを有するpチャネル型MISトランジスタとを備える。下部ゲート電極105は、結晶粒界を有する多結晶の金属窒化物で構成されており、当該結晶粒界には金属窒化物を構成する元素とは異なる元素が偏析されている。

(もっと読む)

TFT用銅スパッタリングターゲット材、TFT用銅膜、及びスパッタリング方法

【課題】成膜条件(成膜中の圧力、成膜に用いるガス種等)を変更しなくても、成膜された銅膜中の引張残留応力を低減できるTFT用銅スパッタリングターゲット材、TFT用銅膜、及びスパッタリング方法を提供する。

【解決手段】本発明に係るTFT用銅スパッタリングターゲット材は、銅材からなり、銅と不可避的不純物とからなる無酸素銅、又は銅合金からなるスパッタ面を備え、かつ、(111)面と、(200)面と、(220)面と、(311)面との総和に対する、(111)面の占有割合が、15%以上であるTFT用銅スパッタリングターゲット材である。

(もっと読む)

配線パターンの形成方法

【課題】触媒層の凝集を抑制し、また炭素の拡散性を制御して、欠陥の無いグラファイト膜を形成することができるグラフェン構造を含むグラファイト膜による配線パターンの形成方法の提供。

【解決手段】触媒層の凝集を抑制し、また炭素の拡散速度を適切に速度に調節することができる合金層又は積層体からなる触媒層を利用して、グラフェン構造を有するグラファイト膜で構成された配線パターンの形成方法を提供する。

(もっと読む)

表示装置及びその作製方法

【課題】デジタル階調と時間階調とを組み合わせた駆動方法において、アドレス期間よりも短いサステイン期間を有する場合にも正常に画像(映像)の表示が可能であり、EL駆動用トランジスタが、劣化によりノーマリーオンとなった場合にも、信号線の電位を変えて動作を補償することの出来る画素を提供することを課題とする。

【解決手段】消去用TFT105のソース領域とドレイン領域とは、一方は電流供給線108に接続され、残る一方はゲート信号線106に接続されている。この構造により、EL駆動用TFT102のしきい値のシフトにより、ノーマリーオンとなった場合にも、ゲート信号線106の電位を変えることで、EL駆動用TFT102が確実に非導通状態となるように、EL駆動用TFT102のゲート・ソース間電圧を変えることを可能とする。

(もっと読む)

21 - 40 / 284

[ Back to top ]