Fターム[4M104BB37]の内容

Fターム[4M104BB37]に分類される特許

141 - 160 / 284

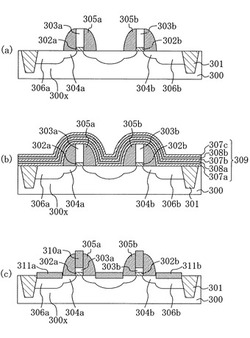

半導体装置及びその製造方法

【課題】高濃度拡散層の上部にシリサイド膜を有する半導体装置において、リーク電流の発生を防止する。

【解決手段】第1のMOSトランジスタは、活性領域300xにおける第1のサイドウォールスペーサ305aの外側方下に形成された第1の高濃度拡散層306aと、第1の高濃度拡散層306aの上部に形成された第1のシリサイド膜311aとを備え、第2のMOSトランジスタは、活性領域300xにおける第2のサイドウォールスペーサ305bの外側方下に形成された第2の高濃度拡散層306bと、第2の高濃度拡散層306bの上部に形成された第2のシリサイド膜311bとを備え、第1のシリサイド膜311a及び第2のシリサイド膜311bを構成する結晶粒の結晶粒径は、第1のサイドウォールスペーサ305aと第2のサイドウォールスペーサ305b間の間隔以下である。

(もっと読む)

ターゲット

【課題】ターゲットの結晶配向の組織を改善し、スパッタリングを実施した際の、膜の均一性(ユニフォーミティ)を良好にし、スパッタ成膜の品質を向上させ、さらに製造歩留まりを著しく向上させることができるスパッタリング用ターゲット及びその製造方法を提供する。

【解決手段】平板状のターゲットにおいて、ターゲット材料の中心面から半分に切断し2枚のターゲットとし、またさらに切断前のターゲット材料の中心面に位置する結晶配向が(222)優先である結晶組織を備えるターゲットを製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、NiSiの潜り込み成長を抑え、オフリーク電流の増加を抑制できる半導体装置を提供することを目的とする。

【解決手段】本発明の1実施形態は、シリコン基板1上に形成されるソース領域及びドレイン領域と、ソース領域とドレイン領域との間にゲート絶縁膜3を介して形成されるゲート領域とを備える半導体装置である。さらに、本発明の1実施形態は、少なくともソース領域及びドレイン領域上に成膜した所定の添加金属を含むニッケル膜10を、Ni2Si膜へと反応させる温度でアニールし、さらにNiSi膜へと反応させる温度でアニールして形成されたシリサイド膜22を備える。

(もっと読む)

半導体装置の製造方法

【課題】素子分離領域に影響を及ぼすことなく、所望のMISトランジスタのチャネル領域に対して選択的に応力を生じさせ且つ記憶させることができる半導体装置を製造できるようにする。

【解決手段】半導体基板11の上に、応力歪み生成膜24を形成し、さらに、第3のレジストパターン25を形成する。第3のレジストパターン25をマスクにして、応力歪み生成膜24に対してプラズマ処理を行うことにより、応力歪み生成膜24における第1の活性領域11aの上側部分を改質して引っ張り応力を生じる引っ張り応力含有部24Aを形成する。次に、第3のレジストパターン25を除去した後、半導体基板11に対して熱処理を行うことにより、引っ張り応力含有部24Aによって、第1の活性領域11aにおけるn型ゲート電極15aの下に位置するチャネル領域に対してゲート長方向に沿った引っ張り応力を生じさせる。

(もっと読む)

太陽電池用電極フィルム、これを用いた太陽電池の製造方法、並びに太陽電池

【課題】シリコン系光電変換素子上に容易に形成することができ、且つ得られる太陽電池に低い全抵抗値及び高い発電効率を付与することができる太陽電池用電極フィルムを提供すること。

【解決手段】透明フィルム、その表面に設けられた透明電極薄膜、及び透明電極薄膜上にストライプ状又はメッシュ状に金属電極からなるシリコン系太陽電池用電極フィルムであって、透明電極薄膜の厚さが10〜400nmの範囲にあり、金属電極の厚さが1〜200μmの範囲にあり、その幅が0.01〜1.0mmの範囲にあることを特徴とする太陽電池用電極フィルム;これを用いた太陽電池の製造方法;及び太陽電池。

(もっと読む)

ジャーマナイド薄膜、ジャーマナイド薄膜の作成方法、ジャーマナイド薄膜を備えたゲルマニウム構造体

【課題】低抵抗かつ熱的安定性に優れた、ジャーマナイド薄膜を提供する。

【解決手段】ゲルマニウム(Ge)基板11上に、Pt薄膜12が形成され、さらにPt薄膜12の上方にNi薄膜13が形成されている。その後、熱処理を加えることによって、Ge基板上にNi、Pt、Geの三元素からなる(Ni1-xPtx)Ge薄膜が形成された。ジャーマナイド薄膜を構成する結晶粒の結晶面方位が、前記ゲルマニウム基板の[110]結晶面に対して、[102]面あるいは[001]面を平行とする配向関係になっている。

(もっと読む)

強誘電体メモリの製造方法

【課題】良好な強誘電体膜を形成する。

【解決手段】本発明の強誘電体メモリの製造方法は、基板上方にイリジウム膜331を形成する工程と、イリジウム膜331上に酸化イリジウム層334を形成する工程と、酸化イリジウム層334を非晶質のイリジウム層336とする工程と、非晶質のイリジウム層336を酸化して、酸化イリジウム部337とする酸化工程と、酸化イリジウム部337上にMOCVD法で強誘電体膜を形成する工程と、強誘電体膜上に電極を形成する工程と、を有する。

(もっと読む)

半導体装置

【課題】ゲート電極と高誘電率ゲート絶縁膜の間に生じる反応を抑制でき、高集積化および高速化に適した素子構造を有する半導体装置を提供する。

【解決手段】絶縁ゲート電界効果トランジスタを有する半導体装置であって、この絶縁ゲート電界効果トランジスタは、高誘電率膜を含むゲート絶縁膜と、第1の導電層およびこの第1の導電層より抵抗率の低い第2の導電層を含む積層構造をもつゲート電極を有し、第1の導電層は、前記高誘電率膜上に接して設けられ、密度5g/cm3以上の窒化チタンからなる半導体装置。

(もっと読む)

積層構造体、磁気又は電子装置およびトランジスタ

【課題】シリコン上へ強磁性相を積層化したスピンエレクトロニクスデバイスを作製するにあたり、強磁性元素の鉄(Fe)から構成されるFe3Si化合物をシリコン系半導体基板上へ結晶成長させる。

【解決手段】この際Fe3Si層の組成制御性の向上および、ハーフメタル構造を有する規則構造相形成のためにSiCからなる半導体基板を使用あるいは表面にSiCを有するシリコン基板上にFe3Si磁性相を形成する。

(もっと読む)

Al−Ni−La−Si系Al合金スパッタリングターゲットおよびその製造方法

【課題】Ni、La、およびSiを含むAl−Ni−La−Si系Al合金スパッタリングターゲットを用いて成膜したときに発生するスプラッシュを低減し得る技術を提供する。

【解決手段】Ni、La、およびSiを含有するAl−Ni−La−Si系Al合金スパッタリングターゲットであって、スパッタリングターゲットの平面に対して垂直な断面における(1/4)t(tは厚み)〜(3/4)tの部位を走査型電子顕微鏡(2000倍)で観察したとき、(1)Al及びNiを主体とするAl−Ni系金属間化合物について、Al−Ni系金属間化合物の全面積に対する平均粒径0.3〜3μmのAl−Ni系金属間化合物の合計面積≧70%であり、(2)Al、Ni、La、およびSiを主体とするAl−Ni−La−Si系金属間化合物について、Al−Ni−La−Si系金属間化合物の全面積に対する平均粒径0.2〜2μmのAl−Ni−La−Si系金属間化合物の合計面積≧70%である。

(もっと読む)

表示装置の作製方法

【課題】電気特性に優れ、信頼性の高い薄膜トランジスタを有する表示装置を生産性よく作製する方法を提案することを課題とする。

【解決手段】ゲート電極上にゲート絶縁膜を形成し、ゲート絶縁膜上に微結晶半導体膜を成膜し、微結晶半導体膜の表面からレーザビームを照射して微結晶半導体膜の結晶性を改善する。次に、結晶性が改善された微結晶半導体膜を用いて薄膜トランジスタを形成する。また当該薄膜トランジスタを有する表示装置を作製する。

(もっと読む)

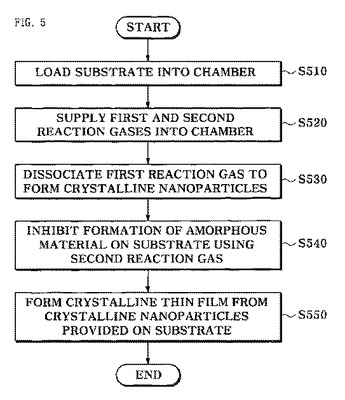

薄膜製造方法及び薄膜製造装置

薄膜製造方法が提供される。基板チャンバ内に提供される。チャンバ内に第1反応ガス及び第2反応ガスが供給される。第1反応ガスが解離されて結晶性ナノ粒子を形成する。第2反応ガスを利用して基板上に非結晶性物質の形成が抑制される。そして、基板上に提供された結晶性ナノ粒子から結晶性薄膜を形成する。  (もっと読む)

(もっと読む)

金属ゲート及び高K誘電体を有する回路構造体

【課題】 高k材料含有ゲート誘電体及び金属含有ゲートを有する回路構造体を提供する。

【解決手段】 高k誘電体のゲート絶縁体及び金属含有ゲートを有するPFETデバイス及びNFETデバイスを備えたFETデバイス構造体が、開示される。両方のNFETデバイス及びPFETデバイスにおけるゲート金属層が、単一の共通の金属層から製造された。単一の共通の金属であるために、デバイスの製造が簡単化され、必要とされるマスクの数が減少する。両方の型のデバイスのゲートのために単一の金属層を用いるさらなる結果として、PFET及びNFETの端子電極を、直接物理的に接触した状態で互いに付き合わせることができる。共通の金属材料を選択すること及び高k誘電体の酸素曝露によって、デバイスの閾値電圧が調整される。閾値は、低消費電力のデバイス動作を目的としている。

(もっと読む)

半導体装置及びその製造方法

半導体装置は、半導体基板上に形成された絶縁膜と、絶縁膜中に形成され、銅又は銅合金からなる埋め込み配線とを備え、絶縁膜と埋め込み配線との間に、白金族元素、又は白金族元素の合金からなるバリアメタル層を有しており、バリアメタル層は、相対的にバリア性が高くなる非晶質度を有する非晶質構造を一部に含んでいる。  (もっと読む)

(もっと読む)

半導体素子およびその製造方法

【課題】MOSトランジスタに十分な応力(ストレス)が加える半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、半導体基板100と、半導体基板100上に備えられたゲート電極114およびゲート電極114の側壁面に備えられたスペーサ116を含むゲート構造物110と、ゲート構造物110の両側の半導体基板100内に形成されたソース/ドレーン領域102と、ゲート構造物110上エッチング停止膜130と、を含み、エッチング停止膜130は、スペーサ116上の第1領域130_1およびゲート電極の上面上の第2領域130_2を含み、第1領域130_1の厚さは、第2領域130_2の厚さの85%以下である。

(もっと読む)

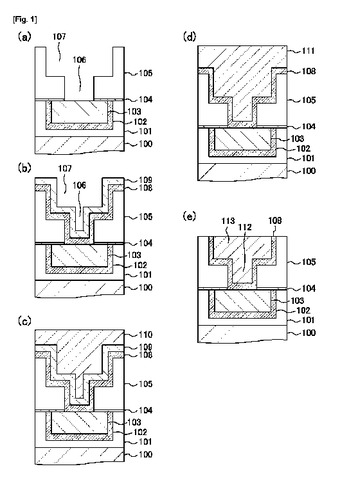

鉄シリサイド強磁性体デバイスの製造方法

【課題】結晶性の良い鉄シリサイド強磁性体Fe3Siを得る。

【解決手段】Si基板1の表面を熱酸化して極薄の酸化膜2を形成する(図(a) 及び(b) 参照)。基板温度を10℃から400℃の範囲の適当な温度に保持した状態で、該酸化膜2の表面にFe3とSi4とをほぼ3:1の蒸着速度比で同時蒸着させる。室温付近の基板温度で蒸着させた場合にはFe3Siのアモルファスが形成され、400℃に近い基板温度で蒸着させた場合には、モノシリサイド(C−FeSi)を含有したFe3Siが形成されるが、いずれの場合にも適正な温度でアニールすれば、鉄シリサイド強磁性体Fe3Siの結晶が得られる。

(もっと読む)

勾配組成を有する最上層を備えた3層バリア層構造

【課題】電子移動の性能を改善しまたリソグラフィープロセスステップを有利にする目的で、バリア層のアルミニウムの{111}含有率を上げる。

【解決手段】IMP技術を用いて(Ti又はTiNX)/TiN/TiNXバリア層を堆積する場合に、Ti又はTiNX である第1層の厚さを約100オングストローム以上、〜約500オングストロームまで(表面形状の幾何関係がこの厚みの上限を制限する)までの範囲に厚くし、TiNの第2層を約100オングストローム以上約800オングストローム以下(好ましくは約600オングストローム以下)の範囲に薄くし、TiNXの第3層の形成を制御してTi含有率が約50原子パーセントチタン(ストイキオメトリック)〜約100原子パーセントチタンとなるようにすることにより、(Ti又はTiNX)/TiN/TiNXバリア層を改良することができる。第1層がTiNXである場合は、Tiの原子パーセントは少なくとも約40パーセントである。

(もっと読む)

半導体装置およびその製造方法

【課題】寄生容量が低く、かつ、熱処理による抵抗値の変動が小さい抵抗素子を有する半導体装置を得ることのできる技術を提供する。

【解決手段】スパッタリングターゲット材料としてタンタルを用い、スパッタリングガスとしてアルゴンと窒素との混合ガスを用いた反応性直流スパッタリング法により、窒化タンタル膜からなる厚さ20nm、窒素濃度30原子%未満の第1抵抗層5a、及び窒化タンタル膜からなる厚さ5nm、窒素濃度30原子%以上の第2抵抗層5bを順次形成した後、第1及び第2抵抗層5a,5bを加工して抵抗素子R1を形成する。窒素濃度が30原子%以上の上部領域を設けることにより、配線工程において熱負荷が与えられても抵抗素子R1の抵抗変動率を1%未満に抑えることができる。

(もっと読む)

半導体装置の製造方法

【課題】サリサイドプロセスで金属シリサイド層を形成した半導体装置の性能を向上させる。

【解決手段】ゲート絶縁膜7、ゲート電極8a,8b、ソース・ドレイン用のn+型半導体領域9b及びp+型半導体領域10bを形成してから、半導体基板1上に金属膜及びバリア膜を形成し、第1の熱処理を行って金属膜とゲート電極8a,8b、n+型半導体領域9bおよびp+型半導体領域10bとを反応させることで、金属膜を構成する金属元素MのモノシリサイドMSiからなる金属シリサイド層41を形成する。その後、バリア膜および未反応の金属膜を除去してから、第2の熱処理を行い金属シリサイド層41を安定化させる。これ以降、半導体基板1の温度が第2の熱処理の熱処理温度よりも高温となるような処理は行わない。第2の熱処理の熱処理温度は、金属元素MのダイシリサイドMSi2の格子サイズと半導体基板1の格子サイズが一致する温度よりも低くする。

(もっと読む)

半導体発光素子

【課題】 発光効率を向上できると共に、順電圧の上昇を抑制可能な半導体発光素子を提供することを目的とする。

【解決手段】 半導体層と、該層上に設けられた透光性の導電性酸化物膜とを有し、導電性酸化物膜は、部分的に柱状構造部を有する半導体発光素子。

(もっと読む)

141 - 160 / 284

[ Back to top ]