Fターム[4M104BB37]の内容

Fターム[4M104BB37]に分類される特許

161 - 180 / 284

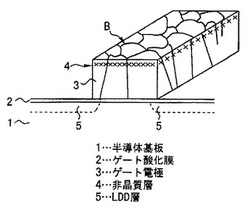

半導体装置の製造方法

【課題】MOS構造の半導体装置において、ゲート電極をイオン注入のチャネリングに対して強い構造とする。

【解決手段】半導体基板上でゲート絶縁膜の上に半導体材料を堆積してゲート電極を形成する。このゲート電極の表面または内部に非晶質層を形成する。その後、ゲートサイドウォールを形成し、ゲート電極およびサイドウォールをマスクとして半導体基板に不純物をイオン注入し、ソース/ドレインを形成する。非晶質層としては、窒素を1×1020〜1×1022/cm3個含む層を形成する。これを、熱処理に対する不純物析出抑制層とし、イオン注入に対するチャネリング防止層とする。

(もっと読む)

半導体装置及びその製造方法

【課題】ニッケル膜又はニッケル合金膜を用いてシリサイド化を行う場合において、シリサイド化されたソース/ドレイン拡散層のシート抵抗及びそのばらつきを低減するとともに、接合リーク電流を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上10に、ゲート電極16とソース/ドレイン拡散層24とを有するトランジスタ26を形成する第1の工程と、半導体基板上に、ゲート電極及びソース/ドレイン拡散層を覆うように、ニッケル又はニッケル合金より成る金属膜28を、基板温度を220℃〜300℃とした状態で形成する第2の工程と、金属膜とソース/ドレイン拡散層の上部とを反応させ、ソース/ドレイン拡散層上に、ニッケルシリサイド又はニッケル合金シリサイドより成るシリサイド膜34bを形成する第3の工程とを有している。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルが薄い場合でもAl配線のモフォロジ及びエレクトロマイグレーションを改善することができる半導体装置の製造方法を得る。

【解決手段】まず、半導体基板11上にSiO2層間膜13(酸化膜)を形成する。次に、SiO2層間膜13上にTi膜18を形成する。次に、Ti膜18上にTiN膜32を形成する。次に、TiN膜32上にAl配線33を形成する。ここで、Ti膜18を形成する工程において、圧力が0.3Pa以下の雰囲気中で物理気相成長法を用いる。これにより、Ti膜18とSiO2層間膜13との間にTiO2膜31が形成される。

(もっと読む)

半導体装置の製造方法および成膜装置

【課題】配向性の高いAl膜を有する半導体装置の製造方法を提供する。また、配向性の高いTi膜を成膜可能な成膜装置を提供する。

【解決手段】スパッタリングを行う成膜室内に、H2ガスを導入してから、または、H2ガスを導入しながら、Ti膜の成膜を行う。成膜中におけるH2ガスの分圧は、1×10−4Pa〜1×10−2Paであることが好ましい。また、Ti膜の成膜は、半導体基板を200℃〜250℃の温度に加熱した状態で行うことが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】反射防止膜としてTiN膜を用いる場合において、アッシング工程にてTiN膜がAl合金配線から剥離するのを抑制できるようにする。

【解決手段】シリコン基板上に形成されるAl合金配線層の反射防止膜としてのTiN膜13f、16fの結晶粒界に充填物質13g、16gを充填する。このようにすれば、Al−Cu膜13c、16cへの酸素(O2)ラジカルの進入を防ぐことが可能となる。従って、酸素(O2)ラジカルとAl−Cu膜13cとが反応してAlxOyが形成されることが防止され、ポリマー除去時にAlxOyがフッ素ラジカルによって還元され、反射防止膜13f、16fがAl−Cu膜13cから剥離することもない。

(もっと読む)

マスク、それによって薄膜トランジスタを形成する方法及び薄膜トランジスタ

【課題】マスク、該マスクで薄膜トランジスタを形成する方法、及び薄膜トランジスタを提供する。

【解決手段】該マスクは、チャンネル領域の半露光マスク構造と、ドレイン電極マスク構造と、ソース電極マスク構造とを備え、前記チャンネル領域の半露光マスク構造は更に、該薄膜トランジスタのチャンネル領域に対応する部分から延在し、且つ該部分の外側に位置するチャンネル領域の外周半露光マスク構造を有する。本発明によって、形成された薄膜トランジスタのソース・ドレイン電極の連結及びチャンネル領域の活性層の切断などの不良を効果的に防止した。

(もっと読む)

トランジスタ、集積回路および集積回路形成方法

【課題】トランジスタ、集積回路、および、集積回路形成方法を提供する。

【解決手段】半導体基板1内に形成されたゲート溝27内にゲート誘電体24を介してゲート電極23が配置された構成を有する。該ゲート電極23は、導電性炭素材を有している。

(もっと読む)

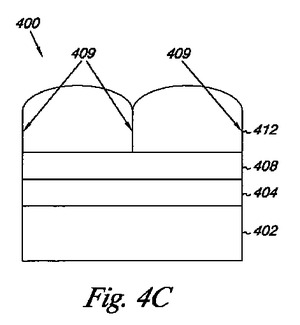

タングステンディジット線、その形成方法及び動作方法

タングステンディジット線を使用するための、及び、形成するための、方法、デバイス、及び、システムが記載されている。本開示の実施例に従って形成されたタングステンディジット線は、窒化タングステン(WNX)基板(402)上のタングステン(W)単分子層(404)と、W単分子層上のホウ素(B)単分子層(308)と、B単分子層上のバルクW層(412)とで形成されうる。バルクW層は、100nmから600nmの間の粒子サイズを有する。ディジット線は50nm未満の幅となりえる。従って、ディジット線のキャパシタンス及び抵抗は減少する。  (もっと読む)

(もっと読む)

フリンジ電界の電荷注入のための電極構造

【課題】電子機器の半導体材料に改良された電荷注入を備える新規電極構造を提供する。

【解決手段】半導体デバイスは、半導体材料及び半導体材料に電気的に接続された電極構造を備える。電極構造は、第1の導体材料で形成された第1の部分及び第2の導体材料で形成された第2の部分を有する。電極構造の第1の部分及び第2の部分の両方は、半導体材料と直接的に接触している。第1の導体材料は、第1の仕事関数を有し、第2の導体材料は、第1の仕事関数と異なる第2の仕事関数を有する。電極構造の第2の部分は、第1の部分と共に接合部点を形成する。電極構造の第1の部分及び第2の部分は、第1の導体材料と第2の半導体材料との間の接合部の端部からフリンジ電界が半導体材料中へ広がるように配置される。

(もっと読む)

有機薄膜トランジスタ、有機薄膜トランジスタの製造方法

【課題】性能のバラツキが少なく温度による性能劣化が少ない有機薄膜トランジスタ、有機薄膜トランジスタの製造方法を提供する。

【解決手段】基板の上に、少なくともゲート電極、ゲート絶縁層、ソース電極、ドレイン電極及び有機半導体層を有する有機薄膜トランジスタにおいて、ソース電極またはドレイン電極のうち少なくとも一つの表面は無機導電材料の多孔質膜であり、多孔質膜は有機導電材料または有機半導体材料を含浸していることを特徴とする。

(もっと読む)

圧電体素子及びその製造方法

【課題】本発明は、分極疲労を抑制した圧電体素子およびその製造方法の提供を目的とする。

【解決手段】本発明の圧電体素子は、一対の対向する主面を有する基板と、その基板の一方の主面上に配置した下部電極層と、その下部電極層上に配置した圧電体層と、その圧電体層上に配置した上部電極層とを有しており、下部電極層はニッケル酸ランタン系セラミックスからなる。

(もっと読む)

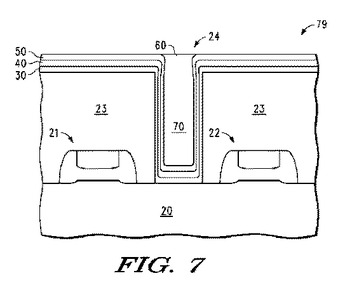

ボイドの無いコンタクトプラグ

コンタクトプラグを形成する半導体素子形成プロセスでは、チタンまたはタンタルコンタクト層(30)、窒化チタンバリア層(40)、及びタングステンシード層をコンタクト開口部(24)に順番に堆積させる。次に、コンタクトホール(24)への充填を、コンタクト開口部の底面から上に向かって、銅層(60)を電気メッキすることにより行なって、ボイドがコンタクト開口部(24)内に形成されることがないようにする。全ての余分な材料をCMPプロセスにより除去してコンタクトプラグ(70)を形成し、この場合、CMPプロセスを使用して、コンタクト層/シード層/バリア層(30,40,50)のうちの一つ以上の層を薄くする、または除去することもできる。  (もっと読む)

(もっと読む)

配線及び記憶素子の作製方法

【課題】焼成を必要とする液滴吐出法をはじめとする塗布法において、配線や導電膜の作製時における焼成温度を低減することを課題とする。

【解決手段】液滴吐出法等の塗布法を用いて導電性材料よりなるナノ粒子が分散された組成物を吐出し、その後乾燥することで該溶媒を気化させる。そして、活性酸素による前処理を行った後、焼成を行うことで、配線もしくは導電膜を作製する。このように、焼成前に活性酸素による前処理を行うことで、作製時における焼成温度を低減することが可能となる。

(もっと読む)

金属化合物膜、その形成方法および金属化合物膜形成用基体

【課題】半導体素子の透明電極などに利用可能な、導電性の高い金属化合物膜と、その簡便な製造方法を提供する。

【解決手段】結晶構造を有する酸化亜鉛などからなる金属化合物粒子1を含む粒子分散液をシリコン基板2に塗布し、金属化合物粒子を、基板平面方向にC軸配向する粒子が含まれるように基板に付着させる。この上に同じ金属化合物粒子を含む液を塗布し、付着した金属化合物粒子を核として結晶成長させる。焼成処理をして基板平面方向にC軸配向した金属化合物膜3の結晶粒を得る。

(もっと読む)

半導体装置およびその製造方法

【課題】製造方法の煩雑化を抑制し、ばらつきを抑え、適切なしきい値およびゲート電極の空乏化の抑制を実現可能にする。

【解決手段】p型半導体基板2と、p型半導体基板に離間して形成された第1ソース領域6aおよび第1ドレイン領域6bと、第1ソース領域および第1ドレイン領域との間のp型半導体基板上に形成された第1ゲート絶縁膜11と、第1ゲート絶縁膜上に形成され、母相が多結晶シリコン15aであり、その結晶粒界と第1ゲート絶縁膜との界面の少なくとも第1原子層15cに真空仕事関数がシリコンのミッドギャップより小さい金属状態の第1金属元素を含有する第1ゲート電極15と、を有するnチャネルMISFETと、を備えている。

(もっと読む)

電界効果型半導体装置及びその製造方法

【課題】 電界効果型半導体装置及びその製造方法に関し、ゲート絶縁膜にダメージを与えることなく、少なくとも窒素を含有するとともにシリコンを主成分とする膜を組成制御性良く構成する。

【解決手段】 シリコンと、シリコンに対して5〜30原子数%の窒素を含有する導電膜をゲート電極3の少なくとも一部として用いる。

(もっと読む)

無電解めっき用膜状触媒組成物

【課題】本発明は、被めっき物に対し、ナノメートルレベルの平滑さを有するめっき被膜を実現することを可能にする無電解めっき用膜状触媒組成物を提供することを目的とする。

【解決手段】被めっき表面に金属ガラスからなる平滑な薄膜状の触媒層を形成する。この膜状の金属ガラスからなる触媒層は、無電解めっき反応において、従来の純金属の単結晶粒子と同等以上の触媒活性を示す。また、この触媒層は、従来の純金属の単結晶粒子と異なり、均一性が高く粒界が存在しないため、ナノメートルレベルの平滑さを備えるめっきを実現することができる。

(もっと読む)

金属膜形成方法及び該方法により得られる金属膜

【課題】加熱のみで膜形成した場合に比べ、電気抵抗を大幅に低減した金属膜を得る。

【解決手段】金属コロイド粒子が金属粒子と粒子表面に配位修飾した保護剤とにより構成され、保護剤が分子中に窒素又は酸素のいずれか一方又はその双方を含む炭素骨格を有し、かつ窒素、酸素、窒素を含む原子団及び酸素を含む原子団からなる群より選ばれた1種又は2種以上をアンカーとして金属粒子表面に配位修飾した構造を有し、保護剤がハイドロキシアルキル基を分子構造に含み、金属コロイド粒子を水系又は非水系のいずれか一方の分散媒又はその双方を混合した分散媒に所定の割合で混合して分散させた金属コロイドを基材表面に塗布する工程と、基材を自然乾燥させて金属コロイド中の分散媒を除去する工程と、基材を室温〜200℃の温度に保持しながら、濃度が、5〜200g/Nm3のオゾンを照射し、基材表面に金属膜を形成する工程とを含む。

(もっと読む)

絶縁膜積層体、絶縁膜積層体の製造方法、半導体装置及び半導体装置の製造方法

【課題】ボロン漏れの抑制とリーク電流増加の抑制とを同時に実現可能な、絶縁膜及びこの絶縁膜を備えた半導体装置と、絶縁膜の製造方法及び半導体装置の製造方法を提供する。

【解決手段】微結晶組織からなるハフニウム含有窒化シリコン酸化物層3aと、非晶質組織からなるハフニウム含有窒化シリコン酸化物層3bとが半導体基板2上に積層されてなる積層膜からなり、積層膜の窒素濃度が15原子%以上40原子%以下の範囲であることを特徴とする半導体装置用の絶縁膜積層体3を採用する。

(もっと読む)

161 - 180 / 284

[ Back to top ]