Fターム[4M104CC00]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574)

Fターム[4M104CC00]の下位に属するFターム

オーミック接触電極 (3,853)

ショットキー接触電極 (1,047)

MISゲート電極 (3,643)

Fターム[4M104CC00]に分類される特許

21 - 31 / 31

半導体装置

【課題】オン抵抗の低減や耐圧の向上が図れる半導体装置を提供する。

【解決手段】第1の絶縁層と、第1の絶縁層の上に設けられた半導体層と、半導体層に選択的に設けられた第1の半導体領域と、第1の半導体領域に対して離間して半導体層に選択的に設けられた第2の半導体領域と、第1の半導体領域に接して設けられた第1の主電極と、第2の半導体領域に接して設けられた第2の主電極と、半導体層の上に設けられた第2の絶縁層と、半導体層における第1の半導体領域と第2の半導体領域との間の部分の上方の第2の絶縁層中に設けられた第1の導電材と、第1の導電材に対向する部分の半導体層に設けられたトレンチ内に設けられ、第1の導電材に接し、かつ前記第1の絶縁層に達する第2の導電材とを備えている。

(もっと読む)

半導体装置

【課題】高い終端耐圧が得られる半導体装置を提供する。

【解決手段】素子領域及びこの素子領域の外側の終端領域における第1の第1導電型半導体層の主面上に設けられた第2の第1導電型半導体層と、第1の第1導電型半導体層の主面に対して略平行な横方向に第2の第1導電型半導体層と共に周期的配列構造を形成する第3の第2導電型半導体層と、終端領域における第2の第1導電型半導体層及び第3の第2導電型半導体層の上に設けられたフィールド絶縁膜と、フィールド絶縁膜上に設けられ第2の主電極もしくは制御電極に接続されたフィールドプレート電極と、絶縁膜を介在させてフィールドプレート電極に一部が重なって、フィールドプレート電極よりも外側のフィールド絶縁膜上に設けられ、電位が浮遊したフローティングフィールドプレート電極とを備えている。

(もっと読む)

半導体装置

【課題】

FLR構造を有する半導体装置において、特性変動のばらつきの小さい半導体装置を提供する。

【解決手段】

半導体基板7に形成されたNベース領域9と、半導体基板7の第1主面側において、半導体基板7に形成されたPウェル領域P(0)と、半導体基板7の第1主面側において、Pウェル領域を囲むように形成された複数のPリング領域P(1)〜P(n)と、半導体基板7の第1主面側において、Pリング領域を囲むように形成されたNストッパ領域SRと、半導体基板の第1主面の上において、隣り合うPリング領域の間に設けられた(酸化膜2と、酸化膜2の上に配置されたポリシリコン3と、Pリング領域及びポリシリコン3に電気的接続されるように配置されたアルミニウム4と、半導体基板7の第1主面とは反対側の第2主面に設けられた電極11、とを備える。

(もっと読む)

高電圧GaNトランジスタ

【課題】より高い破壊電圧およびより低いオン抵抗を含み、高周波数において十分に機能するパワースイッチングデバイスを提供する。

【解決手段】多重フィールドプレートトランジスタが、活性領域、ならびにソース、ドレイン、およびゲートを含む。第1のスペーサ層が、活性領域の上方でソースとゲートの間にあり、第2のスペーサ層が、活性領域の上方でドレインとゲートの間にある。第1のスペーサ層上の第1のフィールドプレート、及び第2のスペーサ層上の第2のフィールドプレートが、ゲートに接続される。第3のスペーサ層が、第1のスペーサ層、第2のスペーサ層、第1のフィールドプレート、ゲート、および第2のフィールドプレート上にあり、第3のフィールドプレートが、第3のスペーサ層上にあり、ソースに接続される。

(もっと読む)

不揮発性記憶素子およびその製造方法

【課題】不揮発性記憶素子は同一ホール内に多層膜を埋め込むので微細化や高速化が難しい。また、多層膜の埋め込みに特化したプロセスやプロセス条件が必要となる。

【解決手段】半導体プロセスと親和性のあるプロセスを用いて、層間絶縁膜23と層間絶縁膜25のそれぞれを貫通したコンタクトホール内に下部電極27と上部電極28を形成し、可変抵抗膜24を上記両電極で挟み込むことで記憶部29を形成する。この記憶部29は低誘電率の層間絶縁膜で周りを取り囲まれている。さらに、本発明のクロスポイント型の不揮発性記憶素子20は、素子構造上CMOSプロセス等との親和性もよいので、集積化と高速化に適している。

(もっと読む)

MOSトランジスタおよびその製造方法

本発明のMOSトランジスタ(1)は、ゲート電極(10)、チャネル領域(4)、ドレインコンタクト領域(6)、および、前記チャネル領域(4)と前記ドレインコンタクト領域(6)とを相互に接続するドレイン拡張領域(7)を具える。前記MOSトランジスタ(1)は、前記ドレイン拡張領域(7)の上方に延在するシールド層(11)をさらに具える。このシールド層(11)と前記ドレイン拡張領域(7)との間の距離は、前記ゲート電極(10)から前記ドレインコンタクト領域(6)へ向かう方向に増加する。このような方法で、前記MOSトランジスタ(1)の横方向破壊電圧は、MOSトランジスタが基地局アプリケーションにおいて用いられるものよりも高い供給電圧のためのブロードキャストアプリケーションの耐久性要求を満足することができるレベルまで増加する。  (もっと読む)

(もっと読む)

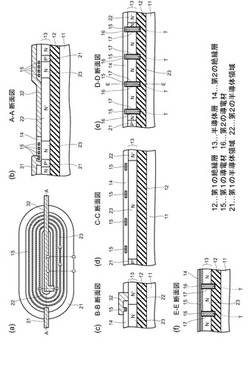

半導体装置および半導体装置の製造方法

【課題】SOI基板を用いることなく、絶縁体上に配置された電界効果型トランジスタ下にバックゲート電極を形成する。

【解決手段】半導体基板11上に第1半導体層12および第2半導体層13を形成した後、第1半導体層12をエッチング除去することで半導体基板11と第2半導体層13との間に空洞部20を形成し、半導体基板11および第2半導体層13の熱酸化を行うことにより、半導体基板11と第2半導体層13との間の空洞部20内の上下面に絶縁膜21を形成してから、空洞部20内に埋め込み導電体層30を形成する。

(もっと読む)

集積回路装置の製造方法

【課題】 リソグラフィー技術の限界以上に微細化した配線構造を持つ集積回路装置製造

方法の提供。

【解決手段】 複数の下地電極配線13が形成された下地表面上に絶縁体膜12を形成する工程と、絶縁体膜12に、下地電極配線13と交差する複数の溝25を形成して下地表面を露出させる工程と、溝中に下地電極配線13に電気接続する複数の素子11を形成する工程と、下地電極配線に電位を付与しつつカーボンナノチューブからなる配線30を溝中に化学気相成長により形成することを特徴とする集積回路装置の製造方法。

(もっと読む)

半導体装置

【課題】 LOCOSオフセット構造を採らなくても、トランジスタの耐圧が高い半導体装置の提供を提供する。

【解決手段】 MOSトランジスタ100のゲート電極11とドレインプラグ17との間のシリコン基板1上に、絶縁膜7を介して電界集中緩和用のスポットプラグ19が設けられており、このスポットプラグ19は、ゲート電極21の上方まで延ばされたソース電極21に接続している。このような構成であれば、ゲート電極11下とドレイン領域5との境界部分は、スポットプラグの影響を受けて電界集中が緩和され、その勾配が緩やかになる。

(もっと読む)

MRAMデバイスの磁気エレクトロニクス素子を覆う導電層への接触方法

誘電領域を覆う記憶素子層を形成する工程を含む磁気エレクトロニクス素子を覆う導電層への接触方法。第1導電層(26)が記憶素子層(18)を覆うように成長する。第1誘電層(28)が第1導電層(26)を覆うように成長し、第1マスキング層(28)を形成するためにパターン化およびエッチング処理される。第1マスキング層(28)を用いて第1導電層(26)がエッチング処理される。第2誘電層(36)が第1マスキング層(28)及び誘電領域を覆うように成長する。第1マスキング層(28)を露出させるために第2誘電層(36)の一部が除去される。第1マスキング層(28)が第2誘電層(36)に比べて早い速度でエッチング処理されるように、第2誘電層(36)及び第1マスキング層(28)が化学エッチング処理される。このエッチング処理により第1導電層(26)が露出する。  (もっと読む)

(もっと読む)

炭化珪素半導体装置

【課題】製造工程が簡単であり、高い耐圧保持機能を有する耐圧構造を備えた炭化珪素半導体装置を提供する。

【解決手段】n+ 型の炭化珪素からなる炭化珪素基板領域11と、炭化珪素基板領域11の上に形成されたn−型のカソード領域12と、カソード領域12における炭化珪素基板領域11との接合界面に対向する一主面に接しているアノード電極13と、炭化珪素基板領域11の裏面に形成されたカソード電極14と、アノード電極13の外周に接し、且つ環状をなすように配置されたエッジ保護領域16と、アノード電極13並びにエッジ保護領域16と同心円状に、且つ互いに接しないように環状に配置された複数の電界緩和領域17とが形成されている。

(もっと読む)

21 - 31 / 31

[ Back to top ]