Fターム[4M104CC00]の内容

半導体の電極 (138,591) | 電極の種類(発明部分) (8,574)

Fターム[4M104CC00]の下位に属するFターム

オーミック接触電極 (3,853)

ショットキー接触電極 (1,047)

MISゲート電極 (3,643)

Fターム[4M104CC00]に分類される特許

1 - 20 / 31

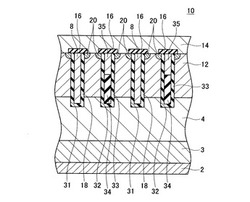

半導体装置

【課題】半導体装置の寄生容量成分を好適に調整する。

【解決手段】半導体装置10は、複数個のエミッタ領域20を備える。半導体層の表面から所定の深さまでの領域に形成されているボディ領域12を備える。ボディ領域12の下部に形成されているドリフト領域4を備える。ドリフト領域4の下部に形成されているコレクタ領域3を備える。各エミッタ領域20の表面からボディ領域12を貫通して伸びている第1トレンチ31を備える。第1トレンチ31の内面を覆っているゲート絶縁膜18を備える。第1トレンチ31内に収容されているゲート電極8を備える。隣接している第1トレンチ31間に形成され、ボディ領域12を貫通して伸びている第2トレンチ32を備える。第2トレンチ32の内面を覆っているトレンチ絶縁膜33を備える。第2トレンチ32内に収容されている導電層35を備える。導電層35がゲート電極8に電気的に接続されている。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】制御性の良い製造方法のみで形成することができる高周波数動作が可能なノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】ソース電極5とドレイン電極6との間の電子供給層4上に、電子供給層4とショットキー接触する浮遊電極8を配置し、この浮遊電極8上に絶縁膜を介してゲート電極7を配置する。さらに、ソース電極5とドレイン電極6との間の電子供給層表面を珪素膜11で被覆する。そして、ゲート電極7に正バイアス印加し、浮遊電極8に電子を蓄積される。

(もっと読む)

半導体装置

【課題】低オン抵抗と高破壊耐量との両立が可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、第1の主電極と、第1の半導体層と、第1導電形ベース層と、第2導電形ベース層と、第1導電形の第2の半導体層と、第2導電形の埋め込み層と、埋め込み電極と、ゲート絶縁膜と、ゲート電極と、第2の主電極とを備えた。埋め込み層は、第1導電形ベース層中に選択的に設けられた。埋め込み電極は、第2導電形ベース層を貫通して埋め込み層に達するトレンチの底部に設けられ、埋め込み層に接する。ゲート絶縁膜は、埋め込み電極より上のトレンチの側壁に設けられた。ゲート電極は、トレンチ内におけるゲート絶縁膜の内側に設けられた。第2の主電極は、第2の半導体層上に設けられ、第2の半導体層及び埋め込み電極と電気的に接続された。

(もっと読む)

半導体装置の製造方法及び基板処理装置

【課題】 低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】 表面に金属膜が形成された基板を処理容器内に搬入する工程と、処理容器内に原料ガスと酸化源とを供給し排気することで、基板の表面に形成された金属膜上に所定膜厚の金属酸化膜を形成する処理を行う工程と、処理済基板を処理容器内から搬出する工程と、を有し、処理を行う工程では、酸化源としてオゾンガス、酸素ガスまたはプラズマにより活性化された酸素ガスを用い、所定膜厚の金属酸化膜を形成する過程において形成される金属酸化膜越しに、酸化源に含まれる酸素原子を、金属膜の表面に導入することで、金属膜の表面を酸化して導電性の金属酸化層に改質する。

(もっと読む)

半導体装置

【課題】ゲートパッド電極と裏面金属電極間のリーク電流を抑制し、ボンディング強度を向上させ、高性能化・高信頼化を図る。

【解決手段】基板10の第1表面上に配置され、それぞれ複数のフィンガーを有するゲート電極24・ソース電極20およびドレイン電極22およびオーム性電極層18と、ゲート電極・ソース電極およびドレイン電極ごとに複数のフィンガーをそれぞれ束ねて形成したゲート端子電極GE1〜4・ソース端子電極SE1〜4およびドレイン端子電極DEと、オーム性電極層上に配置され、ゲート端子電極と接続するゲートパッド電極30と、オーム性電極層と基板との界面に形成された反応層を覆うように基板内に形成された第1導電型半導体層16と、第1導電型半導体層16を覆うように、基板内に形成され、第1導電型と反対導電型の第2導電型半導体層とを備える半導体装置1。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】トランジスタの閾値電圧を高くする。

【解決手段】フローティング電極110は半導体層102上に形成されており、絶縁層はフローティング電極110上に形成されている。バイアス電極134は、絶縁層を介してフローティング電極110の一部に対向することにより、フローティング電極110と容量結合し、かつフローティング電極110が半導体層102にチャネル領域を形成しない大きさの電圧が印加される。制御電極132は、絶縁層を介してフローティング電極110の他の部分に対向することにより、フローティング電極110と容量結合し、かつトランジスタのオン/オフを制御するための制御電圧が入力される。

(もっと読む)

Pチャネル型パワーMOSFET

【課題】PチャネルパワーMOSFETにおいて、同手法に従い、トレンチ内にP+ポリシリコンゲート電極とP+フィールドプレート電極を有するトレンチ内ダブルゲート型PチャネルパワーMOSFETを製作して、種々の特性を測定したところ、高温状態で、基板に対してゲートに負のバイアスを印加し続けると、PチャネルパワーMOSFETの閾値電圧の絶対値がストレス印加時間と共に次第に大きくなってゆく現象があることが明らかとなった。

【解決手段】本願の一つの発明は、N型ポリシリコン線状フィールドプレート電極およびN型ポリシリコン線状ゲート電極を各トレンチ部に有するPチャネル型パワーMOSFETである。

(もっと読む)

半導体装置

【課題】ソースフィールドプレート電極を形成することによる性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】SiC基板11上にGaN層12およびAlGaN層13がこの順で形成され、AlGaN層13上にドレイン電極14、ソース電極15およびゲート電極16が形成された半導体装置であって、ゲート電極16の下方には、SiC基板11を貫通するように第1の開口23が形成されている。さらに、GaN層12上に形成され、ソース電極15に接続されるソースパッド19の一部が、SiC基板11の裏面側から露出するように、第2の開口24が形成されている。そして、第1の開口23内にソースフィールドプレート電極25−1を形成すると同時に、第2の開口24から露出するソースパッド19に接触するようにSiC基板11の裏面に接地導体25−2を形成する。

(もっと読む)

スパッタリングターゲットとそれを用いたTa−W合金膜および液晶表示装置

【課題】Ta−W系スパッタリングターゲットにおいて、面内の抵抗ばらつきが小さいと共に、下地膜との密着力に優れたTa−W合金膜を再現性よく得ることを可能にする。

【解決手段】Ta−W系スパッタリングターゲットは、0.05〜2質量%の範囲のWを含有し、残部が実質的にTaからなると共に、ターゲット全体としてのW含有量のばらつきが±20%以内とされている。このようなTa−W系スパッタリングターゲットを用いて成膜したTa−W合金膜は、例えばTFD素子1の第1の電極3に適用される。TFD素子1は第1の電極3/陽極酸化膜4/第2の電極5によるMIM構造を有し、液晶表示装置のスイッチング素子等に適用される。

(もっと読む)

半導体装置

【課題】高電圧が印加される金属電極による耐圧低下を緩和する半導体装置を提供する。

【解決手段】高電位島領域101内のn-半導体層3とp-半導体基板1との界面にはn+埋め込み不純物領域2が形成されている。n+埋め込み不純物領域2の上方ではn-半導体層3表面にpチャネルMOSFET130が形成されている。p+不純物領域6及びn+不純物領域45を有するダイオード102が、領域105内のn-半導体層3表面に形成されている。n+不純物領域45に接続された金属電極14は、p+不純物領域6及びp+不純物領域4の上方を通ってpチャネルMOSFET130に接続される。p+不純物領域6に接続されたp-不純物領域61は金属電極14の下方に位置している。p-半導体基板1及びp+不純物領域4は、p+不純物領域6及びn+不純物領域45よりも低い電位が与えられる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置において、導電性バッファ層を用いることなく、煩雑なプロセスも必要なく、非常に高い深さ精度のドライエッチングも必要なく、また、結晶性を劣化させずに、効率良くホールを引き抜くことができるようにする。

【解決手段】半導体装置を、同一基板1上に形成され、(0001)面及び(000−1)面を有する窒化物半導体層4と、基板1と窒化物半導体層4との間に部分的に設けられた(0001)面形成層2と、(0001)面を有する窒化物半導体層4上に設けられたソース電極5、ドレイン電極6及びゲート電極7と、(000−1)面を有する窒化物半導体層4上に設けられたホール引き抜き電極8とを備えるものとする。

(もっと読む)

半導体ダイ上に製造されるパワートランジスタデバイス

【課題】パワー半導体デバイス構造と、高電圧トランジスタを製造するためのプロセスとを提供する。

【解決手段】パワートランジスタデバイスは基板を含み、当該基板は、上に重なっているバッファ層とのPN接合を形成する。パワートランジスタデバイスはさらに、第1の領域と、バッファ層の上面に隣接するドリフト領域と、ボディ領域とを含む。ボディ領域は、ドリフト領域から第1の領域を分離する。第1および第2の誘電体領域は、それぞれ、ドリフト領域における対向する横方向側壁部分に隣接する。誘電体領域は、少なくともボディ領域の下から下方に垂直方向に延在して少なくともバッファ層に達する。第1および第2のフィールドプレートは、それぞれ、第1および第2の誘電体領域に配置される。順方向導通を制御するトレンチゲートは、ボディ領域に隣接し、当該ボディ領域から絶縁された誘電体領域の上方に配置される。

(もっと読む)

縦型半導体装置及びその製造方法

【課題】素子終端領域の占有面積を小さくして阻止特性の安定性を確保でき、必要に応じて、順方向/逆方向の電圧阻止能力を実現できる縦型半導体装置を提供する。

【解決手段】縦型半導体装置は、IGBTの素子機能を実現する素子活性領域100と、素子活性領域100を囲む素子終端領域200とによって構成されている。素子終端領域200には、基板表面に略垂直に、素子活性領域100を取り囲む閉ループ状にトレンチ700が形成されている。トレンチ700は、その側壁に形成されたシリコン酸化膜710と、酸化膜間の隙間を充填する多結晶シリコン720とによって形成されている。さらに、素子終端領域200は、トレンチ700と所定距離を隔てたp−型低不純物濃度層500で終端されている。これによって、素子終端領域200の占有面積を大幅に低減するトレンチ構造において、薄膜の低応力な酸化膜を形成して高耐圧化を図ることができる。

(もっと読む)

半導体装置

【課題】素子の高耐圧化に伴い反転領域を介して流れるリーク電流を低減する方法の提供。

【解決手段】所望の不純物濃度を有する半導体層を備えた半導体基板と、半導体層内に形成された複数のストライプ状のトレンチ内にゲート酸化膜を介して導電体層を埋め込み形成したトレンチゲートと、半導体層表面を覆う絶縁膜と、絶縁膜を貫通し、ソースコンタクト開口部に形成されたソース電極と、半導体層内に形成され、ソース電極に電気的に接続されたボディ領域及びソース領域と、トレンチゲート周縁部でトレンチゲートに接続されたゲート周辺配線と、ソース電極と同一表面上で、ソース電極から離間して形成され、ゲート周辺配線に接続されるゲート電極と、ドレイン電極とを具備し、周縁部のスクライブ領域の拡散領域と、デバイス周縁部の拡散領域との間の半導体基板表面に、チャネルストッパ1csを形成し、反転領域形成を抑制する。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体層の素子分離される部分に溝を形成する際に内在する応力が開放されても、その応力によりフィールドプレート部が絶縁膜から剥離するのを防止でき、高耐圧化を可能にした半導体素子及びその製造方法を提供する。

【解決手段】HFET10は、電子供給層14上に形成されたソース電極16、ドレイン電極17およびゲート電極18と、各電極間を絶縁する絶縁膜19と、半導体層22の素子分離される部分に形成されたメサ構造23を有する。ゲート電極18は、ショットキー電極の機能を有する第1の電極層20と、絶縁膜19との接触部が絶縁膜19に密着する金属材料で構成されたフィールドプレート部21aを有する第2の電極層21と、を有する。メサ構造23を形成する際に内在する応力が開放されても、その応力によりゲート電極18のフィールドプレート部21aが絶縁膜19から剥離するのを防止でき、高耐圧化が可能になる。

(もっと読む)

キャパシタ用電極及びその製造方法、キャパシタ

【課題】仕事関数値が高く、熱耐性がある低抵抗なキャパシタ用電極を提供する。

【解決手段】互いに対向する第1面及び第2面を有するキャパシタ用電極であって、酸素原子及び窒素原子を含有し、厚み方向における第1面と第2面の間に酸素原子の濃度が最大値を示す位置Aを有し、窒素原子は位置Aよりも第1面側にのみ存在することを特徴とする、キャパシタ用電極。

(もっと読む)

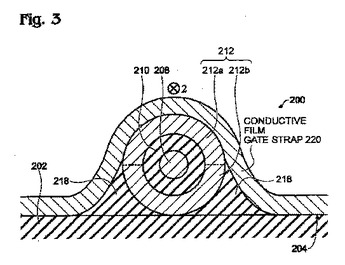

コア−シェル−シェル・ナノワイヤトランジスタ、およびその製造方法

コア−シェル−シェル(CSS)ナノワイヤトランジスタ(NWT)であって、表面を持つ基板と、半導体コアと、該半導体コアを囲む絶縁性シェルと、該絶縁性シェルを囲む導電性シェルとを含む円柱形のCSSナノ構造体であって、上記表面上にある下側半円柱を有するCSSナノ構造体と、上記CSSナノ構造体の中央部にある上記導電性シェルから形成されているゲート電極と、上記基板の表面と、上記CSSナノ構造体の中央部にある上記下側半円柱との間に配置された絶縁性凹形ストリンガと、上記CSSナノ構造体の中央部にある、ゲート電極および上記絶縁性凹形ストリンガの上に形成されている導電膜ゲートストラップと、上記CSSナノ構造体の両端部にある、上記半導体コアの複数の露出領域に形成されているソース/ドレイン(S/D)領域と、を含むコア−シェル−シェル(CSS)ナノワイヤトランジスタ(NWT)。  (もっと読む)

(もっと読む)

半導体装置

【課題】ストライプ型のSJ構造のドリフト層であっても、両方向の電位分布の差を生じさせず安定した耐圧を確保できる半導体装置を提供する。

【解決手段】半導体装置は、半導体素子が形成される素子領域100及びその素子領域100を囲う終端領域200を有する。半導体装置は、n型ドリフト層4内にその平面と平行なY軸方向を長手方向としてストライプ状に且つY軸方向と直交するX軸方向において周期的に形成されたp型ピラー1と、終端領域200において素子領域100を取り囲むように同心環状に形成された複数のフィールドプレート電極2とを備える。p型ピラー層1におけるY軸方向の端部は、素子領域100と終端領域200の境界を超えて形成されている。フィールドプレート電極200は、p型ピラー層1のY軸方向の両端近傍を通るように形成されている。

(もっと読む)

スイッチング素子

【課題】スイッチング素子の動作電圧を低下させる。

【解決手段】スイッチング素子100において、絶縁性基板10と、絶縁性基板10の一面に設けられた第1電極20及び第2電極30と、第1電極20と第2電極30との間に設けられ、第1電極20と第2電極30との間への所定電圧の印加により抵抗のスイッチング現象が生じる間隙を有する電極間間隙部40と、を備え、絶縁性基板10の当該一面に窒素を含有させるよう構成した。

(もっと読む)

1 - 20 / 31

[ Back to top ]