Fターム[4M104DD15]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | コンタクトホール又は電極析出部の形成 (4,254) | 孔開け、又は除去する絶縁膜の材料 (2,744)

Fターム[4M104DD15]の下位に属するFターム

Fターム[4M104DD15]に分類される特許

1 - 20 / 226

半導体装置およびその製造方法

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Cu配線内における空孔の集中を抑制することでCu配線内でのボイドの形成を抑え、例えば2層間配線系におけるビア接続部等における、いわゆるストレスマイグレーションと呼ばれる断線等の配線不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法において、配線形成後に被処理基板を加熱および除熱する熱サイクル工程を行う、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】結晶欠陥の発生を抑え、デバイスのリーク電流の発生、耐圧低下、しきい値電圧の継時変化、およびショートチャネル効果を抑制することが可能な半導体装置を提供すること。

【解決手段】単結晶AlNからなる基板を準備するステップと、前記単結晶AlNからなる基板の表面を酸素プラズマによって酸化し、単結晶AlNからなる基板上に酸化アルミニウムまたはアルミニウムオキシナイトライドからなる絶縁膜を形成するステップとを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

化合物半導体装置の製造方法

【課題】化合物半導体積層構造上の絶縁膜に所期の微細な開口を形成するも、リーク電流を抑止した信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2上にパッシベーション膜6を形成し、パッシベーション膜6の電極形成予定位置をドライエッチングにより薄化し、パッシベーション膜6の薄化された部位6aをウェットエッチングにより貫通して開口6bを形成し、この開口6bを電極材料で埋め込むように、パッシベーション膜6上にゲート電極7を形成する。

(もっと読む)

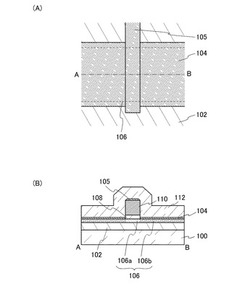

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲートリーク電流が低減され、かつ、ノーマリーオフ動作する半導体装置を提供する。

【解決手段】基板11の上に形成された第1の半導体層12と、第1の半導体層12の上に形成された第2の半導体層13と、第2の半導体層13の上に形成された下部絶縁膜31と、下部絶縁膜31の上に、p型の導電性を有する酸化物により形成された酸化物膜33と、酸化物膜33の上に形成された上部絶縁膜34と、上部絶縁膜34の上に形成されたゲート電極41と、を有し、ゲート電極41の直下において、下部絶縁膜31の表面には凹部が形成されている半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、デバイス特性の劣化(化学的・物理的変化)を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】本発明による化合物半導体装置では、化合物半導体層2上を均質な同一材料(ここではSiN)からなり誘電率が一様な第1の保護膜6が覆い、第1の保護膜6の開口6aの一端部分に酸素を含有する保護部、ここでは当該一端部分を覆う酸化膜である第2の保護膜7aが形成されており、開口6aを埋め込み第2の保護膜7aを包含するオーバーハング形状のゲート電極8が形成される。

(もっと読む)

1 - 20 / 226

[ Back to top ]