Fターム[4M104DD21]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098)

Fターム[4M104DD21]の下位に属するFターム

Fターム[4M104DD21]に分類される特許

21 - 40 / 199

成膜方法及び半導体装置の製造方法

【課題】ポリイミド膜に対して高い密着性を有するコバルト膜を成膜する方法を提供する。

【解決手段】成膜装置100の処理容器1内で、処理容器1内にCOガスを導入しながら、ポリイミド膜81が形成されたウエハWを110℃以上400℃以下の温度で加熱し、ポリイミド膜81を熱処理する。熱処理によって、ポリイミド膜81中の分子が熱分解し、膜密度が減少するとともに、表面粗度が大きくなる。その後、処理容器1内に成膜原料であるCo2(CO)8を導入してCVD法によりポリイミド膜81上にコバルト膜83を堆積させる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】炭化珪素半導体層に設けられたリセス底部の不純物領域を含む終端構造の形成において、リセスの底端部に発生したノッチを除去あるいは緩やかな形状にする。

【解決手段】ガードリング6の形成領域のSiCドリフト層2にリセス7を形成したとき、リセス7の底端部に尖ったノッチ11が現れる。リセス7の形成後、リセス7の内部を含むSiCドリフト層2の表面を熱酸化して酸化層12を形成し、当該酸化層12をエッチングにより除去すると、ノッチ11は緩やかな形状になる。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

半導体製造方法および半導体装置

【課題】ウェーハテスト後のウェーハ状態において所望の回路を印刷処理により容易に形成することが可能な半導体製造方法および半導体装置を提供することを課題する。

【解決手段】本発明に係る半導体製造方法は、ウェーハの被描画パターン形成領域に所定の深さを有する溝部を形成する工程、ウェーハに対してトリミング要否の検査を行う工程、前記ウェーハにおけるトリミング必要なウェーハの前記溝部に導電性溶剤を射出し描画パターンを描画する工程、描画パターンを描画した後、脱気および低温アニールする工程、脱気および低温アニールした成膜後、当該成膜表面を平坦化する工程、および平坦化した後、高温アニールする工程、を有する。

(もっと読む)

窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子

【課題】リーク電流が低減された、耐圧性が高い窒化物系化合物半導体素子の製造方法および窒化物系化合物半導体素子を提供すること。

【解決手段】基板上に少なくともガリウム原子を含むIII族原子と窒素原子とからなる窒化物系化合物半導体層をエピタキシャル成長する成長工程と、素子構造形成前に、前記窒化物系化合物半導体層にレーザ光または電離放射線を照射し、前記窒化物系化合物半導体層中のIII族空孔と水素原子との複合体を分解する分解工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】金属半導体化合物電極の界面抵抗を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態によればn型半導体上に硫黄を含有する硫黄含有膜を堆積し、硫黄含有膜上に第1の金属を含有する第1の金属膜を堆積し、熱処理によりn型半導体と第1の金属膜を反応させて金属半導体化合物膜を形成するとともに、n型半導体と金属半導体化合物膜との界面に硫黄を導入することを特徴とする半導体装置の製造方法である。

(もっと読む)

配線形成方法、及び配線

【課題】カーボンナノチューブを用いて、高精細な配線を、簡単に、かつ生産性良く形成できる半導体装置の製造方法を提供する。

【解決手段】エアロゾルジェット手段により、カーボンナノチューブ含有分散液を、基板3上にエアロゾル状態にて吹き付け、電極1に接続するカーボンナノチューブからなる配線2を形成する。配線はカーボンナノチューブがネットワーク状に絡み合った構造になっているので導電性が高い。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

タンタルチューブとPIT炭素芯の製造方法、タンタルチューブとPIT炭素芯、タンタル炭化物配線の製造方法及びタンタル炭化物配線

【課題】簡易な方法で、所定の形状のタンタルと炭素との固相拡散接合を可能とし更に、タンタルと炭素の固相拡散接合を行う場所以外のタンタル表面に炭化物を形成する方法を提供する。

【解決手段】タンタル若しくはタンタル合金をチューブ状の形状に加工し、チューブの中に炭素粉末を圧入し、その後、チューブをコイル形状に加工した後に真空熱処理炉内に設置し、タンタル若しくはタンタル合金表面に形成されている自然酸化膜であるTa2O5を除去した後、タンタル若しくはタンタル合金チューブ内面と前記炭素粉末PITを固相拡散結合で分子接合させるとともに、前記真空熱処理炉内に炭素源を導入してタンタル若しくはタンタル合金チューブの外表面に炭素を侵入させてTaCを形成する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の内壁に絶縁膜を形成することにより、接続孔の径を小さくする場合において、接続孔内に導電膜を十分に埋め込むことができるようにする。

【解決手段】接続孔210,220の内壁上に絶縁性の第1膜300を形成し、接続孔210,220の径を細らせる。次いで、第1膜300が形成された接続孔210,220内に、第2膜50を埋め込む。次いで、絶縁膜200の表層を、CMP法を用いて除去する。次いで、接続孔210,220から第2膜50を除去する。次いで、接続孔210,220の第1膜300上および接続孔210,220の底面上にバリアメタル膜330を形成し、さらに接続孔210,220内に導電膜からなるコンタクト310,320を埋め込む。

(もっと読む)

ショットキーバリアダイオード及びその製造方法

【課題】バリア金属層のカバレッジを向上させることができ、さらに、トレンチ内に埋め込まれた導電体に応力が集中する虞がなく、逆方向電流(IR)を抑制することができるショットキーバリアダイオード(SBD)及びその製造方法を提供する。

【解決手段】本発明のSBD11は、シリコン基板2の表面2aにトレンチ3が形成され、トレンチ3の内面に最上面12aが傾斜面22とされた絶縁膜12が形成され、このトレンチ3内には、最上端部21aがトレンチ3の側壁上面3aより下方に位置するように導電体13が埋め込まれ、シリコン基板2の表面2a、絶縁膜12及び導電体13を覆うようにバリア金属層14及び電極金属層15が積層されている。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】不純物ドープを用いることなく、低温プロセスでオーミック電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】n+型基板1の表面側に素子構造や表面電極を形成した後、n+型基板1の裏面1bにアモルファス層12を形成する。そして、アモルファス層12が形成された裏面1b上に金属薄膜110を形成した後、n+型基板1の裏面1b側に光子エネルギーとレーザ出力の積が1000eV・mJ/cm2以上かつ8000eV・mJ/cm2以下となるような条件でレーザ光を照射することでシリサイド層111を含むドレイン電極11を形成する。これにより、n+型基板1に高温処理を行うことなく、n+型基板1にドレイン電極11にシリサイド層111を生成できる。したがって、不純物ドープ層を用いることなく、かつ低温プロセスによってドレイン電極11をオーミック電極にできる。

(もっと読む)

窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させた、窒化物系半導体装置を提供することを目的とする。

【解決手段】ドレイン電極26とゲート電極28との間に設けられたSBD金属電極30がAlGaN層20とショットキー接合されている。また、SBD金属電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、SBD金属電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、SBD金属電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu系合金配線膜と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに密着性に優れた配線構造を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記半導体層と前記Cu合金層との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、前記(N、C、F、O)層を構成する窒素、炭素、フッ素および酸素のいずれかの元素は前記半導体層のSiと結合しており、前記Cu合金層は、Cu−X合金層(第一層)と第二層とを含む積層構造である。

(もっと読む)

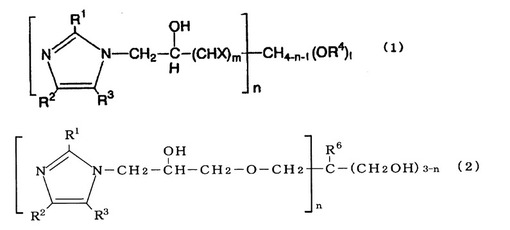

無電解めっき前処理剤

【課題】スルーホールへのめっき性に優れる無電解めっき前処理剤を提供する。

【解決手段】下記一般式(1)及び(2)で表されるイミダゾールアルコール化合物の1種又は2種以上と、パラジウム化合物とを含有する無電解めっき前処理剤。 (もっと読む)

(もっと読む)

ヘテロ接合障壁領域を含む半導体デバイス及びその製造方法

半導体装置の製造方法、及び半導体装置

【課題】シリコン基板の裏面側に形成する裏面電極の反り量、及びオン抵抗値を改善可能な半導体装置、及びその製造方法を提供すること。

【解決手段】シリコン基板2の表面側に表面電極6、裏面側にP型不純物拡散層とそれに当接された裏面電極7を有し、表面電極6と裏面電極7の間に電流を流すように構成された縦型の半導体素子を備える。P型不純物拡散層の表面をウエットエッチングしてP型不純物拡散層のシリコン単結晶面を出し、シリコン基板2が120℃以下の温度で、シリコン基板2の裏面に裏面電極7を形成する。裏面電極7のうち、少なくともシリコン単結晶面と当接する面には、仕事関数が4.5eV以上の金属層を配設する。シリコン単結晶面と仕事関数が4.5eV以上の金属層が接触した接合面であることにより、熱処理無しでオーミック接合の抵抗値を良好に保つことができる。

(もっと読む)

パターン形成方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等のパターンを作製する方法、さらには、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜、良好なマスクパターン、及びコンタクトホールを形成する方法を提案し、更には低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】本発明の一は、膜上にぬれ性の低い1のマスクパターンを形成した後、第1のマスクパターンを介して、膜上にぬれ性の高い材料を塗布又は吐出して第2のマスクパターンを形成し、第1のマスクパターンを除去して、第2のマスクパターンをマスクとして第1の膜の一部を除去する。

(もっと読む)

発光装置及び発光装置の作製方法

【課題】発光装置の信頼性を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路用トランジスタを含む駆動回路部と、画素用トランジスタを含む画素部とを有する発光装置であり、駆動回路用トランジスタ及び画素用トランジスタは、酸化物絶縁層と一部接する酸化物半導体層を含む逆スタガ型のトランジスタである。画素部において酸化物絶縁層上にカラーフィルタ層と発光素子が設けられ、駆動回路用トランジスタにおいて、酸化物絶縁層上にゲート電極層及び酸化物半導体層と重なる導電層が設けられる。なお、ゲート電極層、ソース電極層及びドレイン電極層は金属導電膜を用いる。

(もっと読む)

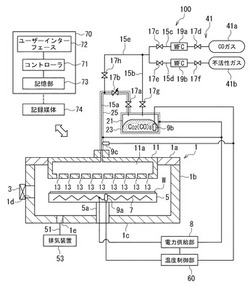

真空加熱装置及び基板処理システム

【課題】基板に均一性高い加熱処理を行う一方で、高い真空度が得られる真空加熱装置を提供すること。

【解決手段】本発明の真空加熱装置は、気密な処理容器と、この処理容器内に基板を載置するために設けられたアルミニウム合金からなる載置台と、この載置台を支持し、その内部に用力線路部材が大気側から挿入されているステンレス鋼からなる筒状の支持部材と、この支持部材と処理容器との間を気密にするための有機物からなるシール部材と、前記載置台を加熱するための加熱部と、前記処理容器内を真空排気するための真空排気手段と、を備えている。これによって載置台の熱が支持部材を介してシール部材に伝熱し難くなっており、シール部材の昇温が抑えられ、大気側から大気成分がシール部材を通って処理容器内へ侵入することが抑えられる。

(もっと読む)

21 - 40 / 199

[ Back to top ]