Fターム[4M104DD21]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 析出面の前処理 (2,098)

Fターム[4M104DD21]の下位に属するFターム

Fターム[4M104DD21]に分類される特許

41 - 60 / 199

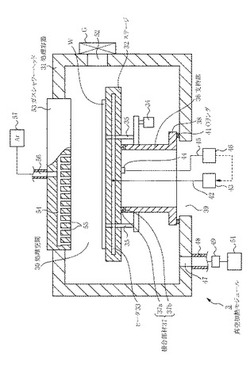

真空加熱装置及び基板処理システム

【課題】基板に均一性高い加熱処理を行う一方で、高い真空度が得られる真空加熱装置を提供すること。

【解決手段】本発明の真空加熱装置は、気密な処理容器と、この処理容器内に基板を載置するために設けられたアルミニウム合金からなる載置台と、この載置台を支持し、その内部に用力線路部材が大気側から挿入されているステンレス鋼からなる筒状の支持部材と、この支持部材と処理容器との間を気密にするための有機物からなるシール部材と、前記載置台を加熱するための加熱部と、前記処理容器内を真空排気するための真空排気手段と、を備えている。これによって載置台の熱が支持部材を介してシール部材に伝熱し難くなっており、シール部材の昇温が抑えられ、大気側から大気成分がシール部材を通って処理容器内へ侵入することが抑えられる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】製造コストの増加を抑制しつつ、SiC基板の一方面に直接接合されるメタル層の接続信頼性を向上でき、さらにはSiC基板に対するメタル層のオーミック接合を確保することのできる半導体装置およびその製造方法を提供すること。

【解決手段】SiC基板2を有する半導体装置1において、SiC基板2の裏面22側の表層部分に、表面21側の表層部分よりもカーボンが高濃度に含まれる高カーボン濃度SiC層3を形成する。そして、その高カーボン濃度SiC層3の表面にドレイン電極17を直接接合する。

(もっと読む)

カーボン・ナノチューブを選択的に成長させる方法

【課題】1つ以上のカーボン・ナノチューブを選択的に成長させる方法を提供する。

【解決手段】本方法は、上面を有する絶縁層を基板上に形成するステップと、絶縁層内にビアを形成するステップと、ビアの側壁及び底面を含め、絶縁層上に活性金属層を形成するステップと、ビアの内部での1つ以上のカーボン・ナノチューブの選択的な成長を可能にするために、イオン・ビームを用いて上面の部分にある活性金属層を除去するステップとを含む。

(もっと読む)

リフトオフ法を用いたパターン形成方法

【課題】本発明は、リフトオフ法を用いたパターン形成方法を実施したとしても、導電性パターンのエッジ付近にバリが発生することがない、リフトオフ法を用いたパターン形成方法を提供する。

【解決手段】本発明では、まず、導電性パターン6のエッジ部が位置するウエハ基板1の表面内に、溝2を形成する。次に、溝2が露出する開口部3aを有するレジスト3を、ウエハ基板1上に形成する。次に、開口部3aから露出するウエハ基板1上とレジスト3上とに、導電性膜5を形成する。そして、レジスト3を除去することにより、ウエハ基板1上に導電性パターン6を形成する。

(もっと読む)

金属酸化物膜の形成方法及び成膜装置

【課題】 セルフリミットを発生させるような金属酸化物であっても、その膜厚を制御することが可能となる金属酸化物膜の形成方法を提供すること。

【解決手段】 下地の温度が金属酸化物膜の成膜温度に達する前に、金属原料ガスを下地の表面に供給する工程(1)と、下地の温度を成膜温度以上とし、下地の表面に供給された金属原料ガスと下地の表面の残留水分とを反応させて、下地上に金属酸化物膜を形成する工程(2)と、を具備する。

(もっと読む)

半導体製造方法

【課題】基板面内で均一な膜厚形成を実現すること

【解決手段】この半導体製造方法は、複数の基板に連続してめっき処理を施す半導体製造方法であって、1枚の基板処理に必要なpH調整剤を含む所定量のめっき液を温度調節用容器に収容し、温度調節用容器に収容しためっき液を、めっき処理に必要なめっき成膜速度およびめっき液に含まれるpH調整剤の濃度に応じた所定の温度に調節し、基板を1枚ずつ所定位置に保持し、めっき処理に必要なめっき成膜速度およびめっき液に含まれるpH調整剤の濃度に応じたタイミングで、保持された基板1枚毎に温度調節用容器に収容され温度調節されためっき液全量を、保持された基板の処理面に吐出することを特徴とする。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】凹凸の大きいステップバンチングに対しても平坦化可能で、かつ平坦化にあたりCMP研磨などの研磨工程を必要としない炭化珪素半導体装置の製造方法を提供することを目的とする。

【解決手段】炭化珪素基板の表面上に、活性領域となり表面にステップバンチングが生じやすいC/Si比を有する第1の炭化珪素層を形成する第1工程と、前記第1の炭化珪素層の表面上に、表面が平坦となるC/Si比を有する第2の炭化珪素層を形成する第2工程と、前記第2の炭化珪素層をエッチング除去する第3工程とを備えている。

(もっと読む)

光電変換デバイス、その製造方法および製造装置ならびに隔壁材料

【課題】光電変換デバイスの表面に高アスペクト比の配線を容易に形成する。

【解決手段】基板W表面を走査移動する第1吐出部52から、光硬化性樹脂を有する隔壁材料A1を吐出し、その後方でUV光を照射することにより硬化させる。さらに後方を移動する第2吐出部54から配線材料を吐出させる。このとき、配線材料の吐出位置の周縁部には隔壁B1,B2が形成されているので、配線材料は面方向に広がることがなく、高アスペクト比の配線CWを形成することができる。隔壁B1,B2については、封止材と同等の屈折率を有する材料を使い配線とともに封止するか、光照射により半硬化状態として配線形成後に熱処理により揮発させる。

(もっと読む)

半導体装置及び配線

【課題】低抵抗の電極や配線を有する半導体装置を実現する。

【解決手段】本実施形態による配線は、p型不純物が導入されたp型不純物層部分と、n型不純物が導入されたn型不純物層部分と、p型及びn型不純物が導入された(p+n)型不純物層部分と、を含む半導体層と、少なくとも(p+n)型不純物層部分上に形成されたシリサイド層と、を備え、(p+n)型不純物層部分に含まれるp型不純物とn型不純物の総濃度は、5E20cm−3未満である。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に高抵抗領域及び低抵抗領域を有するバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層の低抵抗領域を介して接触するように薄膜トランジスタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】最新の0.15μmパワーMOSFETにおいては、微細化によるセル・ピッチの縮小のためトレンチ部(ソース・コンタクト用の溝)において、アルミニウム・ボイド(アルミニウム系電極内に形成されるボイド)が多発することが、本願発明者らによって明らかにされた。この欠陥の発生は、主にアスペクト比が前世代の0.84から一挙に2.8に上昇したことによると考えられる。

【解決手段】本願の一つの発明は、アスペクト比の大きい繰り返し溝等の凹部をアルミニウム系メタルで埋め込む際に、アルミニウム系メタル・シード膜の形成から埋め込みに至るまで、イオン化スパッタリングにより、実行するものである。

(もっと読む)

酸化亜鉛系半導体素子の製造方法

【目的】

p型ZnO系化合物半導体の電極の剥離や金属の凝集が生じず高い接着性を有するとともに良好なオーミック接触を有するコンタクト電極の形成方法及び当該電極が形成されたZnO系化合物半導体素子の製造方法を提供する。

【解決手段】

基板上にn型ZnO系半導体層及びp型ZnO系半導体層を含む積層体をp型ZnO系半導体層が表面に形成されるように形成する工程と、p型ZnO系半導体層をその表面温度が250℃ないし500℃の範囲内で熱処理する工程と、550℃未満の温度で、p型ZnO系半導体層上にp側電極金属を上記熱処理の後に形成する工程と、n型n型ZnO系半導体層上にn側電極金属を形成してZnO系半導体素子を形成する工程と、からなる。

(もっと読む)

半導体素子の製造方法及び半導体素子、並びに半導体装置

【課題】オーミック特性に優れた電極を形成することができるとともに、素子特性に優れる半導体素子が歩留まり良く得られる半導体素子の製造方法及び半導体素子、並びに半導体装置を提供する。

【解決手段】少なくとも、主面2a及び裏面2bを有する第1導電型の炭化珪素バルク基板2の主面2a側に半導体素子構造3を形成する半導体素子構造形成工程と、炭化珪素バルク基板2の裏面2b側に炭化珪素バルク基板2とオーミック接触するオーミック電極4を形成するオーミック電極形成工程とをこの順で具備し、オーミック電極形成工程は、炭化珪素バルク基板2の裏面2b側を研削することによって炭化珪素バルク基板2の厚みを薄くした後、裏面2bにオーミック電極4を形成する小工程と、オーミック電極4に対し、炭化珪素バルク基板2の裏面2b側から高出力光を照射する光学式加熱法によって熱処理を行なう小工程とをこの順で備えている。

(もっと読む)

カーボンナノチューブ及びその製造方法

【課題】 CoWP上でのカーボンナノチューブ作製方法を提供する。

【解決手段】 本発明のカーボンナノチューブ配線構造の製造方法は、Cu配線上のCoを含むめっき層をプラズマ処理するプラズマ処理工程と、前記プラズマ処理工程の前又は後に前記Coを含むめっき層に、カーボンナノチューブ成長用の助触媒を付与する助触媒付与工程と、前記プラズマ処理工程及び助触媒付与工程より後に前記Coを含むめっき層及び前記Coを含むめっき層に付与された前記助触媒を加熱処理する加熱処理工程と、前記加熱処理工程より後に、プラズマCVD法によるカーボンナノチューブ成長工程とを備えたことを特徴とする。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】生産効率の高い薄膜トランジスタ及びその製造方法を提供することにある。

【解決手段】基板上に、少なくともゲート電極、酸化物半導体層、ソース電極及びドレイン電極を有する薄膜トランジスタの製造方法において、前記酸化物半導体層の上に流動性電極材料反撥性を有する撥液パターンを形成後、前記撥液パターンを挟み近接する領域に、流動性電極材料を供給して前記流動性電極材料を前記撥液パターンで分断することにより、前記流動性電極材料からなるソース電極及びドレイン電極を形成することを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

トランジスタにおいて進歩したシリサイド形成と組み合わされる凹型のドレイン及びソース区域

【解決手段】

洗練されたトランジスタ要素を形成するための製造プロセスの間、それぞれの金属シリサイド領域を形成するのに先立つ共通のエッチングシーケンスにおいて、ゲート高さが減少させられてよく、そして凹型のドレイン及びソース構造もまた得られてよい。対応する側壁スペーサ構造はエッチングシーケンスの間に維持され得るので、ゲート電極におけるシリサイド化プロセスの可制御性及び均一性を高めることができ、それにより、低減された程度のスレッショルドばらつきを得ることができる。更に、凹型のドレイン及びソース構造が、全体的な直列抵抗の低減及び応力転移効率の増大をもたらすことができる。

(もっと読む)

半導体集積回路装置の製造方法および半導体集積回路装置の製造装置

【課題】本願発明者らによると、VLSI(Very Large Scale Integration)のウエハ・プロセスにおいて、以下のような問題があることが明らかとなった。すなわち、プリ・メタル(Premetal)工程のタングステン・プラグ形成の準備工程としてのバリア・メタル・スパッタリング成膜時や第1層メタル配線層のスパッタリング成膜時に、ウエハからの脱ガスによる水分に起因する異物の発生がみられる。

【解決手段】本願発明は半導体集積回路装置の製造工程におけるプラズマ・プロセスで、プロセス・チャンバ外に設けられたアンテナにより、プラズマから発生する電磁波を受信することで、同チャンバ内の水分をインサイチュー・モニタ(In Situ Monitor)するものである。

(もっと読む)

半導体装置の作製方法

【課題】絶縁膜中にコンタクトホールを形成せずに、絶縁膜の表面と裏面の間に導電領域を形成することを課題とする。

【解決手段】基板上の半導体素子及び第1の電極上に絶縁膜を形成し、絶縁膜中に第1の加速電圧で第1のイオンを添加して、絶縁膜中の第1の深さに第1の欠陥の多い領域を形成し、第1の加速電圧とは異なる第2の加速電圧で、第2のイオンを添加して、絶縁膜中の第1の深さとは異なる第2の深さに第2の欠陥の多い領域を形成し、第1及び第2の欠陥の多い領域上に、金属元素を含む導電材料を形成し、第1及び第2の欠陥の多い領域のうちの上方の領域から下方の領域に、金属元素を拡散させることにより、絶縁膜中に、第1の電極と、金属元素を含む導電材料とを電気的に接続する導電領域を形成する半導体装置の作製方法に関する。

(もっと読む)

41 - 60 / 199

[ Back to top ]