Fターム[4M104DD34]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | 蒸着 (925)

Fターム[4M104DD34]に分類される特許

1 - 20 / 925

半導体装置

層選択レーザーアブレーションパターニング

トランジスタ、表示装置および電子機器

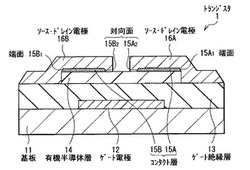

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

成膜装置及び成膜方法

【課題】アルカリ金属又はアルカリ土類金属を含む材料の薄膜を成膜する際において、生産性を低下させず且つ安全にメンテナンスを行うことができる成膜装置及び成膜方法を提供する。

【解決手段】処理室と、処理室内を真空にする真空排気手段と、処理室内に設けられ、成膜材料を放出するための手段と、成膜材料を放出するための手段に対向して設けられた基板支持手段と、一方の面が処理室の内壁と対向し、且つ熱伝導性を有する領域であり、他方の面が熱伝導性を有する領域に接して設けられた酸化物を含む領域である、防着板と、を備えている成膜装置である。そして、当該成膜装置を用いた成膜方法である。

(もっと読む)

蒸着装置

【課題】本発明は、簡易な方法でペレットがインゴット上を転がることを防止できる蒸着装置を提供することを目的とする。

【解決手段】本願の発明に係る蒸着装置は、蒸着材料で形成されたインゴットと、該インゴットの上に供給され、該インゴットと同一材料で形成された複数のペレットと、該インゴットと同一材料で形成され、該複数のペレットが該インゴットの上を転がらないように該複数のペレットを囲う固定用ペレットと、を備えたことを特徴とする。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

紫外線透過ゲート電極を有する電界効果トランジスタ

【課題】基板の自由度があり、待機時(光非照射時)の電力消費が小さく、また光照射時のS/Nが大きい受光素子を提供することである。

【解決手段】紫外線が透過する材料をFETの電極として用い、また、電子走行領域をAlGaNとGaNとのヘテロ界面等のGaN系膜同士のヘテロ界面とする。

(もっと読む)

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体装置

【課題】耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体装置10は、ソース領域12a、複数の帯状のドレイン領域12b、チャネル領域、ソース電極16、ドレイン電極15、およびゲート電極17を具備する。ソース領域12aは、化合物半導体層11上に形成された平面状の領域である。複数の帯状のドレイン領域12bは、化合物半導体層11上に、互いに電気的に分離されるように形成される。チャネル領域は、ソース領域12aの一辺に接し、かつソース領域12aと複数のドレイン領域12bとの間に、互いに電気的に分離されるように形成される。ソース電極16は、ソース領域12a上の少なくとも一部に形成される。ドレイン電極15は、複数のドレイン領域12bに電気的に接続されるように形成される。ゲート電極17は、複数のチャネル領域に電気的に接続されるように形成される。

(もっと読む)

熱処理方法

【課題】シリサイドの横方向への異常成長を防止しつつ、シリサイド形成を行うことができる熱処理方法を提供する。

【解決手段】半導体ウェハーWのソース・ドレイン領域にシリコンなどのイオンを注入し、そのイオン注入領域150を非晶質化する。非晶質化されたイオン注入領域150にニッケル膜158を成膜する。ニッケル膜158が成膜された半導体ウェハーWにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで1ミリ秒以上20ミリ秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーWの表面温度を目標温度T2から±25℃以内の範囲内に1ミリ秒以上100ミリ秒以下維持する。これにより、ニッケルシリサイドが縦方向に優先的に成長する。

(もっと読む)

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

半導体装置

【課題】低コンタクト抵抗を実現し得る半導体基板上の半導体層と電極配線層とのオーミック電極構造を提供する。

【解決手段】半導体基板106と、半導体基板106上に形成された第1のバリア層107と、第1のバリア層107上に形成された厚さ1nm以上40nm以下のチャネル層108と、チャネル層108の上に形成された第2のバリア層102と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第1の電極領域109と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第2の電極領域109とを備える半導体装置であって、少なくとも第1の電極領域109は、チャネル層108と接触する側の面が凹凸形状で構成されている。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

低順方向電圧降下過渡電圧サプレッサーおよび製造方法

【課題】一般にショットキー整流器は定格逆電圧での逆漏れが高く、一方PN構造ダイオードは逆漏れがすくない。両者を並列接続し、低順方向電圧降下を与えると共に、両端で逆サージを保護する。

【解決手段】低逆電圧定格化PNダイオード、および独立集積回路素子におけるPNダイオードに電気的に並列接続した高逆電圧定格化ショットキー整流器からなる低順方向電圧降下過渡電圧サプレッサー。

(もっと読む)

半導体装置およびその製造方法

【課題】閾値電圧を制度良く制御することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

1 - 20 / 925

[ Back to top ]