Fターム[4M104DD35]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537) | ビームによるもの (209)

Fターム[4M104DD35]の下位に属するFターム

イオンプレーティング、イオンビーム蒸着 (97)

Fターム[4M104DD35]に分類される特許

1 - 20 / 112

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

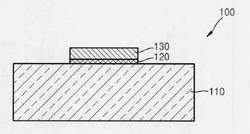

グラフェンを含む電極構造体及び電界効果トランジスタ

【課題】グラフェンを含む電極構造体及び電界効果トランジスタを提供する。

【解決手段】半導体層上のグラフェンと、グラフェン上の電極メタルと、を備え、該グラフェンは、半導体層と直接的に接触し、電極メタルは、グラフェンと直接的に接触する電極構造体である。半導体層は、シリコン、ゲルマニウム、シリコン・ゲルマニウム、III−V族半導体、及びII−VI族半導体を含むグループから選択された一つで形成される。グラフェンは、単層または二層のグラフェンで形成される。

(もっと読む)

窒化物系発光素子及びその製造方法

【課題】窒化物系発光素子及びその製造方法を提供する。

【解決手段】窒素物系発光素子は、基板110、n型クラッド層130、活性層140、

p型クラッド層150、格子セル層160及びオーミック接触層が順次に積層された構造

よりなっている。また格子セル層160は導電性を有する素材で30μm以下の大きさを

有する粒子型セルがオーミック接触層内に埋め込まれて、相互離隔されて形成されている

発光素子である。このような窒素物系発光素子とその製造方法は、p型クラッド層とのオ

ーミック接触特性が改善されているため発光効率及び素子寿命を向上させ、かつウェーハ

成長後の活性化工程を省略できて、製造工程を単純化させうる。

(もっと読む)

トップエミット型窒化物系発光素子

【課題】 優れた電気的特性を有するトップエミット型窒化物系発光素子を提供する。

【解決手段】 本発明は、トップエミット型窒化物系発光素子に関し、窒化物系発光素子は、n型クラッド層、活性層及びp型クラッド層が順次に積層されており、p型クラッド層上に形成された導電性ナノ相酸化物粒子と、p型クラッド層及び導電性ナノ相酸化物粒子層上に形成された透明導電性薄膜層と、を備え、透明導電性薄膜層は透明導電性素材で形成され、導電性ナノ相酸化物粒子は界面改質層が熱処理によってナノ相酸化物に分解されることにより形成される。このようなトップエミット型窒化物系発光素子によれば、p型クラッド層とのオーミック接触特性が改善され、発光素子のパッケージングの際に、ワイヤーボンディング効率及び収率を高めることができ、低い非接触抵抗及び優れた電流−電圧特性により素子の発光効率及び素子寿命を向上することができる。

(もっと読む)

電極被覆材料、電極構造体、及び、半導体装置

【課題】低いコンタクト抵抗、高い移動度を達成し得る半導体装置を提供する。

【解決手段】ゲート電極13、ゲート絶縁層14、有機半導体材料層から構成されたチャネル形成領域16、及び、金属から成るソース/ドレイン電極15を有する電界効果型トランジスタから成る半導体装置において、チャネル形成領域16を構成する有機半導体材料層と接するソース/ドレイン電極15の部分は、電極被覆材料21で被覆されており、電極被覆材料21は、金属イオンと結合し得る官能基、及び、金属から成るソース/ドレイン電極15と結合する官能基を有する有機分子から成る。

(もっと読む)

ナノギャップ電極及びその製造方法

【課題】導電性膜を作製してから、導電性膜に通電しナノギャップを作製するプロセスを行うことなく、エレクトロマイグレーション時の大幅な印加電流の低減とプロセス時間の短縮することができるナノギャップ電極の製造方法を提供する。

【解決手段】絶縁体基板70上に金属電極80,81を形成し、この金属電極間にエレクトロマイグレーションを誘発する電圧又は電流を印加しながら、絶縁体基板上に導電性材料を堆積して、ナノスケールのギャップを有する導電性細線を形成する。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

窒化物半導体発光素子およびその製造方法

【課題】窒化物半導体発光素子の電流拡散効率を向上させるとともに、コンタクト抵抗をも低減でき、大きな駆動電流密度においても発光均一性と高い光出力を得ながら、動作電圧を低減させる得る窒化物半導体発光素子およびその製造方法を提供する。

【解決手段】基板の同一面側にn側およびp側電極パッドが形成された窒化物半導体発光素子であって、p側電極パッド(およびn側電極パッド)から枝状に延伸された延長部を形成し、それによって発光素子中の電流分布を改善する電極構造の窒化物半導体発光素子において、n側およびp側のシート抵抗がいずれも充分に低い場合に、p型窒化物半導体層上に形成された透光性導電膜からなる電流拡散層のシート抵抗を一定条件下において高くすることにより、p型窒化物半導体層と電流拡散層とのコンタクト抵抗を低減し、且つ、シート抵抗の面内分布がより均一になり、光出力も向上する。

(もっと読む)

半導体装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する半導体装置、及び該半導体

装置を量産高く作製する方法を提案することを課題とする。

【解決手段】半導体層としてIn、Ga、及びZnを含む酸化物半導体膜を用い、半導体

層とソース電極層及びドレイン電極層との間にバッファ層が設けられた逆スタガ型(ボト

ムゲート構造)の薄膜トランジスタを含むことを要旨とする。ソース電極層及びドレイン

電極層と半導体層との間に、半導体層よりもキャリア濃度の高いバッファ層を意図的に設

けることによってオーミック性のコンタクトを形成する。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

トップゲート型薄膜トランジスタ及びこれを備えた表示装置

【課題】酸化物半導体層のチャネル領域の、水素拡散による低抵抗化を抑制するトップゲート型酸化物半導体TFT及びこれを備えた表示装置を提供する。

【解決手段】基板の上に、ソース電極層と、ドレイン電極層と、酸化物半導体層と、ゲート絶縁層と、In、Ga、Zn、Snの少なくとも1種類の元素を含むアモルファス酸化物半導体からなるゲート電極層と、水素を含む保護層と、を有し、ゲート絶縁層は酸化物半導体層のチャネル領域の上に形成され、ゲート電極層はゲート絶縁層の上に形成され、保護層はゲート電極層の上に形成されていることを特徴とするトップゲート型薄膜トランジスタ。

(もっと読む)

電界効果トランジスタ

【課題】電流コラプスが小さく且つ良好な高周波特性を有する電界効果トランジスタを実現できるようにする。

【解決手段】電界効果トランジスタは、基板101の上に形成された窒化物半導体積層体102と、ソース電極105、ドレイン電極106及びゲート電極107と、窒化物半導体積層体102の上に形成された絶縁膜110と、絶縁膜110の上に接して形成され、端部がゲート電極107とドレイン電極106との間に位置するフィールドプレート115とを備えている。絶縁膜110は、第1の膜111と、第1の膜111よりも絶縁耐圧が低い第2の膜112とを含み、ゲート電極117とドレイン電極116との間に形成された薄膜部110aを有している。フィールドプレート115は、薄膜部110aを覆い且つ開口部においてソース電極と接続されている。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法および電子装置

【課題】ゲートリーク電流の増加が抑制された信頼性の高い電界効果トランジスタを提供する。

【解決手段】 ゲート電極は、第1金属層16および第2金属層17を含み、

第2金属層17は、第1金属層16よりも導電率が高く、

第1金属層16の上方に、第2金属層17が積層され、

ソース電極18およびドレイン電極19は、半導体層12〜14上にオーム性接触し、

ゲート電極は、ソース電極18およびドレイン電極19の間に配置され、かつ、第1金属層16により半導体層上にショットキー性接触し、

半導体層上におけるソース電極18およびゲート電極の間、ならびに、ゲート電極およびドレイン電極19の間は、絶縁膜15Aにより覆われ、

かつ、

第2金属層17下面の全体が第1金属層16上面の上方に重なっているか、または、第1金属層16の厚みが絶縁膜15Aの厚み以上であることを特徴とする電界効果トランジスタ。

(もっと読む)

薄膜電極、及びその製造方法

【課題】実効キャリアー濃度が増加し、物質間のエネルギーバンドギャップ調節によりショットキー障壁が減少し、高い透過率を有する、優れた電気的、光学的、熱的及び構造的特性を有する新概念のオーミック接触システムを提供する。

【解決手段】発光ダイオード又はレーザーダイオードにおいてオーミック接触を形成するための薄膜電極において、p型窒化ガリウム層上に積層され、Ni−X固溶体を含有する第1電極層と、前記第1電極層上に積層され、Au、Pt、Pd、Ni、Ru、Rh、Re、C、Cu、及びIrからなる群から選択される少なくとも1種以上の元素を含有する第2電極層と、を含むことを特徴とする、薄膜電極である。

(もっと読む)

基板の配線方法及び半導体製造装置

【課題】基板上に形成された配線用パターンの底部までCu埋め込みが可能な基板の配線方法を提供する。

【解決手段】真空状態に保持された処理容器100内にて配線用パターンが形成された基板を配線する方法であって、ウエハ上の配線用パターンを所望のクリーニングガスにより洗浄する前工程と、前工程後、クラスタ化された金属ガス(金属ガスクラスタCg)を用いて配線用パターン内に金属ナノ粒子を埋め込む埋め込み工程と、を含むことを特徴とする基板の配線方法が提供される。

(もっと読む)

ダイヤモンド半導体素子及びその製造方法

【課題】耐電圧、耐熱性、耐放射線性、及び高速性が優れ、かつ、チャネル領域を短くでき、素子の応答性が高いダイヤモンド半導体素子を高精度で製造できる半導体素子の製造方法を提供する。

【解決手段】第1のダイヤモンド半導体領域1の表面上に、絶縁膜2と多層金属電極層3と犠牲層4とを積層し、犠牲層4上に、局所的にレジスト5をパターン形成する。多層金属電極層3の最上層は、Pt又はPt合金により形成する。そして、レジスト5をマスクとして第1の犠牲層、多層金属電極層及び絶縁膜をエッチングした後、レジスト5を除去して、第1のダイヤモンド半導体領域1上に絶縁膜2と金属電極層3と第1の犠牲層4との積層体をパターン形成する。その後、第1のダイヤモンド半導体領域1上に、不純物の高濃度ドープ層7を形成する。その後、犠牲層4をエッチング除去し、高濃度ドープ層7上に金属電極8を形成する。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】デバイス特性を維持し、ゲートリーク電流を低減できる電界効果トランジスタ及びその製造方法を提供する。

【解決手段】本発明に係る電界効果トランジスタ100は、III−V族窒化物半導体層構造と、半導体層構造上に離間して形成されたソース電極105及びドレイン電極106と、ソース電極105及びドレイン電極106の間に形成されたゲート電極108と、ソース電極105上及びドレイン電極106上に形成された電極保護膜107と、半導体層構造上に、ソース電極105、ドレイン電極106、ゲート電極108及び電極保護膜107の上面の少なくとも一部を覆うように形成され、半導体層構造を保護する第1のパッシベーション膜109を備え、第1のパッシベーション膜109は、所定の材料に対して化学的に活性であり、電極保護膜107は、所定の材料に対して化学的に不活性な金属である。

(もっと読む)

1 - 20 / 112

[ Back to top ]