Fターム[4M104DD46]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 選択成長 (331)

Fターム[4M104DD46]の下位に属するFターム

下地膜(パターニングを含む)上の選択成長 (87)

エネルギービーム誘起によるもの (36)

成長速度の制御 (13)

電極孔内のエピタキシー(凸部形成) (109)

Fターム[4M104DD46]に分類される特許

1 - 20 / 86

配線の製造方法、およびこれを用いた立体的な配線を有する回路形成体の製造方法

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体素子の製造方法

【課題】炭化シリコン基板に接するように、オーミック電極となるシリサイド層を形成するに際して、炭化シリコン基板由来の炭素が、オーミック電極内に拡散して表面に析出するのが抑えられ、オーミック電極の上に電極層を密着性良く形成することができる半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明の半導体素子の製造方法は、炭化シリコン基板2のオーミック電極形成領域2aにシリコン層を形成する第1工程と、シリコン層2上に金属層8を形成する第2工程と、熱処理を行うことによって、シリコン層2に含まれるSiと金属層8の構成元素とを反応させ炭化シリコン基板2と接するシリサイド層41を形成する第3工程と、Siと反応せずに残存した金属層8を除去することによって、シリサイド層41を露出させる第4工程とによってオーミック電極4を形成する。

(もっと読む)

半導体装置及びその製造方法

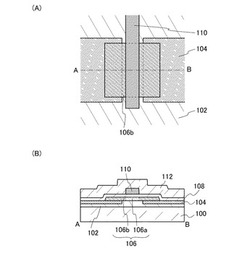

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、ハードマスクに対して、2枚のレジスト膜を用いて、ライン&スペースパターンおよび隣接ゲート電極間切断領域パターンのパターニングを実行し、パターニングされたハードマスクを用いて、ゲート積層膜のエッチングを実行するものである。

(もっと読む)

n型ゲルマニウム上への低抵抗コンタクトの作製方法

【課題】n型Ge上に形成されるコンタクトの接触抵抗を低減する。

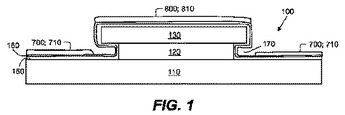

【解決手段】第1ドーパントレベルのn型ドーパントがドープされたゲルマニウム領域(10)を上部に有する半導体基板を得る工程と、n型ドープされたゲルマニウム領域(10)を覆う界面シリコン層(11)を形成する工程であって、界面シリコン層(11)は第2ドーピングレベルのn型ドーパントでドープされて臨界膜厚より大きな膜厚を有し、これにより界面シリコン層(11)は少なくとも部分的に緩和される工程と、界面シリコン層(11)を覆うように、1×10−2Ωcmより小さい電気抵抗率を有する材料の層(12、13)を形成する工程とを含む方法。本発明はまた、対応する半導体デバイスを提供する。

(もっと読む)

パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板

【課題】パターン転写方法及びパターン転写装置、これを適用したフレキシブルディスプレイパネル、フレキシブル太陽電池、電子本、薄膜トランジスター、電磁波遮蔽シート、フレキシブル印刷回路基板を提供する。

【解決手段】本発明によるパターン転写方法は、基板上にパターン物質を形成する第1段階と、パターン物質を固相状態に硬化させる第2段階と、硬化された固相状態のパターン物質にレーザー光を照射して、パターン物質をパターニングする第3段階と、パターニングされた固相状態のパターン物質と柔軟基板をお互いに突き合わせて加圧して、パターン物質から柔軟基板方向に、または柔軟基板からパターン物質方向にレーザー光を照射して、パターン物質と柔軟基板を突き合わせた部位で発生する柔軟基板の粘性力によって、パターン物質を柔軟基板に転写する第4段階と、を含む。

(もっと読む)

配線の形成方法及びその配線を有する表示装置の形成方法

【課題】従来のCMPを伴うダマシン法を用いた配線や電極の形成は、製造工程が煩雑であり高コスト化している。表示装置等の大型基板に配線形成を行うには平坦性等の高精度が要求されて好適せず、また研磨による配線材料の除去・廃棄量が多いという課題がある。

【解決手段】配線の形成方法及び配線を有する表示装置の形成方法は、基板上若しくは回路素子上に設けられた第1の金属拡散防止膜上に、金属シード層をCVD法により形成し、フォトレジストマスクを用いて選択的に無電解メッキ法、又は電解メッキ法により、金属配線層を形成し、金属シード層及び第1の金属拡散防止膜の不要領域除去と、金属シード層及び金属配線層及び第1の金属拡散防止膜の側面を含む表面を覆うように無電解メッキ法による第2の金属拡散防止膜の選択的な形成とにより配線及び電極を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】本発明は、高い信頼性を有するオーミック電極を備えた化合物半導体装置及びその製造方法を提供することを目的とする。

【解決手段】実施形態によれば、窒化物半導体層と、この窒化物半導体層上に設けられたオーミック電極と、を備え、前記オーミック電極は、前記窒化物半導体層との間で金属窒化物を形成する金属を含む第1電極層と、前記第1電極層上に設けられた、アルミニウム(Al)を含む第2電極層と、前記第2電極層の外面を被覆し、かつタングステン(W)を含む第3電極層と、前記第3電極層の外面を被覆し、かつ金(Au)を含む第4電極層と、を有することを特徴とする化合物半導体装置が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置のオン抵抗をより低減させる。

【解決手段】第1導電型の半導体層と、前記半導体層の上側に、前記半導体層の主面に対して平行な方向に沿って周期的に配置された第1導電型の半導体ピラー領域と、前記第1導電型の半導体ピラー領域の表面に選択的に設けられた第2導電型のベース領域と、前記第2導電型のベース領域の表面に選択的に設けられたソース領域と、前記第1導電型の半導体ピラー領域間に設けられ、前記ベース領域の表面にまで達する第2導電型の半導体ピラー領域と、前記ソース領域に電気的に接続された第1の主電極と、前記半導体層の下側に設けられ、前記半導体層に電気的に接続された第2の主電極と、前記第1の主電極と前記第2の主電極との間の通電を制御する制御電極と、を備える。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】初期故障や偶発故障の発生を低減する。

【解決手段】HFET1は、下層のGaN層13およびGaN層13の一部を露出させるトレンチT1が形成された上層のAlGaN層14よりなるIII族窒化物半導体層と、III族窒化物半導体層上に形成されたゲート絶縁膜15と、ゲート絶縁膜15上に形成されたゲート電極16と、を備える。少なくともゲート絶縁膜15と接触するトレンチT1底部のGaN層13上面には、原子層ステップが形成されている。原子層ステップのテラス幅の平均値は、0.2μm以上1μm未満である。

(もっと読む)

成膜方法、プログラム及びコンピュータ記憶媒体

【課題】基板の所定の位置に高い位置精度で膜を形成する。

【解決手段】電極形成用テンプレート112の表面112aには、ウェハWの貫通孔に対応する位置に開口部115が複数形成されている。電極形成用テンプレート112は、開口部115に連通する膜形成用液の流通路116を備えている。この電極形成用テンプレート112とウェハWを密着させた後、この状態のまま、めっき液供給口117から流通路116を介して開口部115からウェハWの貫通孔に対してめっき液を供給することで、ウェハWの貫通孔に電極を形成する。

(もっと読む)

内側にへこんだ形状を含んだトランジスタを製造する方法

トランジスタを製造する方法は、導電材料層と電気絶縁材料層とを順に含んだ基板を準備する工程と、前記電気絶縁材料層上にレジスト材料層を堆積する工程と、前記レジスト材料層をパターニングして、前記電気絶縁材料層の一部を露出させる工程と、露出された前記電気絶縁材料層を除去して、前記導電材料層の一部を露出させる工程と、露出された前記導電材料層を除去し、前記導電材料層及び前記電気絶縁材料層内に凹部形状を作り出す工程と、前記基板と露出された前記電気絶縁材料層及び前記導電材料層とを第2の電気絶縁材料層で共形に被覆する工程と、前記第2の電気絶縁材料層を半導体材料層で共形に被覆する工程と、前記半導体材料層上に導電材料層を指向性堆積する工程とを含む。

(もっと読む)

(もっと読む)

シリサイドの形成方法及び半導体装置

【課題】 ウェット洗浄工程を増加させることなく、かつ、より低温でシリサイドを形成することが可能なシリサイドの形成方法を提供すること。

【解決手段】 表面にシリコンとシリコン酸化物とが露出している基板101上にシリサイドを形成するシリサイドの形成方法であって、基板101の温度を400℃以上として、シリコンとシリコン酸化物とが露出している基板101の表面上にマンガン有機化合物ガスを供給し、基板101の表面に露出したシリコンを選択的にマンガンシリサイド化する。

(もっと読む)

半導体装置の製造方法

【課題】半導体ウェハから半導体装置を製造する場合に、めっき工程においてレジストを用いることなく、裏面電極のめっき層を半導体ウェハの裏面側に選択的に形成する。

【解決手段】裏面にP型の半導体領域を有する半導体素子が形成されている半導体基板と、半導体基板の裏面に接する第1層と、第1層の裏面に接する第2層とを有する裏面電極とを備えている半導体装置を、半導体ウェハから製造する方法。この方法は、半導体ウェハの裏面のP型の半導体領域のダイシング部に、N型の不純物を注入する第1工程と、半導体ウェハの裏面全体に第1層を形成する第2工程と、湿式めっき法によって第1層の裏面に第2層を形成する第3工程とを含んでいる。

(もっと読む)

半導体装置およびその製造方法

【課題】耐熱性に優れたシリサイド層をソース・ドレイン領域に有するp型MOSFETを備える半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、半導体基板2上にゲート絶縁膜11を介して形成されたゲート電極12と、半導体基板2上のゲート電極12の両側に形成されたエレベーテッド層15と、エレベーテッド層15上に形成されたSi:C16層と、半導体基板2、エレベーテッド層15、およびSi:C16内のゲート電極12の両側に形成されたp型のソース・ドレイン領域19と、Si:C層16上に形成されたシリサイド層17と、を有する。

(もっと読む)

成膜方法及び成膜装置

【課題】歩留まりよく高スループットで基板上にパターンを形成することができる成膜方法を提供する。

【解決手段】本発明の成膜方法は、基板の成膜面に、成膜材料の粒子に対して高い親和性を示す高親和性領域と、前記親和性領域よりも低い親和性を示す低親和性領域とを形成する工程と、前記基板との間に電子捕捉部を備えたスパッタ装置を用いて、前記成膜面に前記成膜材料の粒子を飛来させ、前記高親和性領域に選択的に前記成膜材料を堆積させる工程と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

1 - 20 / 86

[ Back to top ]