Fターム[4M104DD52]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 塗布、又は液体からの析出 (2,321) | 電解メッキ (613)

Fターム[4M104DD52]に分類される特許

1 - 20 / 613

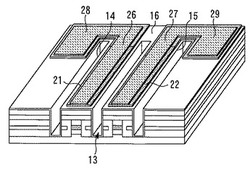

光半導体装置の製造方法

【課題】信頼性を向上させることができる光半導体装置の製造方法を得る。

【解決手段】n−InP基板1上に、分離溝13で互いに分離された光半導体素子14,15を形成する。光半導体素子14,15の上面に、Ptを含む電極21,22をそれぞれ形成する。電極21,22に電気的に接続された電極24を形成する。電極24を給電層とした電解メッキ法により電極21,22上にAuメッキ層26,27をそれぞれ形成する。Auメッキ層26,27を覆うレジスト23をフォトリソグラフィにより形成する。レジスト23をマスクとして電極24をエッチングして電極21と電極22を電気的に分離する。電極24を形成する際に、分離溝13内に電極24が形成されないようにする。

(もっと読む)

半導体装置の製造方法

【課題】高い歩留まりを実現できる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、基板11上の絶縁層13に形成された第1の凹部14および第1の凹部14よりも幅が狭い第2の凹部15に、基板11を銅が流動可能なリフロー温度に加熱した状態で、第1の銅膜21を形成する工程を備えている。また、前記半導体装置の製造方法は、第1の銅膜21上に、不純物濃度が第1の銅膜21よりも高い第2の銅膜22を、第1の銅膜21の形成時よりも流動性が小さい状態で形成する工程を備えている。

(もっと読む)

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Cu配線内における空孔の集中を抑制することでCu配線内でのボイドの形成を抑え、例えば2層間配線系におけるビア接続部等における、いわゆるストレスマイグレーションと呼ばれる断線等の配線不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法において、配線形成後に被処理基板を加熱および除熱する熱サイクル工程を行う、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】電気めっき装置のハードウェアトラブルを低減しながら、銅めっき膜の均一性を保つ。

【解決手段】自動分析器14は、電極16,17間に印加されている電圧を検出し、その電圧値が設定電圧範囲内であるか否かを判断する。検出した電圧値が、設定電圧範囲の下限値よりも低い場合、自動分析器14は、検出した電圧値に基づいて、基本液の不足量を算出し、バルブ11を制御して不足分の基本液を補充した後、めっき液タンク6内のめっき液が規定量を保つようにバルブ13の動作制御を行い、めっき液を廃液する。また、検出した電圧値が設定電圧範囲の上限値よりも高い場合、検出した電圧値に基づいて基本液の超過量を算出し、バルブ12を制御して基本液の濃度が規定範囲内となるように純水をめっき液タンク6に補充してめっき液を薄めた後、バルブ13を制御して規定量を保つようめっき液を廃液する。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

光透過型金属電極、電子装置及び光学素子

【課題】シート抵抗が低く、広い波長範囲で高い透過率を有する光透過型金属電極、電子装置及び光学素子を提供する。

【解決手段】実施形態によれば、複数の第1金属線と、複数の第2金属線と、を含む光透過型金属電極が提供される。複数の第1金属線は、第1方向に沿って並ぶ。第1金属線は、第1方向と交差する第2方向に沿って延びる。複数の第2金属線は、第1方向と第2方向を含む平面に対して平行で第1方向と交差する第3方向に沿って並び、第1金属線と接触する。第2金属線は、その平面に対して平行で第3方向と交差する第4方向に沿って延びる。複数の第1金属線の第1方向における中心どうしの第1距離は、可視光を含む波長帯の最短の波長以下である。複数の第2金属線の第3方向における中心どうしの第2距離は、波長帯の最長の波長を超える。第1金属線と第2金属線の厚さは、最短の波長以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】薄型化された炭化シリコン基板による低抵抗化が可能な半導体装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体装置は、炭化シリコン基板と、半導体層と、絶縁膜と、補強基板と、第1の電極と、第2の電極とを備えている。半導体層は、炭化シリコン基板の第2の面上に設けられ、素子領域と素子領域よりも端部側の周辺領域とを有する。絶縁膜は、半導体層の周辺領域の表面上に設けられている。補強基板は、周辺領域における絶縁膜上に設けられている。第1の電極は、炭化シリコン基板の第1の面に接して設けられている。第2の電極は、素子領域の表面に接して設けられている。

(もっと読む)

窒化物半導体装置

【課題】ドレイン配線電極に起因する電流コラプス現象への影響が抑制され、且つ耐圧が向上された窒化物半導体装置を提供する。

【解決手段】窒化物半導体からなるデバイス層と、デバイス層上に互いに離間して配置されたソース電極及びドレイン電極と、ソース電極とドレイン電極間でデバイス層上に配置されたゲート電極と、デバイス層上に配置された層間絶縁膜と、ドレイン電極とゲート電極間において層間絶縁膜を介してデバイス層と対向して配置され、ドレイン電極と電気的に接続されたドレイン配線電極と、ゲート電極とドレイン電極間においてデバイス層上に層間絶縁膜を介してデバイス層と対向して配置されたドレイン電極に比べて低電位側のフィールドプレートとを備え、ドレイン配線電極下方の層間絶縁膜の膜厚が、フィールドプレート下方の層間絶縁膜の膜厚よりも厚い。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

電極被覆材料、電極構造体、及び、半導体装置

【課題】低いコンタクト抵抗、高い移動度を達成し得る半導体装置を提供する。

【解決手段】ゲート電極13、ゲート絶縁層14、有機半導体材料層から構成されたチャネル形成領域16、及び、金属から成るソース/ドレイン電極15を有する電界効果型トランジスタから成る半導体装置において、チャネル形成領域16を構成する有機半導体材料層と接するソース/ドレイン電極15の部分は、電極被覆材料21で被覆されており、電極被覆材料21は、金属イオンと結合し得る官能基、及び、金属から成るソース/ドレイン電極15と結合する官能基を有する有機分子から成る。

(もっと読む)

めっき装置

【課題】角形基板のめっき処理にカップ方式のめっき法を使っても、均一なめっき厚さを得ることができるめっき装置を提供する。

【解決手段】本発明のめっき装置100は、底面にめっき液噴出口130が形成されためっき槽110と、めっき液噴出口130の上部に位置し、スリット155が形成された陽極部150と、めっき槽110の上部に位置する陰極部120とを含む。

(もっと読む)

半導体電気メッキ装置用のリップシールおよびコンタクト部

【課題】半導体基板の表面との間で封止を形成して、基板の外周領域に電解質が入らないようにするエラストマーリップシール、および封止および電気接続のためのコンタクト部を備える電気メッキ用クラムシェルを提供する。

【解決手段】可撓性のコンタクト部404は、エラストマーリップシール402に一体化されており、エラストマーリップシールの上面にコンフォーマルに配置されており、屈曲して、基板406と適合するコンフォーマルなコンタクト面を形成する。エラストマーリップシールの一部は、クラムシェルにおいて基板を支持、位置合わせおよび封止する。

(もっと読む)

表示装置

【課題】配線等のパターンを、材料の利用効率を向上させ、かつ、作製工程を簡略化して得られた表示装置である。また配線等のパターンを所望の形状で制御性よく形成された導電膜を有する表示装置である。

【解決手段】トランジスタ上の第1の導電膜と、第2の導電膜とは、複数の屈曲点を有するコの字状に設けられる。本形状であっても、第1の導電膜と、第2の導電膜とはパターンを所望の形状で制御性よく形成される。なお、第1の導電膜と第2の導電膜は、共通電極層と、画素電極層となることができる。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】ウエハの外縁上に形成されたネガ型レジストに対して露光現像処理により所定のパターンを形成する場合に、ウエハの外縁上に位置するネガ型レジストに対する露光光の供給をより防止する遮光部の形成工程を備えて歩留まりの向上を実現することが可能な半導体装置の製造方法

【解決手段】ウエハ1の表面上に導電層2及びネガ型レジスト3が順次形成されたウエハ5を準備する工程と、ウエハ5の外縁の少なくとも一部にネガ型レジスト3の表面上と側面とに跨って遮光部材32を塗布する工程と、ネガ型レジスト3に対して露光を行う工程と、遮光部材32を除去する工程と、ネガ型レジスト3を現像する工程と、を有する。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

1 - 20 / 613

[ Back to top ]