Fターム[4M104DD63]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048)

Fターム[4M104DD63]の下位に属するFターム

Fターム[4M104DD63]に分類される特許

141 - 160 / 588

半導体装置およびその作製方法

【課題】電気特性が良好な薄膜トランジスタ及び当該薄膜トランジスタをスイッチング素子として用いた半導体装置を提供することを目的の一とする。

【解決手段】薄膜トランジスタが、絶縁表面上に形成されたゲート電極と、ゲート電極上のゲート絶縁膜と、ゲート絶縁膜上においてゲート電極と重なっており、なおかつ、酸化物半導体が有する一または複数の金属の濃度が、他の領域よりも高い層を含む酸化物半導体膜と、層に接するように酸化物半導体膜上に形成された一対の金属酸化膜と、該金属酸化膜に接するソース電極またはドレイン電極とを有する。そして、金属酸化膜は、ソース電極またはドレイン電極に含まれる金属が酸化することで形成されている。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】酸化物半導体層を用いた、表示装置に代表される半導体装置において、画面サイズの大型化や高精細化に対応し、表示品質が良く、安定して動作する信頼性のよい半導体装置を提供することを課題の一つとする。

【解決手段】引き回し距離の長い配線にCuを含む導電層を用いることで、配線抵抗の増大を抑える。また、Cuを含む導電層を、TFTのチャネル領域が形成される酸化物半導体層と重ならないようにし、窒化珪素を含む絶縁層で包むことで、Cuの拡散を防ぐことができ、信頼性の良い半導体装置を作製することができる。特に、半導体装置の一態様である表示装置を大型化または高精細化しても、表示品質が良く、安定して動作させることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とプラグとの接続信頼性を向上することができる技術を提供する。

【解決手段】本発明では、MISFETのゲート電極G1を金属膜MF2とポリシリコン膜PF1の積層膜から構成するMIPS電極を前提とする。そして、このMIPS電極から構成されるゲート電極G1のゲート長に比べて、ゲートコンタクトホールGCNT1の開口径を大きく形成する第1特徴点と、ゲート電極G1を構成する金属膜MF2の側面に凹部CP1を形成する第2特徴点により、さらなるゲート抵抗(寄生抵抗)の低減と、ゲート電極G1とゲートプラグGPLG1との接続信頼性を向上することができる。

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

曲線状のゲート酸化物プロファイルを有するスプリットゲート半導体素子

スプリットゲート半導体素子は、第1の電極領域及び第2の電極領域を有するトレンチゲートを含む。前記第1の電極領域及び前記第2の電極領域は、ゲート酸化物層及び隣接誘電層によって相互に分離される。前記ゲート酸化物層と前記誘電層との間の境界は曲線状となっており、これにより、前記ゲート酸化物層が前記トレンチの側壁と出合う場所である鋭角部が回避される。 (もっと読む)

半導体装置の製造方法

【課題】微細なパターンを精度良く形成することのできる半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置の製造方法は、被加工体1上にCを含む材料からなる芯材2を選択的に形成する工程と、芯材2の上面および側面を覆うように、酸素を含まない材料からなる保護膜3を形成する工程と、保護膜3を介して芯材2と被加工体1を覆うように酸化膜4を形成する工程と、芯材2の側方に少なくとも酸化膜4からなる側壁5を加工形成する工程と、少なくとも芯材2を除去した後、側壁5をマスクとして用いて被加工体1をエッチングし、側壁5のパターンを転写する工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、高周波高出力で使用可能な、化合物半導体高電子移動度トランジスタを提供する。

【解決手段】支持基板20の第1の主表面20a上に、チャネル層40及びバリア層50が積層されて構成される、化合物半導体高電子移動度トランジスタであって、ソース電極62が形成された領域を含む、支持基板の領域部分が金属部22であり、ドレイン電極64が形成された領域を含む、支持基板の他の領域部分がシリコン部24で構成される。

(もっと読む)

半導体装置の製造方法

【課題】溝側面に側壁膜を形成する際に、側壁膜表面にエッチングダメージを受けることなく、側壁膜上面の溝開口部からの深さのばらつきを抑制して形成可能な方法を提供する。

【解決手段】半導体基板主表面に形成された溝の側壁に第1の層を形成する工程、溝を保護膜で埋設する工程、保護膜の表面の高さが溝の開口部よりも低い位置になるようにドライエッチング法でエッチバックし、該エッチバックにより露出した第1の層をエッチング除去する工程、とを含む半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】 ゲートとドレインの間で生じる電界集中を緩和する半導体装置を提供する。

【解決手段】本発明によれば,半導体基板上にゲート絶縁膜を介して形成された第1のゲート電極と、前記半導体基板上に前記ゲート絶縁膜を介して形成され、かつ、第1のゲート電極の側面に絶縁性のスペーサを介して配置された第2のゲート電極と、第1及び第2のゲート電極を挟むように前記半導体基板上に形成されたソース領域及びドレイン領域と、第1のゲート電極下方における前記半導体基板の一部の領域を挟むように形成され、第2のゲート電極及び前記ソース領域及びドレイン領域と重なるように形成された電界緩和領域と、を備える半導体装置が提供される。

(もっと読む)

半導体装置及びその製造方法

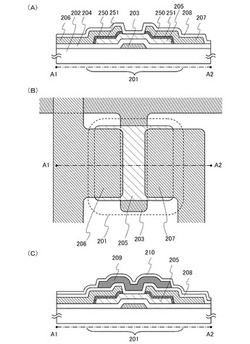

【課題】高集積なSGTを用いたCMOSインバータ回路からなる半導体装置を提供する。

【解決手段】第1のトランジスタは、島状半導体層と、島状半導体層の周囲を取り囲む第1のゲート絶縁膜と、第1のゲート絶縁膜の周囲を取り囲むゲート電極と、島状半導体層の上部に配置された第1の第1導電型高濃度半導体層と、島状半導体層の下部に配置された第2の第1導電型高濃度半導体層とを有し、第2のトランジスタは、ゲート電極の周囲の一部を取り囲む第2のゲート絶縁膜と、第2のゲート絶縁膜の周囲の一部に接する第2の半導体層と、第2の半導体層の上部に配置され、第1導電型高濃度半導体層と反対の極性を有する第1の第2導電型高濃度半導体層と、第2の半導体層の下部に配置され、第1導電型高濃度半導体層と反対の極性を有する第2の第2導電型高濃度半導体層とを有することにより、上記課題を解決する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一とする。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成された表示部用配線とを有すればよい。

(もっと読む)

半導体装置

【課題】消費電力を抑えつつ、走査線へ十分な振幅の信号を供給することができる半導体装置の提供を課題の一とする。また、消費電力を抑えつつ、走査線に供給する信号のなまりを抑制し、立ち上がり時間又は立ち下がり時間を短くすることができる半導体装置の提供を課題の一とする。

【解決手段】表示素子及び少なくとも1つの第1トランジスタをそれぞれ有する複数の画素と、複数の画素を選択するための信号を走査線に供給する走査線駆動回路とを有し、表示素子の画素電極層と、第1トランジスタのゲート電極層、ソース電極層及びドレイン電極層と、走査線とは、透光性を有する導電膜を用いており、走査線駆動回路は、第2トランジスタと、第2トランジスタのゲート電極層とソース電極層の間の電圧を保持する容量素子と、を有しており、第2トランジスタのソース電極層は走査線に接続されている半導体装置。

(もっと読む)

ショットキーダイオードの製造方法

【課題】所望の逆耐圧を容易に設定できるショットキーダイオードの製造方法を提供することを課題とする。

【解決手段】

本発明はショットキーダイオードの製造方法において、半導体基板を準備する工程と;前記半導体基板上に第1導電型埋め込み酸化膜及び第1導電型エピタキシャル層を形成する工程と;前記第1導電型エピタキシャル層内に、前記第1導電型埋め込み酸化膜に接続された第1導電型拡散層を形成する工程と;前記第1導電型エピタキシャル層上に絶縁膜を形成する工程と;前記絶縁膜をマスクとしたイオン注入により、ショットキーダイオード端部の電界集中を緩和する第2導電型拡散層を形成する工程と;前記第2導電型拡散層の上部に、シリサイド層(金属層)を形成する工程と;前記絶縁層内に、前記第1導電型拡散層に接続されるコンタクトを形成する工程と;前記絶縁層上に前記コンタクトと接続される配線層を形成する工程とを含むことを特徴とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

半導体装置

【課題】 DCBLストレスによるオフ耐圧性能を向上させた高耐圧LDMOSを提供する。

【解決手段】 半導体基板に形成され、トレンチにより素子分離され、ソース領域がドレイン領域で挟まれたMOSトランジスタであり、ゲート電極に接続されたメタル層ゲート配線がP型ドリフト層上を通過するように前記トレンチ外に引き出されている高耐圧LDMOS。

(もっと読む)

半導体装置及びその作製方法

【課題】トランジスタを構成する各部材の抵抗を小さくし、トランジスタのオン電流の向上を図り、集積回路の高性能化を図ることを課題の一とする。

【解決手段】単結晶半導体基板上に絶縁層を介して設けられ、素子分離絶縁層によって素子分離されたn型FET及びp型FETを有する半導体装置であって、それぞれのFETは、半導体材料を含むチャネル形成領域と、チャネル形成領域に接し、半導体材料を含む導電性領域と、導電性領域に接する金属領域と、チャネル形成領域に接するゲート絶縁層と、ゲート絶縁層に接するゲート電極と、金属領域を一部に含むソース電極またはドレイン電極と、を有する。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

141 - 160 / 588

[ Back to top ]