Fターム[4M104DD63]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048)

Fターム[4M104DD63]の下位に属するFターム

Fターム[4M104DD63]に分類される特許

161 - 180 / 588

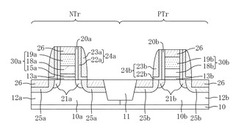

半導体装置

【課題】高誘電体材料を含むゲート絶縁膜とメタルゲート電極とを有する半導体装置の製造中にポリシリコンからなる残渣が素子分離領域上に生じる虞があり、不良の原因であった。

【解決手段】半導体基板10の第1の活性領域10a上には、高誘電体材料と第1の金属とを含有する第1のゲート絶縁膜13aと、下層導電膜15aと第1の導電膜18aと第1のシリコン膜19aとを有する第1のゲート電極30aとを備えた第1導電型の第1のトランジスタが形成されている。半導体基板10の第2の活性領域10b上には、高誘電体材料と第2の金属とを含有する第2のゲート絶縁膜13bと、第1の導電膜18aと同一の材料からなる第2の導電膜18bと第2のシリコン膜19bとを有する第2のゲート電極30bとを備えた第2導電型の第2のトランジスタが形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】微細トランジスタのシリサイド形成工程において、ゲート間容量の増大がなく且つL字状スペーサの端部がエッチングされず接合リーク等の不良を防止できるようにする。

【解決手段】 半導体基板101上にゲート絶縁膜103を介して形成されたゲート電極104及びその側面上に形成された第1のサイドウォール108及びソースドレイン拡散層111を有する第1のトランジスタと、半導体基板上にゲート絶縁膜103を介して形成されたゲート電極104、その側面上に形成された第1のサイドウォール108、及びその外側に形成された第2のサイドウォール109を有する第2のトランジスタとを備えている。シリサイド形成領域Aにおけるゲート電極の上部及びソースドレイン拡散層の上部にはニッケルシリサイド層114が形成されており、第1のサイドウォール108は、第2のサイドウォール109をエッチングする際のエッチング材に対して耐性を有している。

(もっと読む)

半導体装置の製造方法

【課題】後続の工程に伴う埋め込みゲートの酸化を防止し、ビットラインコンタクト及びストレージノードコンタクトと基板との間のコンタクト面積を増加させ、コンタクト抵抗を低減し、ビットラインコンタクト及びストレージノードコンタクトと埋め込みゲートとの間のGIDLを低減し、自己整合コンタクト不良を防止することのできる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板の全面にプラグ導電膜を形成するステップと、前記プラグ導電膜をエッチングしてランディングプラグを形成するステップと、前記ランディングプラグ間の基板をエッチングしてトレンチを形成するステップと、前記トレンチの表面上にゲート絶縁膜を形成するステップと、前記ゲート絶縁膜上に前記トレンチの一部を埋め込む埋め込みゲートを形成するステップと、を含むことを特徴とする。

(もっと読む)

薄膜トランジスタの製造方法及び薄膜トランジスタ

【課題】ポリマー絶縁層及び無機層から構成されるゲート絶縁層を有し、溶液により塗布可能な半導体前駆体材料を用いこれに半導体変換処理を行って金属酸化物半導体を有することにより、移動度が高く、閾電圧が低く、且つ、On/Off特性が良好な薄膜トランジスタの製造方法及び薄膜トランジスタを提供する。

【解決手段】支持体6上にゲート電極5、ゲート絶縁層2、ソース電極3及びドレイン電極4、金属酸化物半導体層1を有する薄膜トランジスタの製造方法において、ゲート絶縁層が、ポリマー絶縁層2a該ポリマー絶縁層上の無機層2bからなり、無機層2bの上に金属酸化物半導体前駆体材料の溶液を用いて金属酸化物半導体前駆体層を形成する工程を有することを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

半導体装置の洗浄方法

【課題】ゲートメタル材料の溶解抑制と良好なコンタクト抵抗取得とを両立可能な半導体装置の洗浄方法を提供する。

【解決手段】半導体装置の洗浄方法は、以下の工程を備えている。シリコンを含み、かつ主表面MSを有する半導体基板SBが準備される。主表面MSの上にメタル層GMとシリコン層GPとを下から順に積層した積層ゲートGE2が形成される。主表面MSとシリコン層GP表面との各々にシリサイド層SCLが形成される。主表面MSと積層ゲートGE2表面との各々のシリサイド層SCLの上に絶縁層ILが形成される。半導体基板SBの主表面MSと積層ゲートGE2の表面との各々のシリサイド層SCLが絶縁層ILから露出するようにシェアードコンタクトホールSC2が絶縁層ILに形成される。シェアードコンタクトホールSC2に硫酸洗浄、過酸化水素水洗浄およびAPM洗浄をそれぞれ別工程で行うことによりシェアードコンタクトホールSC2に形成された変質層ALが除去される。

(もっと読む)

半導体装置

【課題】パワーMISFETのゲート抵抗を低減し、装置の特性の向上を図る。

【解決手段】チップ領域CAのY方向にストライプ状に形成された複数の溝の内部の多結晶シリコン膜よりなるゲート部と電気的に接続されるゲート電極GEを、前記ストライプ状の溝の間に形成されるソース領域と電気的に接続されるソース電極SEと同層の膜で形成し、さらに、ゲート電極GEを、チップ領域CAの周辺に沿って形成されたゲート電極部G1と、チップ領域CAをX方向に2分割するよう配置されたゲートフィンガー部G2とで構成し、ソース電極SEを、ゲートフィンガー部G2の上部に位置する部分と、下部に位置する部分とで構成し、ゲート電極GEおよびソース電極SEをバンプ電極を介してリードフレームと接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】相異なる動作電圧の第1,第2,第3のMISトランジスタを有する半導体装置において、第1,第2,第3のチャネル拡散層の不純物プロファイルの変動を抑制する。

【解決手段】半導体装置は、第1,第2,第3の活性領域上に第1,第2,第3のゲート絶縁膜13A,13B,14Cを介して形成された第1,第2,第3のゲート電極を有する第1導電型の第1,第2,第3のMISトランジスタを備えている。第1のゲート絶縁膜13Aは、第1のシリコン酸化膜13aと第1の高誘電率絶縁膜15aとからなる。第2のゲート絶縁膜13Bは、第2のシリコン酸化膜13bと第2の高誘電率絶縁膜15bとからなる。第3のゲート絶縁膜14Cは、第3のシリコン酸化膜14cと第3の高誘電率絶縁膜15cとからなる。第2のシリコン酸化膜13bは、第1のシリコン酸化膜13aと同じ膜厚を有し、且つ、第3のシリコン酸化膜14cよりも厚い膜厚を有している。

(もっと読む)

半導体装置

【課題】10GHz程度以上のクロック周波数での動作が可能な高速半導体装置の提供。

【解決手段】n−MOSFET100n、p−MOSFET100pを有し、n−MOSFETのチャンネルを形成する第1の領域の表面が(100)面から±10°以内の面または(110)面から±10°以内の面のを有し、p−MOSFETのチャンネルを形成する第2の領域の表面が((110)面から±10°以内の面または(100)面から±10°以内の面のを有し、第1及び第2の領域の各々から各々の両端の前記ソース電極、ドレイン電極の各々までの抵抗を4Ω・μm以下とし、かつ第1の領域と第1のゲート絶縁層との界面及び第2の領域と第2のゲート絶縁層との界面を、各領域のソースからドレインに向かう方向での長さ2nmにおけるピーク・トゥ・バレイが0.3nm以下であるような平坦度とした半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】フォトリソグラフィーのプロセスマージンを確保すると共に、ゲート電極とコンタクトプラグとの短絡が生じにくい半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、層間絶縁膜114の上に第1の下部開口部115aを有する第1のマスク層115を形成する工程と、第1のマスク層115の上に第1の下部開口部115aを通して層間絶縁膜114を露出する第1の上部開口部116aを有する第2のマスク層116を形成する工程とを備えている。第1の下部開口部115aは、隣接するゲート電極102同士の間に形成され、ゲート電極102と平行な方向に延びる長辺と、ゲート電極102と交差する方向に延びる短辺とを有する平面方形状である。第1の上部開口部116aは、各辺の長さが第1の下部開口部115aの短辺よりも長い平面方形状である。

(もっと読む)

薄膜トランジスタを備えた表示素子及びその製造方法

【課題】工程を単純化することのできる酸化物薄膜トランジスタを備えた表示素子及びその製造方法を提供する。

【解決手段】表示素子は、第1基板120及び第2基板140と、第1基板の画素領域に形成され、ゲート電極121、ゲート絶縁層126、酸化物半導体層122、並びにソース電極123及びドレイン電極124からなる薄膜トランジスタと、第1基板のゲートパッド領域に形成されたゲートパッド118、及び第1基板のデータパッド領域に形成されたデータパッド119と、ゲートパッド領域のゲート絶縁層上に形成され、コンタクトホールを介してゲート電極に接続する金属層155と、第1基板の全体にわたって形成された保護層128と、画素領域の保護層に形成された画素電極と、ゲートパッド領域に形成された第1透明導電層129a及びデータパッド領域に形成された第2透明導電層129bと、基板間に形成された液晶層130とから構成される。

(もっと読む)

薄膜トランジスタ、液晶表示装置及びこれらの製造方法

【課題】In、Ga及びZnを含むアモルファス酸化物からなる半導体層にダメージを与えず、また、オフ電流の小さい薄膜トランジスタを提供する。

【解決手段】In、Ga及びZnを含むアモルファス酸化物からなる半導体層を備え、ゲート電極から見てソース領域又はドレイン領域の手前側にソース電極又はドレイン電極が形成されてなるボトムゲート型薄膜トランジスタを構成する。このような構造を持つ薄膜トランジスタではドレイン電極等の金属層のエッチングによって半導体層がダメージを受けることはない。また、裏面照射によって紫外線の照射された半導体層部分を高導電率化するものであるため、半導体層へのダメージが生じないため信頼性が向上する。また、ソース電極又はドレイン電極によって紫外線が遮光された半導体層の領域は照射前の導電率と同じとなるため、オフ電流の値を小さくすることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】導電層を自己整合的に形成する場合において、第1の拡散層コンタクトプラグのコンタクトマージンを比較的大きく取る。

【解決手段】半導体装置10は、第1のシリコンピラー14Aと、第1のシリコンピラー14Aの上面に設けられ、導電性材料が充填されたスルーホール30aを有する層間絶縁膜30と、スルーホール30aの上側開口部に設けられた第1の拡散層コンタクトプラグDC1とを備え、スルーホール30aの下側開口部の面積は前記第1のシリコンピラー14Aの上面の面積に等しくなっているとともに、スルーホール30aの上側開口部の面積はスルーホール30aの下側開口部の面積より大きくなっており、それによって、スルーホール30a内の導電性材料の第1の拡散層コンタクトプラグDC1との接続面の面積が第1のシリコンピラー14Aの上面の面積より大きくなっている。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写加工技術を用いる場合に、転写用のマスクが非対称な形状となることに起因した不具合を極力防止する

【解決手段】半導体基板1上に、ゲート電極を形成するための膜を積層形成する。第1膜としてシリコン窒化膜8a、第2膜としてシリコン酸化膜9aを積層形成する。シリコン酸化膜9aを加工して芯材パターン9を形成する。ウェット処理によりシリコン窒化膜8aを選択的エッチングして、所定深さまで除去すると共に、芯材パターン9の直下に括れ部8bを形成する。非晶質シリコン膜11aを形成し、エッチバックによりスペーサパターン11を形成する。芯材パターン9をエッチングにより除去すると独立したスペーサパターン11を得ることができ、これをマスクとしてシリコン窒化膜8aをRIEエッチング加工しマスクパターン8を形成する。イオンが斜入しても芯材パターン9の直下部分が偏ったエッチング状態とならない。

(もっと読む)

薄膜トランジスタ基板の製造方法、薄膜トランジスタ基板、及び表示装置

【課題】コンタクトエッチングの加工精度を上げて、精度良くコンタクトホールが形成されたTFT基板及び、そのTFT基板を工程が煩雑にならずに製造コストが抑制可能なTFT基板の製造方法を提供する。

【解決手段】厚膜レジスト部21と厚膜レジスト部よりも厚みの薄い薄膜レジスト部22と、開口部23とからなる膜厚差を有するパターンのレジスト層20を設け、レジスト層20の開口部の絶縁膜のエッチングと、レジスト層20の薄膜レジスト部22の除去と、薄膜レジスト部22の下層の絶縁膜のエッチングとを同じエッチング工程で行うことにより、ゲートコンタクトホール8及びシリコンコンタクトホール9を共に形成してTFT基板1を製造した。

(もっと読む)

非対称型半導体デバイス及び製造方法

【課題】 非対称型半導体デバイス、及びその製造の際にスペーサ・スキームを用いる方法を提供する

【解決手段】 高kゲート誘電体の表面上に配置された非対称型ゲート・スタックを含む半構造体が提供される。非対称型ゲート・スタックは、第1の部分と第2の部分とを含み、第1の部分は、第2の部分とは異なる閾値電圧を有する。本発明の非対称型ゲート・スタックの第1の部分は、下から上に、閾値電圧調整材料及び少なくとも第1の導電性スペーサを含み、本発明の非対称型ゲート・スタックの第2の部分は、ゲート誘電体の上の少なくとも第2の導電性スペーサを含む。幾つかの実施形態において、第2の導電性スペーサは、下にある高kゲート誘電体と直接接触しており、他の実施形態においては、第1及び第2の導電性スペーサは、前記閾値電圧調整材料と直接接触している。

(もっと読む)

現像液耐性に優れた表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ現像液耐性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で透明導電膜と直接接続されるAl合金膜であって、上記Al合金膜は、グループAに属するNiおよび/またはCoの元素を2.0原子%以下(0原子%を含まない)、並びにグループBに属する少なくとも一種の元素を0.05〜2.5原子%含み、上記グループBの元素はGd、Nd、La、Y、Sc、Pr、Dy、Ce、Ho、Er、Tb、Pm、Tm、Yb、Lu、Hf、Zr、Zn、Mg、Ti、Mn、およびGeから構成されている。

(もっと読む)

有機半導体に電気接点を形成する方法

【課題】雰囲気条件下で簡単に実施でき、安価な金属箔を使用できる、有機半導体表面に電気接点を形成する方法を提供する。

【解決手段】半導体表面に溶媒層を形成し、前記表面、少なくともその下面が部分的に酸化された金属箔を載置し、次いで前記溶媒を蒸発させる。本発明方法によると、経済的な競争力が向上し、同時に半導体の構造の保持、及び高い界面導電性がその品質的な価値を上昇させる。

(もっと読む)

表示装置および表示装置の製造方法

【課題】有機半導体層を用いた薄膜トランジスタと画素電極とを含む層間に発生する応力を緩和することが可能で、これによりトランジスタ特性の劣化を防止して、表示特性および信頼性の向上が図られた表示装置を提供する。

【解決手段】有機半導体層を用いた薄膜トランジスタが配列形成された基板と、薄膜トランジスタを覆う状態で基板上に設けられた層間絶縁膜と、層間絶縁膜上に設けられた画素電極とを備えたものである。特に、層間絶縁膜は、薄膜トランジスタよりも平面視的なサイズが小さい凹凸パターンからなる凹凸表面を有しており、この凹凸表面上に画素電極が設けられていることを特徴としている。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

電子デバイスの製造方法

【課題】可撓性を有する電子デバイスを、素子の劣化を防いで簡易に且つ短時間で製造することができる電子デバイスの製造方法を提供する。

【解決手段】支持基板12上に、特定の刺激によって発泡する発泡材を含む剥離層14を形成する工程と、前記剥離層上に電子デバイスを構成する素子を含む構造体11を形成する工程と、前記剥離層に前記特定の刺激を加えることにより該剥離層に含まれる前記発泡材を発泡させ、該剥離層を介して前記構造体を前記支持基板から剥離させる工程と、を有する電子デバイス10の製造方法。好ましくは、発泡材として熱膨張性マイクロカプセル15を用いる。

(もっと読む)

161 - 180 / 588

[ Back to top ]