Fターム[4M104DD64]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ウェットエッチ (644)

Fターム[4M104DD64]に分類される特許

101 - 120 / 644

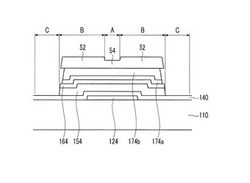

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

感光性塗布型電極材料を用いたTFTの製造方法

【課題】従来の電極方法であるフォトリソグラフィ、マスクスパッタリングは、工程の簡略化、材料使用効率、コスト、多様な基板サイズに対応において解決するには困難な課題があり、インクジェット方式では高精細度なパターンが得られないという課題がある。

【解決手段】感光性塗布型電極材料を用いて、所望の電極パターンニングを行う。本発明による電極作成工程において、コストメリットがある拡散光を光源とするランプを用いて第1の露光と第1の露光よりも大きい露光量をもった第2の露光を施すことで、所望の電極パターンを得ることができる。拡散光を用いた2回露光プロセスによって、例えばTFT作成において従来の方法では解決できない材料使用効率、コスト、多様な基板サイズに対応という課題かつ、インクジェット方式では解決できない高精細パターニングを解決するものである。

(もっと読む)

薄膜トランジスタ及びこれを用いた表示装置、並びに、薄膜トランジスタの製造方法

【課題】オフ電流を抑制するとともにオン電流を確保することができる薄膜トランジスタを提供する。

【解決手段】基板10と、基板の上方に形成されたゲート電極11及びゲート絶縁膜12と、ゲート絶縁膜を介して配置されたチャネル層13と、チャネル層に接続されたバッファ層14と、バッファ層に接続され、不純物が添加された第1コンタクト層15a(15b)と、第1コンタクト層に接続され、第1コンタクト層よりも不純物濃度が高い第2コンタクト層16a(16b)と、第2コンタクト層に接続されたソース電極17S及びドレイン電極17Dとを備える。ソース電極とドレイン電極との間におけるキャリアの移動経路は、チャネル層、バッファ層、第1コンタクト層及び第2コンタクト層を経由してキャリアが移動する第1経路と、チャネル層及び第2コンタクト層を経由してキャリアが移動する第2経路とを含む。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】柱状結晶構造を有する金属を用いた場合でも、簡便な方法で、再現性良く階段構造状のテーパーを有する電極を形成する。

【解決手段】真空状態を保ったままの状態において、同一種類の金属を用いて、スパッタリング法で少なくとも2層の金属膜を成膜する成膜工程と、該成膜工程によって成膜された複数の金属膜にエッチング処理を施すことにより、階段構造状のテーパー形状を端部に有する、ゲート電極、ソース電極およびドレイン電極のうちの少なくとも1つを形成するエッチング工程とによって薄膜トランジスタを製造する。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス負荷を軽減するとともに、EOTを十分に低減するための絶縁膜の薄膜化と、バンドエッジ近傍の仕事関数を有するゲート構造とを実現した半導体装置を提供する。

【解決手段】基板101の異なる領域に形成されたp型トランジスタ100a及びn型トランジスタ100bを備える半導体装置100であって、p型トランジスタ100aは、基板101上方に形成された、第1高誘電率材料からなる第1高誘電率膜106aと、第1高誘電率膜106a上方に形成された、全体が金属によりシリサイド化された第1フルシリサイド電極107aとを備え、n型トランジスタ100bは、基板101上方に形成された、第2高誘電率材料が添加された第1高誘電率材料からなる第2高誘電率膜106bと、第2高誘電率膜106b上方に形成された、全体が金属によりシリサイド化された第2フルシリサイド電極107bとを備える。

(もっと読む)

ウェットエッチング性に優れた表示装置用配線膜

【課題】ウェットエッチング性が良好な表示装置用配線膜を提供する。

【解決手段】希土類金属元素、Zn、Mg、およびCaよりなる群から選択される少なくとも一種の元素を5原子%以上50原子%以下の範囲で含むMo合金と、純CuまたはCu合金との積層構造を有する表示装置用配線膜である。

(もっと読む)

半導体装置、光学装置及びセンサ装置

【課題】ソース電極及びドレイン電極と有機半導体材料層との間の接触抵抗を低下させることができ、これを簡便な製造プロセスで実現できる半導体装置、光学装置及びセンサ装置を提供すること。

【解決手段】ソース電極5と、ドレイン電極6と、少なくともこれらの電極間に設けられた有機半導体材料層7とを有し、有機半導体材料層7を介してソース電極5とドレイン電極6との間で電荷を移動させるように構成された有機電界効果トランジスタにおいて、ソース電極5及びドレイン電極6が、導電性高分子材料と電荷移動錯体との混合物からなる、有機電界効果トランジスタ1a。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1の主面にゲート絶縁膜用のHf含有膜4、Al含有膜5及びマスク層6を形成してから、nチャネル型MISFET形成予定領域であるnMIS形成領域1Aのマスク層6とAl含有膜5を選択的に除去する。それから、nMIS形成領域1AのHf含有膜4上とpチャネル型MISFET形成予定領域であるpMIS形成領域1Bのマスク層6上に希土類含有膜7を形成し、熱処理を行って、nMIS形成領域1AのHf含有膜4を希土類含有膜7と反応させ、pMIS形成領域1BのHf含有膜4をAl含有膜5と反応させる。その後、未反応の希土類含有膜7とマスク層6を除去してから、メタルゲート電極を形成する。マスク層6は、窒化チタン又は窒化タンタルからなる窒化金属膜6aと、その上のチタン又はタンタルからなる金属膜6bとの積層構造を有する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】オーミックコンタクト層の膜厚やドライエッチング時のエッチングレートに依存せず所望のエッチングが可能となる薄膜トランジスタの製造方法を提供する。

【解決手段】絶縁性基板上に、ゲート電極と、ゲート電極を覆うように形成されたゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、を備える薄膜トランジスタの製造方法であって、絶縁性基板上に、ゲート電極と、ゲート絶縁膜と、半導体層と、オーミックコンタクト層と、ソース・ドレイン電極と、がこの順に積層される積層ステップと、積層ステップによって積層されたソース・ドレイン電極とオーミックコンタクト層とがエッチングガスでエッチングされるエッチングステップと、オーミックコンタクト層がエッチングされてゲート絶縁膜が露出し始める点をエッチング終了ポイントとして検知するエッチング終了検知ステップと、を備える薄膜トランジスタの製造方法。

(もっと読む)

半導体装置の製造方法

【課題】極めて薄い金属膜からなるエミッタおよびゲートフィンガー電極を有する圧接型IGBTにおけるエッチングにおいて、エッチング厚さの厳密な制御を必要とすることなく、所望の厚さを有するエミッタおよびゲートフィンガー電極を形成することができる半導体装置の製造方法を提供する。

【解決手段】圧接型半導体に用いる半導体装置の製造方法であって、Si基板上に第1Al層を形成する工程と、所望のエミッタ電極およびゲートフィンガー電極形状となるよう第1Al層の一部をエッチングする工程と、第1Al層上にAl以外の金属からなる下地層を形成する工程と、下地層上に第2Al層を形成する工程と、第2Al層のうちエミッタ電極に相当する部分にレジストを塗布する工程と、レジストを塗布した部分以外の第2Al層をエッチングする工程と、レジストを塗布した部分以外の下地層をエッチングする工程と、レジストを除去する工程とを有する。

(もっと読む)

金属配線

【課題】従来の、真空装置を用いた形成方法に比べて簡便かつ安価に形成され、しかもインクジェット印刷方法によって形成されるもの比べて、断線等を生じることなしに、より細線化された金属配線を提供する。

【解決手段】Ag粒子、またはAgを50原子%以上含む合金粒子を含む分散液を塗布して塗膜を形成し、乾燥後にパターン形成したのち焼成して形成され、その縁部2における、基材の表面方向の、想定される外形線4からの凹入量の最大値と突出量の最大値との和が50nm以下、前記縁部2における、基材3の表面方向の、想定される外形線4と直交し、かつ金属配線1の厚み方向の断面のうち、前記厚み方向の外形線の、前記基材3の表面と接する部分の、前記基材3の表面との交差角度が70°以下で、かつ抵抗率が14μΩ・cm以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、特性の安定したトランジスタを得ることが可能で、かつ複数の縦型トランジスタ間の特性のばらつきを抑制可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板11の表面11aが部分的にエッチングされて形成され、縦壁面となる第1及び第2の側面26a,26bを含む内面によって区画された第2の溝26と、第2の溝26の第1及び第2の側面26a,26bを覆うゲート絶縁膜32と、ゲート絶縁膜32上に形成され、上端面37a,38aが半導体基板11の表面11aより低い位置にある第1の導電膜34、及び第1の導電膜34に形成され、上端面35aが第1の導電膜34の上端面34aより低い位置にある第2の導電膜35よりなるゲート電極33と、第2の溝26内に、半導体基板11の表面11aより低い位置に配置され、第2の導電膜35の上端面35aを覆う第1の絶縁膜17と、を有する。

(もっと読む)

薄膜トランジスタとその製造方法、及びアクティブマトリックス基板

【課題】電極/配線の材料としてAl及び/又はその合金が用いられており、オフリーク電流が小さく良好な素子特性を有する薄膜トランジスタ(TFT)を提供する。

【解決手段】TFT101は、基板1上にゲート電極2とゲート絶縁膜3とチャネル層として機能する半導体膜4とを備え、半導体膜4上にソース電極6とドレイン電極7とが互いに離間して設けられたものであり、ソース電極6及びドレイン電極7は、アルミニウム及び/又はその合金を主成分とする少なくとも1層のアルミニウム(合金)膜を含む単層膜又は積層膜からなり、半導体膜4の表面のソース電極6及びドレイン電極7の間の領域8に、電気的に不活性な少なくとも1種のアルミニウム化合物9が形成されたものである。

(もっと読む)

半導体装置の作製方法

【課題】不良を抑制しつつ微細化を達成した半導体装置の提供を目的の一とする。

【解決手段】平坦な表面上に絶縁膜を形成し、絶縁膜上にマスクを形成し、マスクにスリミング処理を行い、マスクを用いて絶縁膜にエッチング処理を行い、絶縁膜を覆うように導電膜を形成し、導電膜および絶縁膜に研磨処理を行うことにより、導電膜および絶縁膜の厚さを等しくし、導電膜をエッチングして、導電膜より厚さの小さいソース電極およびドレイン電極を形成し、絶縁膜、ソース電極、およびドレイン電極と接する酸化物半導体膜を形成し、酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上の絶縁膜と重畳する領域にゲート電極を形成する。

(もっと読む)

半導体装置の作製方法、及び半導体装置

【課題】酸化物半導体層を用い、電気特性の優れた薄膜トランジスタを備えた半導体装置

を提供することを課題の一とする。また、同一基板上に複数種類の薄膜トランジスタの構

造を作製して複数種類の回路を構成し、増加する工程数が少ない半導体装置の作製方法を

提供することを課題の一とする。

【解決手段】絶縁表面上に金属薄膜を成膜した後、酸化物半導体層を積層し、その後、加

熱処理などの酸化処理を行うことで金属薄膜の一部または全部を酸化させる。また、論理

回路などの高速動作を優先する回路と、マトリクス回路とで異なる構造の薄膜トランジス

タを配置する。

(もっと読む)

薄膜電界効果型トランジスタの製造方法

【課題】TFT特性が良好であり、しかも面内均一性等も良好な薄膜電界効果型トランジスタを低コストで提供すること。

【解決手段】基板上に、少なくともゲート電極、絶縁膜、活性層、ソース電極およびドレイン電極が形成され、活性層上にソース電極およびドレイン電極が設けられた薄膜電界効果型トランジスタの製造方法である。本発明の製造方法は、エッチング液として、りん酸、酢酸および硝酸を含む混酸水溶液を用いて、ソース電極およびドレイン電極を形成する工程を有する。この活性層は、In、GaおよびZnを含むアモルファス酸化物半導体で構成されるものであり、かつZn濃度が20%未満であり、In濃度が40%以上であり、Ga濃度が37%以上である。

(もっと読む)

貫通孔配線基板の製造方法

【課題】めっき反応速度を調整することでめっき未着を防ぐことが可能な貫通孔配線基板の製造方法を提供することである。

【解決手段】微小デバイスを構成する貫通孔配線基板の製造方法であって、基板40の両表面を貫通する貫通孔41を形成する工程と、貫通孔41の少なくとも内表面にNiめっきを成長させる工程と、を備え、貫通孔41の少なくとも内表面にNiめっきを成長させる工程では、Niめっきの析出レートを50nm/min未満にしてめっきを成長させる。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗が可及的に低い半導体装置、および前記半導体装置を高歩留まりで容易に得ることができる半導体装置の製造方法を提供する。

【解決手段】SiC基板11を薄板化した後、SiC基板11の厚み方向他方側の表面に、オーミック電極層17などを介して、サポート基板19を電気的および機械的に接合する。サポート基板19には、SiC基板11よりも体積抵抗率が低い基板を用いる。このようにしてSiC基板11とサポート基板19とを接合した後で、SiC基板11の厚み方向一方側のSBD2上に外部出力電極15などを形成して、半導体装置1を製造する。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術により倒れにくいマスクパターンを形成するNANDフラッシュメモリ等の製造方法を提供する。

【解決手段】非晶質シリコン膜21上に第1膜のシリコン酸化膜22を形成し(a)、所定のラインアンドスペースのパターンに加工して中間パターン23を形成する(b)。中間パターン23は、パターン部23aを有するとともに、パターン部23aの間に残存部23bを残してた状態で形成される。中間パターン23をスリミング処理し、非晶質シリコン膜21上に芯材パターン24を形成する(c)。残存部23bは除去される。芯材パターン24上に第2膜のシリコン窒化膜を形成し、エッチバック処理で側壁パターンを形成し、芯材パターン24を除去してマスクパターンを得る。マスクパターンは、段差のない非晶質シリコン膜21上に形成されるので応力差に起因した倒れの発生を抑制できる。

(もっと読む)

電子回路装置

【課題】ノーマリオフ型の炭化珪素接合FETはゲートの特性が、使い勝手が悪いという問題がある。これは、ノーマリオフを実現するためにゲート電圧が0Vでオフしていなければならず、かつ、ゲート・ソース間のpn接合に電流が流れないようにオン状態としてはゲート電圧を2.5V程度に抑える必要があるため、実質的にゲート電圧を0Vから2.5Vの間で制御しなければならないためである。従って、閾値電圧からオン状態のゲート電圧までが1Vから2V程度しかなく、ドレイン電流がゲート電圧の変化に非常に敏感であるため、ゲートの制御が難しい。

【解決手段】本願発明は、ノーマリオフ型の炭化珪素接合FETのゲートに、接合FETのゲート容量と同等か少し小さな容量を持つ素子を接続したものである。

(もっと読む)

101 - 120 / 644

[ Back to top ]