Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

121 - 140 / 542

半導体装置の作製方法

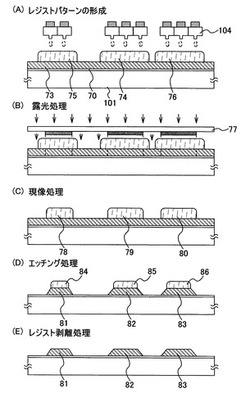

【課題】 レジスト材料の利用効率を向上させて、作製コストの削減を目的としたレジス

トパターンの作製方法、レジストパターンの除去方法、半導体装置の作製方法を提供する

ことを課題とする。

【解決手段】 本発明は、減圧下で、被加工物上に、感光剤を含む組成物を吐出してレジ

ストパターンを形成するステップを有することを特徴とする。また、前記レジストパター

ンをマスクとして前記被加工物をエッチングするステップ、若しくは、前記レジストパタ

ーンに、フォトマスクを介して前記感光剤の感光波長域の光を照射するステップ、前記レ

ジストパターンをマスクとして前記被加工物をエッチングするステップ、前記被加工物上

の前記レジストパターンを除去するステップを有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】第1導電型の第1の多結晶シリコン膜と第2導電型の第2の多結晶シリコン膜とを同時にエッチング加工する際の加工精度を向上するための製造方法の提供。

【解決手段】第1導電型の不純物を含む第1の多結晶シリコン膜103−1と、第2導電型の不純物を含む第2の多結晶シリコン膜103−2とを形成し、前記第1の多結晶シリコン膜をエッチングし、第1のパターンを形成するとともに、前記第2の多結晶シリコン膜をエッチングし、第2のパターンを形成するパターニング工程とを備える。パターニング工程は、第1のパターン及び第2のパターンのそれぞれの側面を露出させるようにエッチングを行う第1のエッチング工程と、露出した側面を酸化して側面に酸化膜を形成する酸化工程と、側面が酸化膜で保護された状態でエッチングを行い、第1の多結晶シリコン膜及び第2の多結晶シリコン膜のパターニングを完了させる第2のエッチング工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 酸化物半導体においてはイオン注入法による拡散層形成が難しいため、バルクシリコンMOSトランジスタや多結晶シリコンTFTのようなイオン注入法を用いた自己整合プロセスを組むことができない。本願では、リフトオフを用いる場合のような不都合の生じない自己整合プロセスを酸化物半導体において実現することを課題とする。

【解決手段】 裏面露光により製造される薄膜トランジスタ(TFT)において、チャネル層として酸化物半導体を用い、基板上の電極をマスクとして、基板の裏面側から導電膜上のネガレジストを露光し、ネガレジストの露光部分を残し前記ネガレジストを除去し、露光部分をエッチングマスクとする導電膜のエッチングにより、電極を加工する。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:酸化ランタンまたは酸化ランタニド(例えば、Dy2O3、Pr2O3、Ce2O3)を含む層を準備する工程と;炭酸水である水溶液を供給することにより、酸化ランタンまたは酸化ランタニドを含む層を特定の領域で除去して、酸化ランタンまたは酸化ランタニドを含む層が上に蒸着された表面を露出させる工程とを備える方法が開示されている。

(もっと読む)

半導体ウエハを処理するための方法

【課題】

【解決手段】半導体ウエハを処理するための方法であって:ハフニウムおよび/またはジルコニウムを含む第1の酸化物材料を含む高誘電体層と;前記高誘電体層の上部に蒸着され、ランタン、ランタニド、および/または、アルミニウムを含む第2の酸化物材料を含むキャップ層と、を備えたスタックを準備する工程と;酸化剤を含む水溶液である液体Aを前記半導体ウエハの表面に供給する工程SAと;工程SAの後に、6未満のpH値の液体である液体Bを前記半導体ウエハの前記表面に供給する工程SBと;工程SBの後に、少なくとも10ppmのフッ素濃度の酸性水溶液である液体Cを前記半導体ウエハの前記表面に供給する工程SCとを備える方法が開示されている。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ低抵抗の半導体装置およびその製造方法を提供すること。

【解決手段】基板と、前記基板上に形成された半導体層と、前記半導体層上に形成され、該半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極と、を備える。また、基板上に半導体層を形成する半導体層形成工程と、前記半導体層上に、前記半導体層の表面方向における幅が該半導体層の表面と垂直方向における高さ以上である櫛歯状の電極を形成する電極形成工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写加工技術を用いる場合に、転写用のマスクが非対称な形状となることに起因した不具合を極力防止する

【解決手段】半導体基板1上に、ゲート電極を形成するための膜を積層形成する。第1膜としてシリコン窒化膜8a、第2膜としてシリコン酸化膜9aを積層形成する。シリコン酸化膜9aを加工して芯材パターン9を形成する。ウェット処理によりシリコン窒化膜8aを選択的エッチングして、所定深さまで除去すると共に、芯材パターン9の直下に括れ部8bを形成する。非晶質シリコン膜11aを形成し、エッチバックによりスペーサパターン11を形成する。芯材パターン9をエッチングにより除去すると独立したスペーサパターン11を得ることができ、これをマスクとしてシリコン窒化膜8aをRIEエッチング加工しマスクパターン8を形成する。イオンが斜入しても芯材パターン9の直下部分が偏ったエッチング状態とならない。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極部と容量コンタクトプラグとのショートを防止する。

【解決手段】複数のゲート電極部10と該ゲート電極部10間を接続する配線部との上に、耐エッチング膜17を備えたゲートハードマスク20を形成後、前記配線部上の前記耐エッチング膜17を除去する。これにより、CMP処理を経てコンタクトプラグ22を形成し、さらに、エッチングにより容量コンタクトホール24を開口して容量コンタクトプラグ25を形成した場合に、ゲート電極部10と容量コンタクトプラグ25とのショートを防止することができる。

(もっと読む)

半導体装置の製造方法

【課題】メモリセルトランジスタのゲート電極MGと選択ゲートトランジスタのゲート電極SGとの微細パターン形成で、ゲート電極MG−SG間の配置間隔を狭くできるようにする。

【解決手段】シリコン基板1に、ゲート絶縁膜4を形成し、ゲート電極用の膜を積層する。シリコン窒化膜8を積層し、その上にシリコン酸化膜からなる芯材パターン9を形成する。ゲート電極SG−SG間は広い間隔に配置させる。非晶質シリコン膜10を形成し、RIE法でスペーサ10aを形成した後、芯材パターン9を除去する。ネガ型レジスト膜11を塗布し、スペーサ10aの上部が露出する膜厚に加工する。所定波長の光で露光し、スペーサ10aの配置間隔が広いゲート電極SG部分にネガ型レジスト膜11を残す。RIE加工でゲート電極MGを形成し、こののちフォトリソグラフィ処理でゲート電極SGを形成する。

(もっと読む)

ヘテロ接合バイポーラトランジスタの製造方法

【課題】アスペクト比の高いサブミクロンサイズのエミッタ電極パタンを線幅制御性良く形成することを可能とするヘテロ接合バイポーラトランジスタの製造方法を提供すること。

【解決手段】エミッタコンタクト層6上にTi層(図示せず)、エッチングストッパー用のW層7、Au層8、エッチングマスク用W層9、フォトレジストパタン10を形成し、フォトレジストパタン10をマスクとしてエッチングマスク用W層9を選択的に除去することによってWパタン9とし、Wパタン9をマスクとして、Au層8を、酸素ガスを含有する混合ガスを用いる反応性イオンエッチング法により選択的に除去し、Wパタン9をマスクとして、エッチングストッパー用のW層7、Ti層を選択的に除去することを特徴とするヘテロ接合バイポーラトランジスタの製造方法を構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】MIPS構造を有する電界効果トランジスタにおいて、金属ゲート電極とポリシリコンゲート電極との接触抵抗を低減することにより、AC動作を向上させる。

【解決手段】半導体装置1は、半導体基板10上に電界効果トランジスタを有する。電界効果トランジスタは、ゲート絶縁膜25、27とゲート電極63、71と、を備える。さらに、ゲート電極63、71は第1金属からなる第1電極層22と、第2金属からなる第2電極層26、34と、シリコン層からなる第3電極層62、70と、を含む積層構造である。第2金属は、シリコン層の多数キャリアに対する第1電極層22と第3電極層62、70とのバンド不連続を緩和する仕事関数を有する材料である。

(もっと読む)

ドライエッチング方法及び金属薄膜のパターニング方法

【課題】難エッチング材料を不活性ガスによりエッチングする際に残渣なく加工する方法を提供する。

【解決手段】難エッチング性の金属薄膜2上に、断面形状がハンマーヘッド型となるようにレジスト4を形成した後に前記金属薄膜をドライエッチングし、その後前記レジストを除去する。前記ハンマーヘッド型の断面形状を有するレジストパターンは、現像液に対する溶解速度が異なる2種類のレジストを積層塗布して露光・現像することによって得る。

(もっと読む)

半導体装置及びその製造方法

【課題】微細化に対応可能であり、不純物拡散領域上に形成したコンタクトプラグが近傍の導電材料とショートすることを防止する配線構造を有する半導体装置を提供する。

【解決手段】半導体基板内の不純物拡散領域22上に選択エピタキシャル成長法により、第1の層16aを形成する工程と、第1の層16a上に、選択エピタキシャル成長法により第2の層18を形成する工程と、第2の層18上に導電材料を充填することにより、コンタクトプラグ21を形成する工程と、を有する。

(もっと読む)

メッシュ構造を有する電極を具備した太陽電池及びその製造方法

【課題】低抵抗と高透過性を併せ持ち、さらに太陽光を効率よくキャリアの励起に利用できる、安価な材料を用いた光入射面側電極を備えた太陽電池、及びその製造方法を提供する。

【解決手段】本発明の太陽電池は、光電変換層と、光入射面側電極層と、対向電極層とを具備し、前記光入射面側電極層が前記層を貫通する複数の開口部を有し、かつその膜厚が10nm以上200nm以下の範囲にあり、前記開口部の1つあたりの面積が80nm2以上0.8μm2以下の範囲にあり、開口部の開口率が10%以上66%以下の範囲にあり、光吸収層の少なくとも一部が、前記光入射面側電極層と前記光電変換層の接触面から1μm以内の距離に配置されていることを特徴とする。この電池の光入射面側電極層は、微粒子の単粒子層や、ブロックコポリマーの自己組織化によるドットパターンをマスクにエッチングしたり、スタンパーを利用して形成させることができる。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極を形成するときのハードマスクを除去するときにゲート絶縁膜の側面がエッチングされることを抑制し、かつ、サイドウォールの上端がゲート電極の上面より上に位置することを抑制する。

【解決手段】ゲート絶縁膜110上に、ゲート電極126となる導電膜120を形成する。次いで、導電膜120上に、ハードマスクパターン70を形成する。次いで、ハードマスクパターン70をマスクとして導電膜120を選択的に除去することにより、ゲート電極126を形成する。次いで、ゲート電極126の側面に第1のサイドウォール140を形成する。次いで、ハードマスクパターン70をウェットエッチングにより除去する。ハードマスクパターン70を形成した後、第1のサイドウォール140を形成する前に、ハードマスクパターン70の側面52を、上に行くにつれてハードマスクパターン70の幅が狭くなる方向に傾斜させる。

(もっと読む)

パターン形成方法

【課題】微細化したホール又はラインのパターンを、従来よりも容易に形成する製造方法を提供する。

【解決手段】被加工膜(2)上に第1のカーボン膜(3)と第1のARL(4)を順次堆積し、第1のARLをパターニングする工程、第2のカーボン膜(6)と第2のARL(7)を順次堆積し、第2のARLをパターニングする工程と、第2のARLをマスクとして第2のカーボン膜を除去する工程と、露出した第1のARLとをマスクとして、第1のカーボン膜を除去する工程と、残存している第1及び第2のカーボン膜をマスクとして被加工膜のエッチングを行う工程とを備えている。

(もっと読む)

トランジスタ素子の製造方法

【課題】 ゲート電極に対して、ソース・ドレイン電極を正確に位置合わせし、寄生容量の発生を抑制する。

【解決手段】 透明ガラス基板310上に金属からなるゲート電極320を形成し、その上に、透明なゲート絶縁層330を形成し、更に、ソース・ドレイン電極350・360の元になるITOからなる導電層を形成し、その上面をネガ型レジスト層で覆う。ソース・ドレイン形成領域を含む所定領域が透光性を有するマスクを、基板の下面側に配置する。下方から光を照射し、マスクの遮光領域によって生じる影とゲート電極320によって生じる影とが、レジスト層の非露光領域となるような背面露光を行い、パターニングしてソース電極350およびドレイン電極360を形成する。その上に、InGaZnO4からなる酸化物半導体のチャネル層340を直接形成して、高濃度不純物拡散層を省略しつつ、良好なオーミック接触を得る。

(もっと読む)

121 - 140 / 542

[ Back to top ]