Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

141 - 160 / 542

パターン形成方法

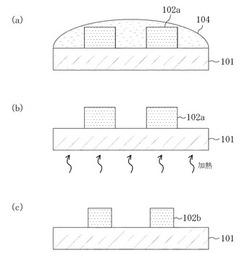

【課題】パターン形状に優れた、トリミング法によるパターン形成方法を簡易に実現できるようにする。

【解決手段】基板101の上に光酸発生剤を含むポジ型のレジスト膜102を形成する。その後、レジスト膜102に露光光を選択的に照射してパターン露光を行う。続いて、パターン露光が行われたレジスト膜102に第1の加熱を行い、加熱されたレジスト膜102に第1の現像を行って、第1のレジストパターン102aを形成する。続いて、第1のレジストパターン102aを、熱酸発生剤を含み且つポリマー及び架橋剤を含まない溶液104にさらし、溶液104にさらされた第1のレジストパターン102aに第2の加熱を行う。その後、加熱された第1のレジストパターン102aに第2の現像を行って、第1のレジストパターン102aが縮小された第2のレジストパターン102bを得る。

(もっと読む)

トランジスタ素子の製造方法

【課題】 ソース・ドレイン電極に対して、ゲート電極を正確に位置合わせし、寄生容量の発生を抑制する。

【解決手段】 透明ガラス基板110上に金属からなるソース電極120,ドレイン電極130を形成し、その上に、InGaZnO4からなる透明な酸化物半導体チャネル層140を形成し、その上面に透明な絶縁層150を形成する(図8(a) )。その上に、ITOからなる導電層185を形成し、その上面をネガ型レジスト層191で覆う(図8(b) )。基板下面にゲート形成用マスクM3を配置して下方から光を照射し、マスクM3の遮光領域によって生じる影とソース電極120およびドレイン電極130によって生じる影とが、レジスト層191の非露光領域となるような背面露光を行い、パターニングしてゲート電極層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】半導体基板に対して略垂直な形状のゲート電極を有する半導体装置の製造方法を提供する。

【解決手段】半導体基板11の主面11aにゲート絶縁膜12を介して形成された金属含有膜19を有するゲート電極膜30上にマスク材31を形成し、マスク材31を用いてゲート電極膜30をゲート絶縁膜12が露出するまで異方性エッチングし、ゲート電極13を形成する工程と、金属含有膜19を酸化し、金属含有膜19の側壁に酸化膜34を形成する工程と、ゲート絶縁膜12を等方性エッチングし、半導体基板11上に露出したゲート絶縁膜12を除去するとともに、半導体基板11と金属含有膜19との間に挟まれたゲート絶縁膜12を後退させる工程と、金属含有膜19を選択的に等方性エッチングし、金属含有膜19のゲート絶縁膜12より外側に突出した部位を除去する工程と、を具備する。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写プロセスによりパターンを形成するときに、被加工膜の加工形状差を抑制できるようにする。

【解決手段】シリコン窒化膜10の上にシリコン酸化膜11を形成し、リソグラフィによりパターニングし、シリコン酸化膜11をスリミング技術によりスリミングし、シリコン酸化膜11の上面および側面並びにシリコン窒化膜10の上面上に沿って非晶質シリコン膜13を堆積する。非晶質シリコン膜13を異方性エッチング処理することでシリコン酸化膜11の側面に沿ってスペーサ状に残留させる。次に、シリコン酸化膜11の上端11aが非晶質シリコン膜13の上端13aよりも低くなるようにエッチング処理し、非晶質シリコン膜13の上面13bを上に凸となる湾曲面に形成する。

(もっと読む)

半導体装置の製造方法

【課題】導電層と絶縁層とが積層された構造に貫通ホールを一括して形成可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上にシリコン酸化物を含む絶縁層17とシリコンを含む導電層WLとの積層体を形成する工程と、絶縁層17及び導電層WLを貫通するホール50を積層体に形成する工程とを備え、ホール50の形成工程は、積層体上にシリコン酸化物を含む第1のマスク層41を形成する工程と、第1のマスク層41をマスクにして導電層WLをエッチングする工程と、第1のマスク層41上に絶縁層17よりもシリコン含有量が多い第2のマスク層42を形成し第2のマスク層42をマスクにして、絶縁層17をエッチングする工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗な電極部を有し、且つパターニング工程数の削減可能な半導体装置及びその製造方法を提供する。

【解決手段】拡散層が形成された半導体基板の上に第1の金属層を形成する工程と、前記第1の金属層の上に開口部を有する絶縁層を形成する工程と、前記絶縁層の開口部において、前記第1の金属層の上に第2の金属層を形成する工程と、前記絶縁層を除去する工程と、前記第2の金属層の露出面に前記第2の金属層よりもイオン化傾向の小さい金属を含む第3の金属層を被覆する工程と、前記第3の金属層をマスクとして前記第1の金属層を除去することにより、前記第1の金属層と前記第2の金属層と前記第3の金属層とを有する電極配線を形成する工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

半導体装置の製造方法及び設計支援装置

【課題】コンタクト領域の欠損を抑制する技術を提供する。

【解決手段】半導体装置の製造方法は、基板上方に導電膜を形成し、導電膜上に補助パターンを形成し、導電膜及び補助パターンを覆うように金属膜を形成し、金属膜をエッチバックし、補助パターンの側面にサイドウォール膜を形成し、補助パターンを除去し、導電膜及びサイドウォール膜の一部を覆い、一部を露出させるレジストパターンを形成し、レジストパターンをマスクとしてエッチングによりサイドウォール膜の露出している部分を除去し、サイドウォール膜をマスクとして導電膜をエッチングして、ゲート電極及びゲート電極と導通するコンタクト領域を形成し、露出している部分が除去されることにより導電膜上に残存するサイドウォール膜の形状は、ゲート電極及びコンタクト領域の形状に対応し、補助パターンの形状は、コンタクト領域の形状に対応するサイドウォール膜の少なくとも三辺と接する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極とコンタクト配線のショート不良を防止できる半導体装置の製造方法を提供する。

【解決手段】半導体基板32上にゲートハードマスク、ゲート電極34及びゲート絶縁膜33を形成する。ゲートハードマスクの線幅をゲート電極よりも狭くした後、S/Dエクステンション36を形成する。全面にシリコン酸化膜を堆積形成し、エッチバックしてゲート電極の側壁から上面の一部上に渡って連続的に残存させた絶縁部材37を形成する。ゲートハードマスクを除去した後、ゲート電極と絶縁部材をマスクにしてコンタクトジャンクション38を形成する。金属シリサイド膜を形成後、シリコン窒化膜40と層間絶縁膜41を順次堆積形成する。層間絶縁膜にコンタクトホールを形成し、続いてシリコン酸化膜との選択比が高い異方性エッチングによってシリコン窒化膜を除去することでコンタクトホールを開孔し、コンタクト配線43を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】

メタルゲートを有するpチャネルMISトランジスタとメタルゲートを有するnチャネルMISトランジスタとを、少ない工程数で形成する。

【解決手段】

半導体装置は、シリコン層を有する半導体基板と、半導体基板に画定されたn型活性領域とp型活性領域と、n型活性領域の上方に形成され、酸化シリコンより高い誘電率を有し、表面にAlを含有する第1高誘電率ゲート絶縁膜と、p型活性領域の上方に形成され、酸化シリコンより高い誘電率を有する第2高誘電率ゲート絶縁膜と、第1高誘電率ゲート絶縁膜および第2高誘電率ゲート絶縁膜の各々の上に形成され、nチャネルトランジスタに適した仕事関数を有する金属又は金属化合物を含む材料で形成された、第1ゲート電極および第2ゲート電極と、を有することを特徴とする。

(もっと読む)

メモリデバイス及びメモリデバイスの形成方法

【課題】プログラマブルMOSFET(105)とロジックMOSFET(110)とを含むメモリデバイスを同一チップ上に形成する。

【解決手段】半導体基板を被う層状ゲート積層体の成形から始まり、層状ゲート積層体の高kゲート電極層上で停止するよう金属ゲート電極層にパターンを形成して、半導体基板上に第1、第2ゲート金属ゲート電極(16、21)を形成するメモリデバイスの製法が提供される。次のプロセスで、高kゲート誘電体層の一部を被う少なくとも1つのスペーサ(55)を第1ゲート電極(16)に形成する。高kゲート誘電体層の露出された残存部分をエッチングし、第1金属ゲート電極のサイドウォールを越えて延びる部分を有する第1高kゲート誘電体(17)及び第2金属ゲート電極(21)のサイドウォールに整合されたエッジを有する第2高kゲート誘電体(22)を形成する。

(もっと読む)

半導体素子およびその製造方法

【課題】 サドルフィン形態のチャンネルを形成する際に、ゲートパターンとプラグとの間のブリッジ発生を防止することが可能な半導体素子およびその製造方法を提供する。

【解決手段】 半導体素子は、半導体基板と、半導体基板内に活性領域を限定するように形成された素子分離膜と、活性領域および素子分離膜に形成されたゲート用リセスパターンと、リセスパターン内およびリセスパターン上に形成されたゲートパターンと、ゲートパターンを覆うように形成されたゲートスペーサとを含み、ゲート用リセスパターンは、活性領域では第1深さを有し、素子分離膜では第1深さよりも深い第2深さを有し、ゲートパターンと素子分離膜のゲート用リセスパターン上部側面との間には空間が形成されて、ゲートスペーサが前記空間を埋め立てる。

(もっと読む)

二回のカット工程によって多結晶シリコンのライン端部短縮の問題を解決する方法

【課題】ゲートストリップを二回のカット工程によって端部を改善する製造方法の提供。

【解決手段】第1アクティブ領域40と、第2アクティブ領域42とを有する基板を提供するステップと、基板にゲート電極層を形成するステップと、第1ゲートストリップ60と、第1ゲートストリップに実質的に平行する第2ゲートストリップ62と、第1アクティブ領域と第2アクティブ領域の間に位置して、第1ゲートストリップと第2ゲートストリップに平行していないが、互いに接続する犠牲ストリップ66とを残すように、ゲート電極層をエッチングするステップと、第1ゲートストリップと第2ゲートストリップの一部を覆い、犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部を開口部に露出させる遮蔽部を形成するステップと、開口部に露出される犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部をエッチングするステップを含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層に新たな機能を有する素子を設けた半導体装置を提供する。

【解決手段】半導体基板上に形成された第1配線層150、及び半導体素子200を備える。第1配線層150は、絶縁層156と、絶縁層156の表面に埋め込まれた第1配線154とを備える。半導体素子200は、半導体層220、ゲート絶縁膜160、及びゲート電極210を備える。半導体層220は、第1配線層150上に位置する。ゲート絶縁膜160は、半導体層220の上又は下に位置する。ゲート電極210は、ゲート絶縁膜160を介して半導体層220の反対側に位置する。

(もっと読む)

半導体装置の作製方法

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチング工程において、第1のエッチング工程は、エッチングガスによるドライエッチングを用い、第2のエッチング工程はエッチング液によるウエットエッチングを用いる。

(もっと読む)

半導体装置の作製方法

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチング工程は、エッチングガスによるドライエッチングを用いる。

(もっと読む)

電子デバイスの製造方法及び設定装置

【課題】電子デバイスの更なる微細化及び高集積化が進んでも、リソグラフィー及びエッチングにより被加工対象の極めて高い寸法精度を達成し、信頼性の高い電子デバイスを実現する。

【解決手段】被加工対象上に形成されたレジスト膜を加工してレジストパターンを形成する工程と、レジストパターンをマスクとして、所定のエッチング条件で被加工対象をエッチングする工程とを実行する際に、形成されたレジストパターンの寸法及び形状(膜厚及びテーパ角度)を測定し、測定されたレジストパターンの寸法及び形状に基づいて前記エッチング条件を調整する。

(もっと読む)

半導体素子の製造方法

【課題】パターニングされた被エッチング膜のシリサイド化を簡便に行うことのできる半導体素子の製造方法を提供する。

【解決手段】本発明の半導体素子の製造方法は、ポリシリコン膜21上にSiO2 膜22をパターンニングし、SiO2 膜22を覆うようにポリシリコン膜23を堆積した後、SiO2 膜22の側壁部分にポリシリコン電極23aを形成する。次いで、SiO2 膜22を除去した後、堆積したSiO2 膜24をエッチバックして電極23aの側壁部にSiO2 からなるサイドウォール24aを形成する。次いで、サイドウォール24aの間にポリシリコンを埋め込むことによってポリシリコン電極23bを形成し、サイドウォール24aを除去して、ポリシリコン膜21およびポリシリコン電極23a,23bをエッチバックすることでポリシリコン膜21をパターンニングする。

(もっと読む)

蒸着用マスク

【課題】弊害なくたわみを回避できる蒸着用マスクを提供する。

【解決手段】被蒸着体であるウェハと接するウェハ対向面と、該ウェハ対向面と反対の面であり蒸着源と対向する蒸着源対向面15と、該ウェハ対向面と該蒸着源対向面15とを貫通する開口を有するマスク開口領域14と、該開口の形成されない領域である無効領域12とを有する。そして、該蒸着源対向面15の該無効領域12に付加された線状の補強部材16を備えることを特徴とする。

(もっと読む)

表示装置およびその作製方法

【課題】表示パネルに設けられる共通接続部として適した構造を提供することを目的の一とする。

【解決手段】画素部の外側領域に設けられる共通接続部は、ゲート絶縁層と同じ層で形成された絶縁層上に、第2酸化物半導体層と同じ層で形成された酸化物半導体層と、導電層と同じ層で形成された導電層(共通電位線とも呼ぶ)とが積層された構成を有し、第1酸化物半導体層上に設けられた層間絶縁層の開口部を介して導電層(共通電位線とも呼ぶ)が共通電極と接続しており、画素電極と対向する電極が導電性粒子を介して共通電極と電気的に接続する。

(もっと読む)

半導体装置の製造方法

【課題】疎部及び密部のそれぞれにおいて、所望の寸法のデバイスパターンを簡単にエッチングにより形成できるようにする。

【解決手段】金属層12上に2層のマスク層13,14を形成する工程と、2層のマスク層13,14に対して、各層ごとに、デバイスパターンを疎に形成する疎部または密に形成する密部におけるCDシフト量を調整する1種類のエッチングパラメータを変更させてエッチングを行い、マスクパターン13−1〜13−4,14−1〜14−4を形成する工程と、マスクパターン13−1〜13−4を用いて金属層12をエッチングし、ゲート電極12−1〜12−4を形成する。

(もっと読む)

141 - 160 / 542

[ Back to top ]