Fターム[4M104DD71]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | パターニング用マスク (645)

Fターム[4M104DD71]の下位に属するFターム

エッチングストッパ (103)

Fターム[4M104DD71]に分類される特許

1 - 20 / 542

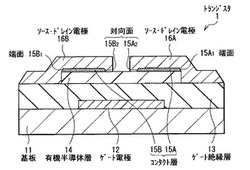

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】酸化物半導体層、及びチャネル保護層を覆うようにソース電極層、及びドレイン電極層となる導電膜を形成した後、酸化物半導体層、及びチャネル保護層と重畳する領域の導電膜を化学的機械研磨処理により除去する。ソース電極層、及びドレイン電極層となる導電膜の一部を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、チャネル保護層を有することにより、導電膜の化学的機械研磨処理時に当該酸化物半導体層に与える損傷、または膜減りを低減できる。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】レジスト層、中間層、レジスト層のパターン形状をさらに良好にする半導体装置の製造方法を提供する。

【解決手段】下層フォトレジスト7、無機材料の中間層8、上層フォトレジスト9を形成し、上層フォトレジスト9をパターニングして上層レジストパターン9aを形成し、半導体基板1をチャンバー内の下部電極上に設置し、チャンバー内に二酸化硫黄ガス、酸素ガスを有する第1反応ガスを導入してプラズマを発生させるとともに下部電極への高周波電力の供給を切断して上層レジストパターン9aをトリミングし、第1反応ガスを第2反応ガスに置換するとともに下部電極に高周波電力を供給して上層レジストパターン9aをマスクにして中間層8をエッチングして中間層パターン8aを形成し、第2反応ガスを第3反応ガスに置換してプラズマを発生させるとともに下部電極に高周波電力を供給して中間層パターン8aをマスクにして下層フォトレジスト層7をエッチングする。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】ワード線抵抗を低減し、かつ、周辺回路のトランジスタの特性変化を抑制することができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、複数のメモリセルと、周辺回路とを備える。メモリセルは、半導体基板の上方に設けられたフローティングゲートと、フローティングゲート上に設けられたゲート間絶縁膜と、ゲート間絶縁膜上に設けられたコントロールゲートとを含む。周辺回路は、互いに電気的に接続されたフローティングゲートおよびコントロールゲートと、少なくともフローティングゲートとコントロールゲートとの間の電気的接触部分に設けられ該フローティングゲートと該コントロールゲートとの間の電気的接続を妨げない絶縁薄膜とを含むトランジスタを含む。複数のメモリセルは、コントロールゲート内に絶縁薄膜を含まない。メモリセルおよび周辺回路において、コントロールゲートの少なくとも上部はシリサイド化されている。

(もっと読む)

半導体装置

【課題】短チャネル効果の抑制およびオフリーク電流の抑制が可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置は、半導体基板において素子分離領域によって仕切られた素子領域と、前記素子領域を横切る所定の方向に沿って前記素子領域の表層に設けられたゲートトレンチにより分離されて前記素子領域の表層に形成されたソース領域およびドレイン領域とを備える。また、実施形態の半導体装置は、少なくとも一部が前記ゲートトレンチ内にゲート絶縁膜を介して埋め込まれて前記ソース領域およびドレイン領域よりも深い位置まで形成されたゲート電極を備える。ドレイン領域における前記ゲート絶縁膜と接触する界面は、前記ゲート電極側に突出した凸部を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

1 - 20 / 542

[ Back to top ]