Fターム[4M104DD83]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の処理 (7,014) | 固相反応 (1,946)

Fターム[4M104DD83]の下位に属するFターム

Fターム[4M104DD83]に分類される特許

1 - 20 / 303

炭化珪素半導体装置の製造方法

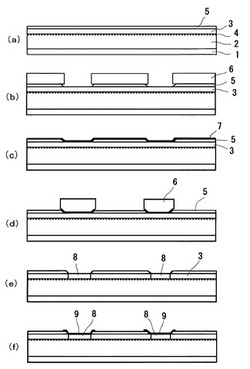

窒化物半導体装置の製造方法

【課題】低温の加熱処理によって、コンタクト抵抗の低いオーミック電極を形成することができる方法を提供する。

【解決手段】窒化物半導体層のオーミック電極形成領域に、インジウムあるいはゲルマニウムのような低融点金属7を積層し、低融点金属の融点近傍の低温で加熱処理することにより、窒化物半導体層中に低融点金属が拡散させ、合金層8を形成することによりオーミック接触を形成する。窒化物半導体層表面に残るインジウムあるいはゲルマニウムを除去した後、配線のための金属層9を形成する。

(もっと読む)

炭化珪素半導体装置

【課題】ボンディング耐性を向上させた炭化珪素半導体装置及びその製造方法を提供することを目的とする。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、炭化珪素基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に平面視してリング状に形成された低濃度p型JTE領域3と、n型炭化珪素層2の表面近傍の低濃度p型JTE3の内側に該低濃度p型JTE領域3に接触して平面視してリング状に形成された高濃度p型領域4と、高濃度p型領域4上の一部に形成されたp型オーミック電極5と、p型オーミック電極5を覆うと共に高濃度p型領域4上及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】ショットキー電極形成前に酸洗浄を行ってもp型オーミック電極がその酸に曝されることなく、p型オーミック電極とショットキー電極との電気的接続が良好な炭化珪素半導体装置及びその製造方法を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に形成された複数のp型不純物領域3と、p型不純物領域3上の一部に形成されたp型オーミック電極4と、p型不純物領域3上の一部に、p型オーミック電極4を覆うように形成された耐酸性のバリアメタル層5と、バリアメタル層5、p型不純物領域3、及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板1のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】低コンタクト抵抗を実現し得る半導体基板上の半導体層と電極配線層とのオーミック電極構造を提供する。

【解決手段】半導体基板106と、半導体基板106上に形成された第1のバリア層107と、第1のバリア層107上に形成された厚さ1nm以上40nm以下のチャネル層108と、チャネル層108の上に形成された第2のバリア層102と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第1の電極領域109と、少なくとも第2のバリア層102及びチャネル層108を厚さ方向に貫通する第2の電極領域109とを備える半導体装置であって、少なくとも第1の電極領域109は、チャネル層108と接触する側の面が凹凸形状で構成されている。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】中間層の形成時に、第2コイル46および第3コイル61によってターゲット53と基体11との間に磁力線M1が通るように磁場を発生させることによって、溝部12の内壁面に均一な厚みで中間層を成膜することが可能になる。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

半導体発光装置及びその製造方法

【課題】高いオーミック性と反射率を併せ有する電極構造を備える、低駆動電圧で駆動し、良好な光取り出し効率を有する半導体発光装置及びその製造方法を提供すること。

【解決手段】n型半導体層と、p型半導体層と、前記n型半導体層と前記p型半導体層との間に設けられた活性層と、前記n型半導体層に接して設けられたn電極と、前記p型半導体層に接して設けられたp電極とを具備する半導体発光素子。前記p電極が前記p型半導体層上に少なくとも一部が網目状に形成されたNiO層と、このNiO層に接して形成されたAg層とを含む。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】超音波振動を利用したワイヤーボンディングの際に、p型オーミック電極がp型不純物拡散領域の面上から剥離することを防止する。

【解決手段】パッド電極7にボンディングワイヤー8を接合する際に、ボンディングツール100を用いて、ボンディングワイヤー8をパッド電極7に接触させた状態で、ボンディングワイヤー8に荷重を加えながら、p型オーミック電極5の長手方向に沿って超音波振動を印加する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】製造工程等で高温下に曝された場合であっても、半導体領域と電極との間での原子の相互拡散が抑制され、かつ界面抵抗の上昇が抑えられる半導体素子を提供すること、及びこのような半導体素子の製造方法を提供することを目的とする。

【解決手段】本発明は、シリコンを含む半導体領域、アルミニウムを主成分として含む電極、及び上記半導体領域と電極との間に介在し、ゲルマニウムを含有する拡散防止層を備え、上記拡散防止層の少なくとも一部のゲルマニウム含有量が4原子%以上である半導体素子である。本発明の半導体素子の製造方法は、シリコンを含む半導体領域の表面に、ゲルマニウムを含むアルミニウム合金膜を形成する工程、及び上記アルミニウム合金膜が形成された半導体領域に熱処理を行う工程を有する。

(もっと読む)

半導体装置の製造方法

【課題】二酸化珪素からなる層間絶縁膜を挟んでアルミニウムを含む電極とゲート電極とを配置した場合に、当該アルミニウムを含む電極とゲート電極とが短絡することを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】MOSFET100の製造方法は、活性層7上にゲート酸化膜91を形成する工程と、ゲート酸化膜91上にゲート電極93を形成する工程と、活性層7に対してオーミック接触するソースコンタクト電極92を形成する工程と、ソースコンタクト電極92が形成された後、ゲート電極93を覆うように二酸化珪素からなる層間絶縁膜94を形成する工程とを備え、ソースコンタクト電極92を形成する工程は、活性層7に接触するようにアルミニウムを含む金属層を形成する工程と、金属層を合金化する工程とを含む。

(もっと読む)

半導体装置およびその作製方法

【課題】微細化に伴う短チャネル効果を抑制しつつ、トランジスタの電気特性のしきい値電圧(Vth)をプラスにすることができ、所謂ノーマリーオフを達成した半導体装置、及びその作製方法を提供する。また、ソース領域、及びドレイン領域と、チャネル形成領域との間のコンタクト抵抗を低くして良好なオーミックコンタクトがとれる半導体装置、及びその作製方法を提供する。

【解決手段】酸化物半導体層を有するトランジスタにおいて、少なくともチャネル形成領域となる、酸化物半導体層の一部をエッチングによって部分的に薄くし、そのエッチングによってチャネル形成領域の膜厚を調節する。また、酸化物半導体層の厚い領域に、リン(P)、またはホウ素(B)を含むドーパントを導入し、ソース領域、及びドレイン領域を酸化物半導体層中に形成することにより、ソース領域、及びドレイン領域と接続するチャネル形成領域とのコンタクト抵抗を低くする。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】Ge基板上に形成されたPチャネル型MISFETの第1ソースおよび第1ドレインが、Ge原子とニッケル原子との化合物、Ge原子とコバルト原子との化合物またはGe原子とニッケル原子とコバルト原子との化合物からなり、III−V族化合物半導体からなる半導体結晶層に形成されたNチャネル型MISFETの第2ソースおよび第2ドレインが、III族原子およびV族原子とニッケル原子との化合物、III族原子およびV族原子とコバルト原子との化合物、または、III族原子およびV族原子とニッケル原子とコバルト原子との化合物からなる半導体デバイスを提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置においてオーミック特性を良好にし、かつ、酸・アルカリによる腐食に対し高い耐性を有することが可能な技術を提供することを目的とする。

【解決手段】半導体装置は、不純物が添加された高濃度不純物領域2を有する窒化物半導体層1と、高濃度不純物領域2上に順に積層された下地電極層3及び主電極層4を含む電極11とを備える。主電極層4は、窒化物半導体層1に対して下地電極層3よりも仕事関数が近い第1金属と、水素よりもイオン化傾向が小さい第2金属とからなる合金を主成分として含む。下地電極層3は、主電極層4よりも窒素との反応性が高い金属を主成分として含み、かつ、第1金属を含む。

(もっと読む)

化合物半導体装置の製造方法

【課題】 短チャンネル効果が抑制され、メタルS/Dを有するInGaAs−MOSFETの低消費電力化をはかり得る化合物半導体装置を製造する。

【解決手段】 InGaAsをチャネルに用いた化合物半導体装置の製造方法であって、基板上のInGaAs層10上に、ゲート絶縁膜11を介してゲート電極12を形成した後、ゲート電極12の両側に露出するInGaAs層10上に、厚さ5.5nm以下のNi膜14を形成する。次いで、250℃以下の温度で熱処理を施すことにより、Ni膜14とInGaAs層10とを反応させて、ショットキー・ソース/ドレインとなるNi−InGaAs合金層15を形成する。

(もっと読む)

半導体装置の製造方法

【課題】設計された形状およびサイズのゲート電極を形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】本実施形態に係る半導体装置の製造方法は、半導体層12の表面上のうち、互いに離間した位置に、チタン層17a、18a、アルミニウム層17b、18b、ニッケル層17c、18c、金層17d、18dがこの順で積層した積層体17、18を形成し、これらを、アルミニウムの融点より高い温度で加熱して複数の金属体17´、18´を形成するするとともに、これらの複数の金属体17´、18´を半導体層12にオーミック接触させる。この後、複数の金属体17´、18´を薄膜化して複数の合金層13a、14aを形成し、合金層13a、14aを含むドレイン電極13およびソース電極14を形成する。次に、ドレイン電極13とソース電極14との間のレジスト層19に開口部20し、この開口部20内にゲート電極15を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線の低抵抗化を図る。

【解決手段】本実施形態の半導体装置は、半導体基板10を覆う第1の層間絶縁膜上に設けられる配線60と、配線60の上面上に設けられるキャップ層68と、配線60と第2の層間絶縁膜との間に設けられるバリア膜62と、を含む。配線60は高融点導電層を含み、配線60の配線幅W1は、キャップ層68の幅W2よりも小さい。バリア膜62は、高融点導電層60が含む元素の化合物からなり、配線60を覆う層間絶縁膜69,70に起因する不純物が配線60内に拡散するのを抑制する。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチの対向する側面上に互いに離間されたゲート電極を有する半導体装置において、微細化に対応することができる半導体装置の製造方法を提供する。

【解決手段】トレンチ4を形成する工程およびゲート絶縁膜6を形成する工程では、トレンチ4のうち第2導電型層3と接する部分を中間部したとき、トレンチ4の対向する側面に形成されたゲート絶縁膜6の間隔において、トレンチ4の開口部に形成されている部分の間隔W1がトレンチ4の中間部に形成されている部分の間隔W2より狭くなるトレンチ4およびゲート絶縁膜6を形成する。そして、導電膜7aを形成する工程では、トレンチ4に導電膜7aで囲まれる空隙14を形成しつつ、導電膜7aを形成する。その後、ゲート電極7を形成する工程では、導電膜7aを異方性エッチングし、空隙14を介してトレンチ4の底面に形成された導電膜7aを除去してゲート電極7を形成する。

(もっと読む)

SiC半導体デバイス及びその製造方法

【課題】SiC半導体デバイスにおいて、裏面電極の剥離を十分に抑制することができる製造方法と、裏面電極の剥離が防止された新規な裏面電極構造を有するSiC半導体デバイスを提供する。

【解決手段】SiC半導体上へチタン及びニッケルを含む層を形成して、加熱によりチタンカーバイドを含むニッケルシリサイド層を形成させ、析出した炭素層を逆スパッタにより除去することにより、後工程でニッケルシリサイド上に形成される金属層の電極が剥離することを抑制する。炭素層を除去する前のニッケルシリサイド表面の、析出した炭素の量とチタンカーバイドの炭素量の関係が、所定の条件のときに、さらに剥離防止の効果を向上させることができる。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

1 - 20 / 303

[ Back to top ]