Fターム[4M104EE01]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412)

Fターム[4M104EE01]の下位に属するFターム

Fターム[4M104EE01]に分類される特許

1 - 20 / 123

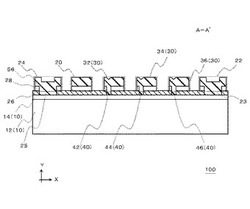

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置

【課題】逆方向リーク電流および閾値電圧を低減することができる半導体装置を提供すること。

【解決手段】表面12および裏面11を有するSiCエピタキシャル層6の表面12に接するように、アノード電極27をショットキー接合させる。そして、ショットキーバリアダイオード1の閾値電圧Vthを0.3V〜0.7Vにし、定格電圧VRにおけるリーク電流Jrを1×10−9A/cm2〜1×10−4A/cm2にする。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】SiCを用いて、逆方向特性が良好なショットキーダイオードを高い歩留まりで得る。

【解決手段】図1(b)に示されるように、バリアメタル21を部分的にエッチングする(電極層エッチング工程)。電極層エッチング工程によってバリアメタル21がエッチングされた領域における半導体層10中に、埋め込み絶縁層を形成する(埋め込み絶縁層形成工程)。図1に示される製造方法においては、この埋め込み絶縁層形成工程は、半導体層エッチング工程、絶縁層形成工程、エッチバック工程からなる。

(もっと読む)

炭化珪素ショットキダイオード

【課題】本発明の目的は耐圧変動が抑制された炭化珪素ショットキダイオードを提供する。

【解決手段】本発明の炭化珪素ショットキダイオードは、炭化珪素半導体基板1の表面に形成されるショットキ電極2と、その周囲を取囲むべく、炭化珪素半導体基板の表面に不純物が導入されて成るガードリング3と、該ガードリング上に延在すると共に当該ガードリングの周囲を取囲むように前記炭化珪素半導体基板の表面上に延在する絶縁膜4と、を備え、ショットキ電極は炭化珪素半導体基板の表面上においてガードリングに接し、かつ絶縁膜上にも延在し、ガードリングの幅寸法比を10、ショットキ電極がガードリングに接する幅寸法比を1、絶縁膜上に延在するショットキ電極の先端からガードリングの外周端までの離間距離比をXとするとき、離間距離比Xは、3〜9内に設定されている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】低オン抵抗、高耐圧及び高信頼性を達成する。

【解決手段】窒化物半導体装置110は、第1半導体層3、第2半導体層4、第1電極10、第2電極7、第3電極8、第1絶縁膜6及び第2絶縁膜5を備える。第1半導体層3は、窒化物半導体を含む。第2半導体層4は、第1半導体層3上に設けられ、孔部4aを有する。第2半導体層4は、第1半導体層3よりも広い禁制帯幅を有する窒化物半導体を含む。第1電極10は、孔部4a内に設けられる。第1電極10の一方側に第2電極7、他方側に第3電極8が設けられ、それぞれ第2半導体層4と電気的に接続される。第1絶縁膜6は、酸素を含有する膜であって、第1電極10と孔部4aの内壁とのあいだ、及び第1電極10と第2電極7とのあいだに設けられ、第3電極8と離間して設けられる。第2絶縁膜5は、窒素を含有する膜であって、第1電極10と第3電極8とのあいだで第2半導体層4に接して設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

ショットキーバリアダイオード

【課題】ジャンクションバリアショットキー構造をもつダイオードにおいて、ショットキー接合部の逆サージ耐量を改善することが可能なショットキーバリアダイオードを提供する。

【解決手段】ガードリング層15に隣接した第二半導体層161と、この第二半導体層161に隣接する第二半導体層162との間に跨るように、基板11の中心領域Acにおいて第三絶縁層23が形成されている。即ち、第二半導体層161と第二半導体層162との間で、基板11の一面(一方の主面)11aに露呈された第一半導体層13を覆うように第三絶縁層23が形成される。これによって、第三絶縁層23は、第二半導体層161と第二半導体層162との間で基板11の一面11aに露呈された第一半導体層13と、金属層14との間を電気的に絶縁する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキーバリアダイオードの逆リーク電流を低減させる。

【解決手段】禁制帯幅の異なるGaN膜3a、3bとバリア膜4a、4bとを交互に積層して形成したヘテロ接合体5a、5bを有する積層体6と、積層体6の一方の側壁にショットキー接続された第1電極8と、もう一方の側壁に接して形成された第2電極10とを有する半導体装置において、第1電極8とバリア膜4a、4bとの間に酸化膜12を設ける。これにより、バリア膜4a、4bの加工に起因してバリア膜4a、4bに残留する欠陥にを介して逆リーク電流が流れることを防ぐ。

(もっと読む)

半導体整流装置

【課題】少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極とフィールドプレート電極間の容量を低減させた半導体装置およびその製造方法を提供する。

【解決手段】一実施形態によれば、半導体装置10は、N++型の第1半導体層10上にN−型の第1導電型の第2半導体層12が形成されている。フィールドプレート電極14が第2半導体層12に形成されたトレンチの底面側であって、第1絶縁膜13を介してトレンチの下部を埋め込むように形成されている。第2絶縁膜16がトレンチの上部において、フィールドプレート電極14の上面に接するように形成されている。ゲート電極17がトレンチの開口側であって、ゲート絶縁膜15を介するとともに第2絶縁膜16を挟んでトレンチの上部を埋め込むように形成されている。P型のベース層18が第2半導体層12の上部に形成されている。N+型のソース層19がベース層18の上部に形成されている。

(もっと読む)

パワー半導体素子

【課題】窒化物化合物半導体を用いたパワーダイオード、パワーMOSFET等のパワー

半導体素子について、クラックフリーで形成されて従来よりも厚い窒化物化合物半導体層

を使用して耐圧を向上することである。

【解決手段】シリコン基板1上に厚さ10μm以上の凸状に選択成長された窒化物化合物

半導体からなるキャリア移動層3と、キャリア移動層3上に形成された電極4とを有し、

1つのパワー半導体素子は1つのキャリア移動層3から構成されている。

(もっと読む)

半導体装置の製造方法

【課題】携帯電話などのフロントエンドモジュールに使用されているハイパワーアンプは、シリコン系CMOS集積回路をベースとするデバイスであるが、その出力段に多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成したLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。このポリシリコンプラグは、熱処理に起因する固相エピタキシャル成長により収縮し、シリコン基板に歪が発生する。

【解決手段】本願発明は、LDMOSFET等の半導体装置の製造方法において、基板の表面からエピタキシャル層を貫通するホールを形成し、ポリシリコンプラグを埋め込むに際して、ホールの内面に薄膜酸化シリコン膜が存在する状態で、ポリシリコン部材の堆積を行うものである。

(もっと読む)

半導体不揮発性メモリ装置

【課題】占有面積を増加することなくトンネル絶縁膜の劣化を抑制して高い信頼性を持った電気的書き換え可能な半導体不揮発性メモリ装置を得る。

【解決手段】トンネル領域を有する半導体不揮発性メモリにおいて、トンネル領域の周囲部分は掘り下げられており、掘り下げられたドレイン領域には、空乏化電極絶縁膜を介して、トンネル領域の一部を空乏化するための電位を自由に与えることが可能な空乏化電極を配置する。

(もっと読む)

発光素子、発光素子ユニットおよび発光素子パッケージ

【課題】発光効率の向上を図ることができる発光素子、これを含む発光素子ユニットおよび発光素子ユニットを樹脂パッケージで覆った発光素子パッケージを提供すること。

【解決手段】発光素子1では、第1導電型半導体層3上に、発光層4、第2導電型半導体層5、透明電極層6、反射電極層7および絶縁層8が、この順で積層されていて、絶縁層8上には、第1電極層10と第2電極層12とが分離絶縁された状態で積層されている。発光素子1は、平面視において離散して配置されて絶縁層8から連続して反射電極層7、透明電極層6、第2導電型半導体層5および発光層4を貫通し、第1導電型半導体層3に到達する複数の絶縁管層9と、第1電極層10から連続し、絶縁層8および絶縁管層9を通って第1導電型半導体層3に接続された第1コンタクト11と、第2電極層12から連続し、絶縁層8を貫通して反射電極層7に接続された第2コンタクト13とを含む。

(もっと読む)

電力用半導体装置

【課題】オン電圧および損失の低減を可能にする電力用半導体装置を提供する。

【解決手段】pベース層2の表面からn−層1の第1の主面に対して垂直方向で、n−層1内に達する位置まで形成され、その後n−層1の第1の主面に対して水平方向で、片側に所定の長さ延出した底部3dを有したL字形のトレンチゲート21を備え、さらに所定の隣合うL字形のトレンチゲート21の底部21dの延出方向が対向するようにして、それぞれの底部21dの間隔が、n−層1の第1の主面に対して垂直方向に形成されている部分の間隔より狭くなるようにしたことを特徴とする。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

半導体装置

【課題】ドリフト領域が主に窒化ガリウム層で構成された縦型のパワー半導体装置において、電界集中を緩和して高耐圧とすることができる新たな耐圧構造を有する半導体装置を提供すること。

【解決手段】高濃度シリコン基板の上に窒化ガリウムの半導体層を積層し、窒化ガリウム半導体層側の表面には、主電流の流れる活性領域の周囲がノンドープ窒化ガリウム化合物半導体層により方位される構成の半導体装置とする。

(もっと読む)

1 - 20 / 123

[ Back to top ]