Fターム[4M104EE02]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極下 (1,572)

Fターム[4M104EE02]の下位に属するFターム

ゲート絶縁膜 (1,401)

Fターム[4M104EE02]に分類される特許

21 - 40 / 171

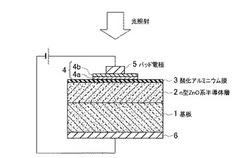

ZnO系半導体素子

【課題】リーク電流をより小さくし、かつ、電気的特性を改善したショットキーバリア型のZnO系半導体素子を提供する。

【解決手段】基板1上にn型ZnO系半導体層2、酸化アルミニウム膜3が順に形成されている。また、酸化アルミニウム膜3上には、金属電極4、パッド電極5が形成される。金属電極4は、Pd層4a上にAu層4bが積層された多層膜構造を有している。金属電極4は、半透明電極として機能する。金属電極4上にはパッド電極5が形成されている。基板1の裏面には金属電極4に対向するように、裏面電極6が形成される。n型ZnO系半導体層2とPd層4aでショットキーバリア構造を構成している。

(もっと読む)

表示装置およびその製造方法

【課題】配線にCuを用いる配線の電気抵抗値とTFTの電気特性値を均一にするアクティブマトリクス型表示装置及びその製造方法を提供する。

【解決手段】基板およびTFTを有する表示装置の製造方法であって、TFTは、電極および電極近接層を有し、電極は、銅および銅以外の添加元素を含み、以下の工程を含む表示装置の製造方法(A)基板の上に電極および電極近接層が形成される工程、(B)電極または電極近接層がオゾン水で洗浄される工程、(C)前記(B)の工程後の熱処理により、電極と電極近接層との界面に、酸素を含む酸化物膜が形成される工程。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

トランジスタデバイスおよび高電子移動度トランジスタ(HEMT)

【課題】デバイス利得、帯域幅、および動作周波数が増加するトランジスタを提供する。

【解決手段】第1のスペーサ層28が、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間の活性領域の表面の少なくとも一部の上にある。ゲート電極24は、ソース電極20とドレイン電極22に向かって延在する一般的にT字型の頂部34を備える。フィールドプレート32は、スペーサ層28の上であって、ゲート頂部34の少なくとも1つの区域のオーバーハングの下にある。第2のスペーサ層30は、ゲート電極24とドレイン電極22との間、およびゲート電極24とソース電極20との間にある第1のスペーサ層28の少なくとも一部の上と、フィールドプレート32の少なくとも一部の上に形成される。少なくとも1つの導電性経路が、フィールドプレート32をソース電極20またはゲート電極24に電気的に接続する。

(もっと読む)

窒化物半導体ダイオード

【課題】 従来と同じチップ面積でありながら従来よりも素子抵抗が低く、順方向電流が大きくとれる窒化物半導体ダイオードを提供する。

【解決手段】 窒化物半導体上のショットキー電極形成領域において、ショットキー電極と窒化物半導体層の表面とが接する境界の長さの合計が、前記ショットキー電極形成領域の外周長よりも長くなるように形成する。また、10倍長いことが望ましい。例えば、ショットキー電極を同心環状とすることで、上記課題を解決することができる。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、パワー半導体素子を提供する。

【解決手段】半導体基材内に第1の伝導型のドリフト領域2と、半導体基材内にドリフト領域2に隣接して配置され半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3の間に配置された蓄積誘電体4と、基材領域8と、基材領域8から分離され蓄積誘電体4に隣接するドレイン領域5と、基材領域8によりドリフト領域2から分離されるソース領域9と、ゲート誘電体16により半導体基材から絶縁されソース領域9からドリフト領域2に到るまで基材領域8に隣接して伸びたゲート電極15と、ドレイン領域5と接したドレイン電極11と、ドレイン領域5と相補的にドープされた半導体領域27とを含み、半導体領域27はドレイン電極11とドリフト領域2の間に配置されドレイン電極11に隣接する。

(もっと読む)

成膜方法及び半導体装置の製造方法

【課題】ポリイミド膜に対して高い密着性を有するコバルト膜を成膜する方法を提供する。

【解決手段】成膜装置100の処理容器1内で、処理容器1内にCOガスを導入しながら、ポリイミド膜81が形成されたウエハWを110℃以上400℃以下の温度で加熱し、ポリイミド膜81を熱処理する。熱処理によって、ポリイミド膜81中の分子が熱分解し、膜密度が減少するとともに、表面粗度が大きくなる。その後、処理容器1内に成膜原料であるCo2(CO)8を導入してCVD法によりポリイミド膜81上にコバルト膜83を堆積させる。

(もっと読む)

半導体装置およびその作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置、およびその作製方法を提供することである。

【解決手段】基板上に下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、第1の加熱処理を行って第2の酸化物半導体膜を形成した後、選択的にエッチングして、第3の酸化物半導体膜を形成し、第1の絶縁膜および第3の酸化物半導体膜上に絶縁膜を形成し、第3の酸化物半導体膜の表面が露出するように絶縁膜の表面を研磨して、少なくとも第3の酸化物半導体膜の側面に接するサイドウォール絶縁膜を形成した後、サイドウォール絶縁膜および第3の酸化物半導体膜上にソース電極およびドレイン電極を形成し、ゲート絶縁膜およびゲート電極を形成する。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

薄膜トランジスタ回路基板及びその製造方法

【課題】製造工程数を大幅に増加することなく高性能な薄膜トランジスタを備えた薄膜トランジスタ回路基板、及び、薄膜トランジスタ回路基板の製造方法を提供する。

【解決手段】 絶縁基板上に配置されたゲート電極と、前記ゲート電極の上に配置されたゲート絶縁膜と、前記ゲート絶縁膜の上に配置されたポリシリコンによって形成され、前記ゲート電極の直上に位置するチャネル領域、前記チャネル領域に隣接するとともに前記チャネル領域よりも高濃度の不純物を含む低濃度不純物領域、及び、前記低濃度不純物領域に隣接するとともに前記低濃度不純物領域よりも高濃度の不純物を含む高濃度不純物領域を含む半導体層と、前記チャネル領域及び前記低濃度不純物領域の上に配置され、前記チャネル領域の直上の膜厚が前記低濃度不純物領域の直上の膜厚よりも厚い保護膜と、前記高濃度不純物領域に電気的に接続された電極と、を備えたことを特徴とする薄膜トランジスタ回路基板。

(もっと読む)

キャップ層および埋込みゲートを有する窒化物ベースのトランジスタを作製する方法

【課題】埋込み部を形成する際のエッチングにより埋込みゲートが損傷をきたし、ゲート領域劣化が生じ得る。

【解決手段】ショットキーコンタクトなどのゲートコンタクトを形成する前にゲート埋込み部のアニーリングを行うことにより、ゲートリークが低減され、かつ/またはトランジスタなどの半導体デバイス内に高品質のゲートコンタクトを提供することができる。アニーリング中に封入層を使用することで、トランジスタのゲート埋込み部内の半導体への損傷がさらに低減される。アニーリングを、例えばデバイスのオーミックコンタクトのアニーリングによって提供することができる。

(もっと読む)

異種材料接合型ダイオード及びその製造方法

【課題】電流電圧特性を維持しつつ、アノード電極6の剥離に対する機械的強度を向上させる。

【解決手段】異種材料接合型ダイオードは、半導体基体1と、半導体基体1の上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主表面に接合された、ドリフト領域2とは異なる種類の材料からなるアノード電極6と、半導体基体1に接続されたカソード電極7とを備える。ドリフト領域2とアノード電極6との接合によりダイオードが形成されている。アノード電極6の主表面のうち、ドリフト領域2に接している側の主表面に、嵌合構造(3、G1)が形成されている。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで高い信頼性を有する、半導体装置およびその製造方法を提供すること。

【解決手段】n型半導体基板の一方の主面に、p型ベース領域とn型エミッタ領域と所要の位置にゲート絶縁膜を介して載置されるゲート電極とからなるMOSゲート構造と該MOSゲート構造を沿面方向に取り巻く耐圧構造部とを有し、他方の主面に1μm以下の浅い逆阻止接合を有するp型コレクタ層を備える半導体装置において、前記コレクタ層の他方の主面上に、バッファ絶縁層を介して被覆されるコレクタ電極が、前記バッファ絶縁層に設けられたコンタクトホールを通して前記コレクタ層と導電接触する半導体装置とする。

(もっと読む)

微細加工構造及び電子デバイス

【課題】プロセス工程の数が従来のリフトオフ方法より少なく、基板との密着性が良好な薄膜パターンの形成が可能な微細加工方法を提供すること。基板との密着性に優れたパターニングされた被加工薄膜を有する微細加工構造を提供すること。移動度が優れた有機トランジスタの作成が可能な微細加工方法及び電子デバイスを提供すること。

【解決手段】基体1上にレジスト膜2を形成する工程、レジスト膜2をパターン露光する工程、現像を行うことなくレジスト膜2上に被加工薄膜4を形成する工程、レジスト膜2の非露光部2bとその上の被加工薄膜4とをリフトオフする工程、を順次行うことを特徴とする。パターン化された被加工薄膜4aと基板1との間に、露光されたレジストパターン2aが介在していることを特徴とする。

(もっと読む)

半導体装置及びその作製方法

【課題】デュアルゲート型トランジスタのゲートと、ソースまたはドレインの間の寄生容量を低減する。

【解決手段】第1の導電層を覆って設けられた第1の絶縁層と、第1の絶縁層上に設けられた第1の半導体層と、第1の半導体層上に、第1の半導体層を露出させて離間して設けられた第2の半導体層と、第2の半導体層上に設けられた不純物半導体層と、不純物半導体層上に、少なくとも一部が接するように設けられた第2の導電層と、第2の導電層上に設けられた第2の絶縁層と、第1の半導体層、第2の半導体層、不純物半導体層、第2の導電層、及び第2の絶縁層を覆って設けられた第3の絶縁層と、少なくとも、第3の絶縁層上に設けられた第3の導電層と、を有し、第3の導電層は、第1の半導体層の第2の半導体層と重畳していない部分と重畳し、且つ第2の導電層の一部とも重畳している構造とする。

(もっと読む)

トレンチゲート型トランジスタの製造方法

【課題】トレンチゲート型トランジスタの製造方法において、ゲート容量の低減、結晶欠陥の発生の抑止、及びゲート耐圧の向上を図る。

【解決手段】N−型半導体層12の表面にトレンチ14を形成し、該表面とトレンチ14内に、熱酸化によりシリコン酸化膜15Aを形成し、これを覆うホトレジスト補強膜16、及びホトレジスト補強膜16を覆うホトレジスト層R2を形成する。そしてホトレジスト層R2及びホトレジスト補強膜16をエッチバックしてトレンチ14内にのみに残す。このホトレジスト層R2及びホトレジスト補強膜16をマスクとして、トレンチ14の側壁の上方のシリコン酸化膜15Aをエッチングして除去する。上記マスクを除去した後、熱酸化により、トレンチ14の側壁の上方にシリコン酸化膜15Aより薄いシリコン酸化膜15Bを形成する。その後、シリコン酸化膜15A,15B上にゲート電極18を形成する。

(もっと読む)

窒化物半導体装置及びその製造方法

【課題】電流コラプスを抑制し、高出力動作可能な窒化物半導体装置を提供する。

【解決手段】ショットキ接触する電極(ゲート電極16)16とオーミック接触する電極(ソース電極17a、ドレイン電極17b)との間のIII−V族窒化物半導体層14表面に、ECRスパッタリング法により珪素膜15を形成する。ショットキ接触する電極16とIII−V族窒化物半導体層14との間に、珪素膜15を形成してもよい。

(もっと読む)

半導体装置およびその製法

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

21 - 40 / 171

[ Back to top ]