Fターム[4M104EE02]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極下 (1,572)

Fターム[4M104EE02]の下位に属するFターム

ゲート絶縁膜 (1,401)

Fターム[4M104EE02]に分類される特許

101 - 120 / 171

半導体装置およびその製造方法

【課題】ソース領域およびドレイン領域をシリサイド化しても、リーク電流を可及的に抑えることを可能にする。

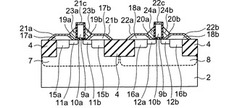

【解決手段】半導体領域7を有するシリコン基板2と、半導体領域に離間して形成されたソース/ドレイン領域11a、15a、11b15bと、ソース領域とドレイン領域との間の半導体領域上に形成された絶縁膜9aと、絶縁膜上に形成されたゲート電極10aと、ゲート電極の側部に形成された側壁絶縁膜13aと、第1ソース/ドレイン領域上に形成され、少なくとも{111}面となる表面を有する単結晶シリコン層17a、17bと、少なくとも単結晶シリコン層の{111}面上に形成され、かつ側壁絶縁膜に接する部分を有し、この部分と単結晶シリコン層との界面が単結晶シリコン層の{111}面であるNiSi層21a、21bと、NiSi層に接する第1のTiN膜23a、23bと、を有する第1のMOSFETと、を備えたことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキーメタルが1種類でありながらも、使用用途に応じた順方向特性、逆方向特性を発現するショットキーバリアダイオードを提供する。

【解決手段】第1導電型の半導体層2を表面に備えた半導体基板1と、半導体層2の表面から層内に延びる第2導電型の半導体領域からなるガードリング6と、ガードリング6で囲まれた半導体層表面に形成された金属層4とでショットキー接合領域を形成した半導体装置であって、ショットキー接合領域は金属層4と半導体層2との間に共晶層が形成された共晶領域7と、共晶領域7で囲まれ、金属層4と半導体層2との間に絶縁膜パターン5が介在し、共晶領域よりも共晶厚さが薄い共晶領域とを含む。

(もっと読む)

高出力ダイヤモンド半導体素子

【課題】高電界でも低リーク電流で高い電圧まで動作する高出力ダイヤモンド半導体素子を提供する。

【解決手段】ショットキー電極をカソードとし、オーミック電極をアノードとし、ショットキー電極、ダイヤモンドp−ドリフト層、ダイヤモンドp+オーミック層、オーミック電極からなる構造の高出力ダイヤモンド半導体素子において、ショットキー電極とダイヤモンドp−ドリフト層の接合面の一部に、誘電層を設け、さらに誘電層の外表面でかつショットキー電極の周囲面に、導電体からなるフィールドプレートを設けることにより、カソード電極付近の電界を緩和する高出力ダイヤモンド半導体素子。

(もっと読む)

電子素子

【課題】温度や周辺の雰囲気に対して、特性が大きく変動する問題を解決する高い仕事関数を持つPt等の水素吸蔵性のある金属からなるショットキー電極として直接、半導体上に作製する構造の素子を提供する。

【解決手段】半導体基板とショットキー電極との間に窒化シリコン(SixNy)薄膜が設けてあることを特徴とする。 また前記窒化シリコン(SixNy)薄膜の厚さが0.5nmから10nmであることを特徴とする。

(もっと読む)

発光装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する発光装置、及び該発光装置を量産高く作製する方法を提案することを課題とする。

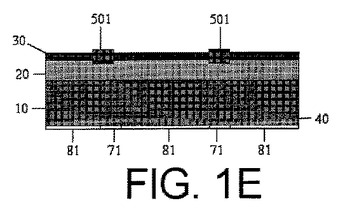

【解決手段】チャネルストップ型の逆スタガ型薄膜トランジスタを有する発光装置において、該チャネルストップ型の逆スタガ型薄膜トランジスタは、ゲート電極と、ゲート電極上にゲート絶縁膜と、ゲート絶縁膜上にチャネル形成領域を含む微結晶半導体膜と、微結晶半導体膜上にバッファ層と、バッファ層上において微結晶半導体膜のチャネル形成領域と重なる領域にチャネル保護層と、チャネル保護層及びバッファ層上にソース領域及びドレイン領域と、ソース領域及びドレイン領域上にソース電極及びドレイン電極を有する。

(もっと読む)

液晶表示装置

【課題】電気特性及び信頼性の高い薄膜トランジスタを有する液晶表示装置、及び該液晶表示装置を量産高く作製する方法を提案することを課題とする。

【解決手段】チャネルストップ型の逆スタガ型薄膜トランジスタを有する液晶表示装置において、該チャネルストップ型の逆スタガ型薄膜トランジスタは、ゲート電極と、ゲート電極上にゲート絶縁膜と、ゲート絶縁膜上にチャネル形成領域を含む微結晶半導体膜と、微結晶半導体膜上にバッファ層と、バッファ層上において微結晶半導体膜のチャネル形成領域と重なる領域にチャネル保護層と、チャネル保護層及びバッファ層上にソース領域及びドレイン領域と、ソース領域及びドレイン領域上にソース電極及びドレイン電極を有する。

(もっと読む)

積層構造体、電子素子、電子素子アレイ及び表示装置

【課題】表面自由エネルギーの高い領域と、表面自由エネルギーの低い領域の境界ラインを明確に切り分けることが可能な積層構造体を、簡易な製造工程を用いて低コストで提供することを目的とする。

【解決手段】第1の膜厚である第1の表面エネルギー部と、所定のエネルギーが付与されて前記第1の表面エネルギー部よりも表面エネルギーが高くなり、かつ、前記第1の表面エネルギー部との境界に沿って溝が形成された第2の膜厚である第2の表面エネルギー部とを有する濡れ性変化層と、前記濡れ性変化層の前記第2の表面エネルギー部に形成された導電層とを有する積層構造体であることを特徴とする。

(もっと読む)

ソース−ドレイン電極、薄膜トランジスタ基板およびその製造方法、並びに表示デバイス

【課題】下部バリアメタル層を省略しても優れたTFT特性を発揮し得、ソース−ドレイン配線をTFTの半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明のソース−ドレイン電極34は、窒素含有層と純AlまたはAl合金の薄膜とからなる。窒素含有層の窒素は、薄膜トランジスタの半導体層33のSiと結合しており、純AlまたはAl合金の薄膜は、窒素含有層を介して薄膜トランジスタの半導体層33と接続している。

(もっと読む)

ジアミン化合物、ポリアミド酸及び可溶性ポリイミド、並びにこれらから得られる濡れ性変化膜及び電極

【課題】エネルギー線を照射し、膜の表面自由エネルギーを変化させ、該変化した部分に銀ナノインクを塗布し、焼成して、電極用ラインを形成する時、少ない照射エネルギーの照射線で膜の表面自由エネルギーを変化させることが可能な有機半導体材料の原料となるポリアミド酸の提供。

【解決手段】1,3−ジアミノ−ベンゼン−5−カルボン酸置換基含有フェノールエステルで、該置換基が、2,3,4−トリアルコキシフェニレンを含有することを特徴とするジアミン化合物と酸二無水物との共重合体であるポリアミド酸。

(もっと読む)

スイッチング素子

【課題】スイッチング素子の動作電圧を低下させる。

【解決手段】スイッチング素子100において、絶縁性基板10と、絶縁性基板10の一面に設けられた第1電極20及び第2電極30と、第1電極20と第2電極30との間に設けられ、第1電極20と第2電極30との間への所定電圧の印加により抵抗のスイッチング現象が生じる間隙を有する電極間間隙部40と、を備え、絶縁性基板10の当該一面に窒素を含有させるよう構成した。

(もっと読む)

電界効果半導体装置

【課題】ノーマリオフのHEMTを得ることが困難であった。

【解決手段】本発明に従うHEMTは、電子走行層4と、この上を覆う電子供給層5と、電子供給層5と、ソース電極6と、ドレイン電極7と、ゲート電極8と、第1及び第2の絶縁膜9,10と、圧電体層11とを有している。第1の絶縁膜9は電子走行層4と電子供給層5とのヘテロ接合面に沿って生じる2DEG層13を分断する働きを有する。圧電体層11はゲート電極8の電圧に応答して第1の絶縁膜9の応力を打ち消す働きを有する。これにより、ノーマリオフ特性を有し且つオン抵抗が小さいHEMTを得ることができる。

(もっと読む)

半導体装置の製造方法

【課題】バリアメタルが薄い場合でもAl配線のモフォロジ及びエレクトロマイグレーションを改善することができる半導体装置の製造方法を得る。

【解決手段】まず、半導体基板11上にSiO2層間膜13(酸化膜)を形成する。次に、SiO2層間膜13上にTi膜18を形成する。次に、Ti膜18上にTiN膜32を形成する。次に、TiN膜32上にAl配線33を形成する。ここで、Ti膜18を形成する工程において、圧力が0.3Pa以下の雰囲気中で物理気相成長法を用いる。これにより、Ti膜18とSiO2層間膜13との間にTiO2膜31が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極と各ソース/ドレイン電極間に有限の間隔が存在するため、寄生抵抗が発生する。

【解決手段】バリア層4の内で第1及び第2高濃度n型不純物領域6A,6B間の領域4A全体の表面上に、AlGaOから成る絶縁膜8が全面的に形成されている。更に、絶縁膜8の表面上に、ゲート電極9が全面的に形成されている。本構造によって、ゲート電極9と第1及び第2高濃度n型不純物領域6A,6Bないしは第1及び第2ソース/ドレイン電極7A,7Bとが直接に接触することはない。

(もっと読む)

有機薄膜トランジスタ

【課題】 有機物を利用して薄膜トランジスタを製造しようとする場合、有機半導体薄膜のキャリア移動度が小さく、実用的な動作速度を有する有機薄膜トランジスタは得られなかった。この課題を解決するために縦型有機薄膜トランジスタが検討され、高速動作が期待されているが、十分な電流オンオフ比が得られないという課題がある。

【解決手段】 本発明の有機薄膜トランジスタは、基板上に第1の電極(ソース又はドレイン)、第1の有機半導体層、第3の電極(ゲート)、第2の有機半導体層、第2の電極(ドレイン又はソース)の順に積層した構造を有する。第3の電極の膜厚を80nm以上の厚膜とする。第3の電極の膜厚を厚くすることで、大きなオンオフ比を有する有機薄膜トランジスタが得られる。

(もっと読む)

液晶表示装置及びその製造方法

【課題】 本発明は、半導体層あるいは画素電極との密着性が高い酸化被膜を形成して、配線材料等の酸化を防止できると共に、導電率が高いソース電極あるいはドレイン電極を備えた液晶表示装置及びその製造方法を提供することにある。

【解決手段】 本発明では、液晶表示装置を構成するTFT基板上のTFT電極において、ソース電極あるいはドレイン電極が、銅を主体とした層と、該銅を主体とした層を被覆する酸化物からなることを特徴とする。さらに、本発明は、前記TFT電極において、半導体層あるいは画素電極と、前記ソース電極あるいはドレイン電極とが、オーミック接合していることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】シリサイド層上に抵抗値の上昇が抑制されたコンタクトを備え、高い信頼性を有する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板10と、半導体基板10内に形成された活性領域50と、活性領域50の上面に形成されたシリサイド層45と、半導体基板10およびシリサイド層45の上に形成された第1の層間絶縁膜15と、シリサイド層45上に形成され、第1の層間絶縁膜15を貫通するコンタクトプラグ60とを備えている。コンタクトプラグ1個当たりのシリサイド層45の面積は、コンタクトプラグの面積以上、且つ、100μm2以下である。

(もっと読む)

銀及びニッケル、もしくは、銀及びニッケル合金からなる厚膜導電体形成、及びそれから作られる太陽電池

本発明は、太陽電池及び太陽電池コンタクトの処方及び製造方法を開示するものである。概して、本発明は、焼成に先立って、ニッケルと銀とを含む金属部からなる混合物から作られる太陽電池コンタクトを提供するものである。

(もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】セルコンタクトのアクティブ領域に対する位置合わせにずれが生じた場合でも、コンタクト抵抗を増大させない半導体装置及びその製造方法を提供する。

【解決手段】半導体基板20、半導体基板に設けられた素子分離膜21、層間絶縁膜60及び導電プラグ62を備えて構成される。半導体基板は、一方の主表面20a側に、第1の方向及び第2の方向に行列配列されたメモリセルを有している。導電プラグは、層間絶縁膜内に形成されていて、メモリセルと層間絶縁膜上に形成される配線74とを電気的に接続する。各メモリセルは、ゲート電極34と、一対の不純物拡散領域40を備えている。不純物拡散領域は、主表面側に金属シリサイド膜46を有している。導電プラグは、素子分離膜上と金属シリサイド膜上とに形成されている。金属シリサイド膜は、第1部分47と、第2部分48を備えていて、第1部分の厚みが第2部分の厚みよりも大きい。

(もっと読む)

積層構造体及びその製造方法

【課題】本発明は、少ない紫外線照射量で表面自由エネルギーを変化させることが可能な積層構造体及び該積層構造体の製造方法を提供することを目的とする。また、本発明は、該積層構造体を有する電子素子、該電子素子を複数有する電子素子アレイ及び該電子素子アレイを有する表示装置を提供することを目的とする。

【解決手段】積層構造体は、基板11上に、エネルギーを付与することにより臨界表面張力が変化する材料を含有する濡れ性変化層12と、濡れ性変化層12にパターン形成された導電層13を有し、臨界表面張力が変化する材料は、主鎖と側鎖を有し、側鎖は、エネルギーを吸収すると結合が開裂する部位を2個以上有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】研磨工程などを削減するとともに素子分離領域の上に微細なゲートスペースパターンを有する。

【解決手段】半導体装置は、半導体基板100と、素子分離絶縁膜101と、第1および第2電極107a,107bと、ゲート絶縁膜パターン104と、側壁絶縁膜108とを備えている。素子分離絶縁膜101は半導体基板100の上に設けられており、第1および第2電極107a,107bはゲート絶縁膜パターン104を挟むようにして素子分離絶縁膜101の上に設けられている。側壁絶縁膜108は、第1および第2電極107a,107bの側面のうちゲート絶縁膜パターン104に接している部分以外の部分に設けられている。

(もっと読む)

101 - 120 / 171

[ Back to top ]