Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

261 - 280 / 992

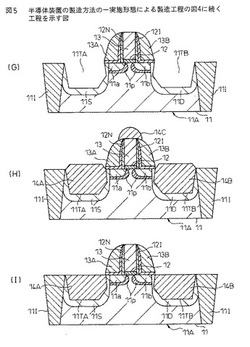

半導体装置の製造方法

【課題】消費電力の少ない半導体装置の製造方法を提供する。

【解決手段】ゲート電極13の多結晶シリコン領域と、ゲート電極13下のチャネル領域11Cを挟んで配置された一対の単結晶シリコン領域11S,11Dとが形成されたシリコン基板11に対して、単結晶シリコン領域11S,11D上に単結晶のSiGe混晶層領域14A,14Bを成長させ、且つ多結晶シリコン領域13上に多結晶のSiGe混晶層領域14Cを成長させる工程と、Clを含むガスを用いて、一対の単結晶シリコン領域11S,11D上に成長したSiGe混晶層領域14A,14Bの表面側の一部を取り除くと共に、多結晶シリコン領域13上に成長したSiGe混晶層領域14Cを取り除く工程と、一対の単結晶シリコン領域上のSiGe混晶層領域14A,14B上に単結晶のシリコン層15A,15Bを成長させる工程と、シリコン層15A,15Bをシリサイド化する工程と、を有する。

(もっと読む)

半導体装置とその製造方法

【課題】本発明は、高性能でかつ閾値電圧の低い半導体装置とその製造方法を提供することを目的とする。

【解決手段】基板に形成され、NMOSトランジスタが形成されるNMOS形成領域とPMOSトランジスタが形成されるPMOS形成領域とを絶縁分離する素子分離領域と、該基板上に形成されたHigh−k材料からなるNMOSおよびPMOSのゲート絶縁膜と、該NMOSのゲート絶縁膜上に形成されたNMOSゲート電極と、該PMOSゲート絶縁膜上に形成された第1ニッケルシリサイド層と、該第1ニッケルシリサイド層上に形成され、該第1ニッケルシリサイド層よりも厚くかつ該第1ニッケルシリサイド層よりニッケル密度が大きい第2ニッケルシリサイド層と、を有するPMOSゲート電極と、該NMOSゲート電極および該PMOSゲート電極の側壁に形成されたサイドウォールスペーサとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】前記従来のエアーギャップを有するMISトランジスタ及びその製造方法では、ゲート電極の周囲にエアーギャップを設けるため、ゲート電極に近接して応力絶縁膜を形成することができない。

【解決手段】半導体装置は、ゲート絶縁膜13と、ゲート電極14と、ソースドレイン領域19と、コンタクトプラグ22と、応力絶縁膜23とを備えている。ゲート電極14の側方のうちゲート電極14とコンタクトプラグ22との間に位置する領域のみに空洞24が形成されており、応力絶縁膜23は半導体基板10上にゲート電極14を覆うように形成されており、半導体基板10におけるゲート電極14の直下に位置するチャネル領域に対して応力を生じさせる。

(もっと読む)

半導体装置及びその製造方法

【課題】容易に製造することができ、トランジスタの性能を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2及びゲート電極3が形成されている。半導体基板1の表面の、平面視でゲート電極3を挟む位置に2個の不純物拡散層4が形成されている。2個の不純物拡散層4の表面に、ゲート絶縁膜2と半導体基板1との界面より低くなった掘り込み部6が設けられている。更に、半導体基板1のゲート絶縁膜2下の領域(チャネル)に応力を付加する応力付加膜が、少なくとも掘り込み部6内に位置している。

(もっと読む)

ゲート・スタック、ゲート・スペーサ及びコンタクト・ビアを用いる垂直型金属−絶縁体−金属(MIM)キャパシタ

【課題】 向上した製造可能性を有する金属−絶縁体−金属キャパシタ、及びその製造方法を提供する。

【解決手段】 垂直型金属−絶縁体−金属キャパシタを含む半導体構造体、及び垂直型金属−絶縁体−金属キャパシタを含む半導体構造体の製造方法がそれぞれ、半導体基板の上に配置された分離領域の上に配置され形成されたダミー金属酸化物半導体電界効果トランジスタからの構造コンポーネントを用いる。ダミー金属酸化物電界効果トランジスタは、分離領域を含む半導体基板の上に配置された金属酸化物半導体電界効果トランジスタと同時に形成することができる。金属−絶縁体−金属キャパシタは、キャパシタ・プレートとしてゲートを用い、ゲート誘電体として均一な厚さのゲート・スペーサを用い、別のキャパシタ・プレートとしてコンタクト・ビアを用いる。容量の増大のために、均一な厚さのゲート・スペーサは、導体層を含むことができる。容量の増大のために、単一のコンタクト・ビアを用いる鏡像となる金属−絶縁体−金属キャパシタ構造体を用いることもできる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】層間絶縁膜を表面研磨する工程を経て形成される半導体装置の信頼性を向上させる。

【解決手段】シリコン基板1の主面s1上に、高耐圧ゲート絶縁膜IG1および高耐圧ゲート電極EG1からなる高耐圧ゲートG1を形成した後、サリサイドブロック膜SAB、層間絶縁膜ILを順に形成し、その層間絶縁膜ILをCMPにより研磨する。サリサイドブロック膜SABは、下層から順に酸化シリコンを主体とする絶縁膜である保護酸化膜t1と、窒化シリコンを主体とする絶縁膜である保護窒化膜t2とによって形成する。また、層間絶縁膜ILの研磨は、高耐圧ゲートG1上面のサリサイドブロック膜SABに達するまで研磨する。

(もっと読む)

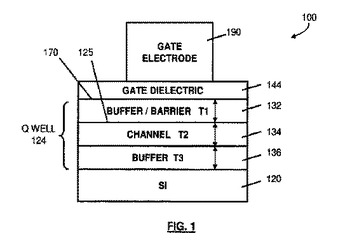

金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインにより発生される一軸性歪みを有する量子井戸MOSFETチャネル

開示の実施形態は、MOSチャネル領域に一軸性歪みを与える金属ソース/ドレイン及びコンフォーマル再成長ソース/ドレインを備えた、歪みトランジスタ量子井戸(QW)チャネル領域を含む。チャネル層の除去された部分が、チャネル材料の格子間隔とは異なる格子間隔を有するジャンクション材料で充填されることで、量子井戸の頂部バリア層及び底部バッファ層によってチャネル層に発生される二軸性歪みに加えて、一軸性歪みがチャネルに発生される。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する複数の電気素子要素と、複数の電気素子要素を覆う、シリコンを含まない下層保護絶縁膜と、下層保護絶縁膜の上に配置され、シリコンを含む上層保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、複数の電気素子要素の少なくとも一つは、シリサイド化される金属を含有でき、下層保護絶縁膜は、電気素子要素に含有される金属と上層保護絶縁膜に含有されるシリコンとの接触を阻害できる。下層保護絶縁膜は、比誘電率が10以上の高誘電体層を有してよい。上層保護絶縁膜は、シリコンおよび窒素を含有することができる。

(もっと読む)

半導体装置

【課題】ゲート電極とのコンタクトのためのコンタクトホールの形成時に、ゲート電極が深く掘り下げられることを防止できる半導体装置を提供すること。

【解決手段】ゲートトレンチ6を有するエピタキシャル層3に、ボディ領域5、ドレイン領域4、ソース領域9およびボディコンタクト領域10を形成する。ゲートトレンチ6には、ゲート電極8を埋設する。エピタキシャル層3には、層間絶縁膜11を積層する。ゲート電極8と層間絶縁膜11との間には、エピタキシャル層3とはエッチングレートの異なる材料からなるエッチングストッパ層14を介在させる。そして、エッチングにより、ゲート電極8およびボディコンタクト領域10それぞれとのコンタクトのための、ゲートコンタクトホール13およびソースコンタクトホール15を同時に形成する。ゲートコンタクトホール13は、平面視でエッチングストッパ層14と重なるように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の小型化が進んでも半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】本発明の技術的思想は、積層形成される窒化シリコン膜SN1〜SN3のそれぞれの膜厚を一定値ではなく、トータルの総膜厚を一定に保ちながら、上層の窒化シリコン膜SN3から下層の窒化シリコン膜SN1にしたがって膜厚を薄くするように構成している点にある。これにより、歪シリコン技術を実効あらしめる窒化シリコン膜SN1〜SN3の引張応力を確保しながら、特に、最上層の窒化シリコン膜SN3の埋め込み特性を改善できる。

(もっと読む)

半導体装置及びその製造方法

【課題】 オン抵抗の小さいDMOSトランジスタを含む半導体装置の製造方法を提供することを目的とする。

【解決手段】

CMOSトランジスタ1は、ゲート電極9と、N+型のソース領域3と、N+型のドレイン領域4を備える。DMOSトランジスタ21は、ゲート電極29と、N+型のソース領域23と、N―型のドリフト領域30と、ドレイン領域24と、シリサイド層32aを備える。ゲート電極9のソース領域3側とドレイン領域4側の側部にはサイドウォール8Bが設けられ、ゲート電極29のソース領域23側とドレイン領域24側の側部にはサイドウォール28C、28Dが設けられている。ドレイン領域24側のサイドウォール28Cは、ソース領域23側のサイドウォール28D、及びサイドウォール2Bよりもチャネル方向に沿う厚さが厚い。さらに、シリサイド層32aがゲート電極9上面のドレイン領域24側端まで形成されている。

(もっと読む)

半導体装置

【課題】トランジスタの集積化を妨げることなく、トランジスタの駆動力を向上させる半導体装置を提供する。

【解決手段】所定の結晶からなる半導体基板上にゲート絶縁膜を介して形成されたゲート電極と、ゲート幅方向に凸部を有して前記半導体基板内に形成され、前記所定の結晶とは異なる格子定数を有するエピタキシャル結晶が埋め込まれたソース・ドレイン領域と、を具備するトランジスタと、前記凸部以外の前記ソース・ドレイン領域に接続されたコンタクトプラグと、を備えた半導体装置を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な高い動作電圧を有するN型およびP型トランジスタ、ならびに適切な低い動作電圧を有するN型およびP型トランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置1は、半導体基板2上に形成されたHVNトランジスタ10と、HVPトランジスタ20と、LVNトランジスタ30と、LVPトランジスタ40と、抵抗素子50を有する。LVNトランジスタ30は、絶縁体層31a、La2O3層31bおよび高誘電率絶縁体層31cからなるゲート絶縁膜31と、金属層32aおよび半導体層32bからなるゲート電極32を有する。LVPトランジスタ40は、絶縁体層41a、Al2O3層41bおよび高誘電率絶縁体層41cからなるゲート絶縁膜41と、金属層42aおよび半導体層42bからなるゲート電極41を有する。抵抗素子50は、絶縁体材料からなる第1の層51と、半導体材料からなる第2の層52を有する。

(もっと読む)

半導体装置の製造方法

【課題】デュアルメタルゲート構造を有する半導体装置において、ゲート電極除去する工程において、ゲート絶縁膜に与える損傷を抑える。

【解決手段】 第1のトランジスタと第2のトランジスタとを備える半導体装置において、第1のトランジスタは、第1の仕事関数を有する第1の材料からなる第1のゲート電極と、第1のゲート絶縁膜とを含む。また、第2のトランジスタは、第2の仕事関数を有する第2の材料からなる第2のゲート電極と、第2のゲート絶縁膜とを含む。ここで、第1のゲート絶縁膜は、高誘電率膜と、第1の高誘電率膜上に形成された第1の絶縁膜とを含むものとする。第2のゲート絶縁膜においては、高誘電率膜上部に形成した第1の絶縁膜を、第1のゲート電極を除去した後に除去する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】金属シリサイド層と窒化シリコン膜の界面に自然酸化膜が残存していると、窒化シリコン膜の成膜後の種々の加熱工程(例えば種々の絶縁膜や導体膜の成膜工程のように半導体基板の加熱を伴う工程)において、金属シリサイド層表面にある自然酸化膜の酸素に起因して、金属シリサイド層が部分的に異常成長してしまう。

【解決手段】本願発明においては、集積回路を構成する電界効果トランジスタのソース・ドレイン上のニッケル・シリサイド等の金属シリサイド膜の上面に対して、不活性ガスを主要な成分とするガス雰囲気中において、実質的にノン・バイアス(低バイアスを含む)のプラズマ処理を施した後、コンタクト・プロセスのエッチング・ストップ膜となる窒化シリコン膜を成膜することにより、金属シリサイド膜の不所望な削れを生じることなく、金属シリサイド膜の上面の自然酸化膜を除去することができる。

を図ることができる。

(もっと読む)

半導体装置の製造方法

【課題】ダミーゲートを高選択的に除去することのできる半導体装置の製造方法を提供すること。

【解決手段】半導体装置1の製造工程において、シリコン基板2上にゲート絶縁膜8を形成し、このゲート絶縁膜8上にダミーゲート32を形成する。ダミーゲート32の側面には、サイドウォール10を形成する。サイドウォール10の形成後、ダミーゲート32を被覆する第1絶縁層17を形成し、第1絶縁層17の表面がダミーゲート32の表面と面一となるように加工する。第1絶縁層17の加工後、ダミーゲート32に、ダミーゲート32とサイドウォール10とのエッチング選択比を確保可能なエッチング液を供給することにより、ダミーゲート32をウェットエッチングする。そして、ダミーゲート32のエッチングにより現れるゲート絶縁膜8上に、金属材料からなるゲート電極9を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線層間の正常な電気的導通が取れている半導体装置を提供することを課題とする。

【解決手段】基板上又は基板の表面層に少なくとも2層の配線層を備え、前記2層の配線層の内、下層配線層がシリコンからなる際に、前記下層配線層と上層配線層間に炭化珪素層を備えたことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御でき、短チャネル効果を効果的に抑制できる半導体装置を提供する。

【解決手段】シリコン基板1と接してショットキー接合を形成するソース領域10,ドレイン領域11と、上記シリコン基板1とソース領域10との境界が露出する部分およびシリコン基板1とドレイン領域11との境界が露出する部分を被覆するように設けられた絶縁層を備える。上記絶縁層は、シリコン基板1とソース領域10との境界およびシリコン基板1とドレイン領域11との境界を跨ぐように、シリコン基板1とソース領域10に接すると共にシリコン基板1とドレイン領域11に接する固定電荷を含む領域8を有する。上記固定電荷は、熱平衡状態において荷電している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】導電層が基板の内部深くにまで達することを回避して、浅いソース・ドレイン領域を形成することを可能とし、微細化に適した半導体装置及びその製造方法を得る。

【解決手段】シリコン基板1の上面内にエクステンション5を形成した後、シリコン酸化膜30を全面に堆積し、シリコン酸化膜30上にシリコン窒化膜31を、シリコン窒化膜31上にシリコン酸化膜32をそれぞれ堆積し、シリコン酸化膜32、シリコン窒化膜31及びシリコン酸化膜30をこの順にエッチングしてサイドウォール36を形成する。不純物領域13を形成し、シリコン酸化膜に対して選択性を有する条件下でシリコン成長を行うことにより、シリコン成長層15,16,37を形成する。コバルト17を全面に堆積した後、熱処理を行うことにより、コバルトシリサイドを形成する。その後、未反応のコバルト17を除去する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の絶縁膜の上に形成される金属配線または金属電極の接着力を向上させる。

【解決手段】窒化タングステン6bをタングステン6cの側面にまで設けて、タングステン6cと窒化タングステン6bとが接触している面積を増やす。ゲート絶縁膜2上に、ゲート絶縁膜2との接着力が強いポリシリコンサイドウォール5を配置する。タングステン6cの側面にある窒化タングステン6bにはポリシリコンサイドウォール5を密着させる。

(もっと読む)

261 - 280 / 992

[ Back to top ]