Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

861 - 880 / 992

トレンチゲート電界効果トランジスタおよびその形成方法

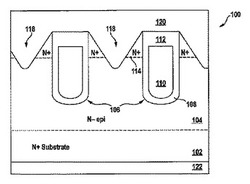

一体的に統合されたトレンチFETおよびショットキーダイオードを含む構造体であって、半導体領域内に伸張するゲートトレンチと、ゲートトレンチの各側面に位置し、実質的に三角形状のソース領域と、隣接するトレンチ間における半導体領域内部に伸長するコンタクト開口と、コンタクト開口を満たし、各ソース領域の傾斜した側壁部の少なくとも一部に沿ってソース領域と電気的に接触し、且つコンタクト開口の底部に沿って半導体領域と電気的に接触し、且つ半導体領域とショットキーコンタクトを形成する導電体層と、を含む。 (もっと読む)

半導体装置およびその製造方法

【課題】 活性領域とタングステンプラグとの接触面積の低下を防止する。

【解決手段】 シリコン基板1にSTI2を形成し、活性領域3を区画形成する。ゲート電極4aを形成した後に、活性領域3のコンタクトホール5を形成する領域の表面を上に凸の滑らかな表面となるようにRIE加工する。層間絶縁膜10にコンタクトホール5を形成する際に、パターンずれが発生してもコンタクトプラグ13との接触面積の低下を防止できる。設計ルールの縮小化に伴う不具合を回避することができる。

(もっと読む)

半導体装置の製造方法

【課題】 接合特性、抵抗、コンタクト特性のばらつきを低減・防止する。

【解決手段】 図1に示す半導体装置1は、シリコンで構成されたシリコン基板2、シリコン基板2上に形成されたp型ウェル領域3、p型ウェル領域3上に形成されたn+型ソース領域4、n+型ドレイン領域5、p型ウェル領域3上のn+型ソース領域4とn+型ドレイン領域5とに対向して設けられたゲート電極6、ゲート電極6をn+型ソース領域4とn+型ドレイン領域5との接触から絶縁するゲート絶縁膜7およびゲート電極6の側部に設けられたサイドウォール8を有している。ゲート電極6は、CMP法によりポリシリコンが露出しない位置まで、ポリシリコン上に形成されたマスク層の一部を除去し、その後、マスク層を除去してポリシリコン層を露出し、ポリシリコン層をシリサイド化して形成したシリサイドで構成されている。

(もっと読む)

半導体装置とその製造方法

【課題】本発明は、CMOSトランジスタにおいて、nチャネル型トランジスタとpチャネル型トランジスタの両方に同一のメタルゲート材料を用いて好ましい、半導体装置と製造工程の効率が向上する製造方法を提供する。

【解決手段】nチャネル型トランジスタは、不純物領域と、ゲート酸化膜、ゲート電極からなるゲート電極側壁絶縁膜を有していない第1のゲート積層体と、半導体基板の表面および前記第1のゲート積層体を覆う引張応力を有する第1のシリコン窒化膜とを備え、前記半導体基板の第2の領域に配置されてなるpチャネル型トランジスタは、不純物領域と、ゲート酸化膜、ゲート電極およびゲート電極側壁絶縁膜からなる第2のゲート積層体と、半導体基板の表面および前記第2のゲート積層体を覆う圧縮応力を有する第2のシリコン窒化膜とを備える。

(もっと読む)

半導体装置の製造方法

【課題】LDD構造を有し、ソース/ドレイン領域に自己整合的に金属シリサイド層が形成されているMOSFETの製造方法において、ソース/ドレイン領域上のシリサイド層がLDD層と接触しないようにする。

【解決手段】ソース/ドレイン領域6形成後のシリコン基板1に保護膜用の酸化シリコン膜7を形成した後、チタン膜8を形成する部分の上から酸化シリコン膜7を除去して保護膜72を形成する。この保護膜72を、ゲート電極3の上と、サイドウォール51の上と、ソース/ドレイン領域6のLDD層4側の部分61の上にも形成する。次に、この保護膜72を介して、シリコン基板1上にチタン膜8を形成した後、所定の熱処理を行って、シリコン基板1とチタン膜8を反応させて、ソース/ドレイン領域6上にシリサイド層9を形成する。

(もっと読む)

非対称性誘電領域を備える半導体装置の形成方法及びその半導体装置の構造

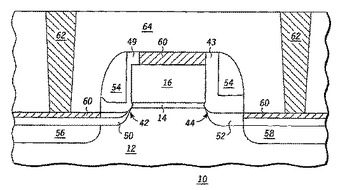

半導体基板(12)を形成するステップ、半導体基板の上方に第一側面及び第二側面を備えるゲート電極(16)を形成するステップ、及びゲート電極の下方にゲート誘電体を形成するステップを含む半導体装置(10)の形成方法。ゲート誘電体は、ゲート電極の下方でゲート電極の第一側面に隣接した第一領域(42)と、ゲート電極の下方でゲート電極の第二側面に隣接した第二領域(44)と、ゲート電極の下方で第一領域及び第二領域間にある第三領域(14)とを備えている。第一領域は、第二領域よりも薄く、第三領域は、第一領域よりも薄く、更に第二領域よりも薄い。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置の素子分離領域等における浅い溝に、ボイドが発生しないように絶縁膜を埋め込む方法を含む半導体装置の製造法方法を提供する。

【解決手段】 溝部の途中段階まで第1の埋込絶縁膜15を形成した後、オーバーハング部を除去し、続いて第2の埋込絶縁膜を溝部へ埋め込む。

(もっと読む)

半導体装置およびその製造方法

【課題】 近年の、半導体素子の微細化に伴い、NBTI寿命が劣化することを防止することを目的とする。

【解決手段】 少なくともライナー膜または第2の側壁絶縁膜として、Si−H結合が1×1021cm-3以下のシリコン窒化膜を用いることでp型MOSFETのNBTI寿命を1×109秒に改善でき、半導体集積回路装置の寿命を確保できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ゲート電極を全て合金化(フルシリサイド化)させる一方で、ソース・ドレイン領域においては合金化反応を抑制することができ、接合リークの発生を抑制することができる半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜2を介してゲート電極を形成した後、ゲート電極の側壁にサイドウォール絶縁膜4を形成する。ゲート電極およびサイドウォール絶縁膜4をマスクとしたイオン注入により、ソース・ドレイン領域6を形成する。その後、ゲート電極を被覆するように半導体基板1上に高融点金属膜8を堆積させ、アニール処理を行う。本発明では、アニール処理において、ゲート電極材料のバンドギャップよりも大きいエネルギーをもつ電磁波を照射する。これにより、フルシリサイド化したゲート電極3aが形成され、ソース・ドレイン領域6中には浅いシリサイド層7aが形成される。

(もっと読む)

半導体装置

【課題】短チャネル効果の抑制を課題とする。

【解決手段】不純物イオンが注入されたP型ソース/ドレイン領域を有する電界効果型トランジスタと、不純物イオンが注入されたN型ソース/ドレイン領域を有する電界効果型トランジスタからなるCMOS半導体装置において、前記P型ソース/ドレイン領域の接合深さは前記N型ソース/ドレイン領域の接合深さに対して、等しいか、或は浅いことを特徴とする半導体装置により上記課題を解決する。

(もっと読む)

半導体装置およびその製造方法

【課題】エピタキシャル成長層によりエクステンション層およびソース・ドレイン層が形成された半導体装置において、合金層と半導体基板間に生じる接合リークを防止して、信頼性を向上させた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板1には、活性領域を区画する素子分離絶縁膜2が形成されており、活性領域における半導体基板1上にゲート絶縁膜4を介してゲート電極5が形成されている。ゲート電極5の両側における半導体基板1上には、エピタキシャル成長層により形成された2つのエクステンション層6と、2つのソース・ドレイン層8が積層されている。ソース・ドレイン層8における素子分離絶縁膜2側の端部には、当該端部における合金層の形成を防止する保護層9が形成されている。保護層9から露出したソース・ドレイン層8には、合金層10が形成されている。

(もっと読む)

MIS型トランジスタおよびその製造方法

【課題】S/D拡散層抵抗の低減とゲート寄生容量の低減とを同時に実現することのできるMIS型トランジスタ及びその製造方法の提供。

【解決手段】MIS型トランジスタは、半導体基板と、この基板上に形成されたソース・ドレイン領域と、このソース・ドレイン領域間のチャネル領域の上方に設けられたゲート電極と、を備える。このMIS型トランジスタにおいて、前記チャネル形成面を挟んで設けられた前記ソース・ドレイン領域の上面が、前記チャネル形成面よりも嵩上げされてゲート電極側に位置し、かつ、前記ソース・ドレイン領域の上面は、嵩上げされて前記ゲート電極側に位置するレベルの実質的な平坦面と、この平坦面のレベルから前記チャネル形成面のレベルまで傾斜する傾斜面と、を備えると共に、前記チャネル形成面の上側に設けられたゲート絶縁膜により囲まれるゲート電極の形状が、段部を介して下側が先細りとなった断面T字の形状となっている。

(もっと読む)

半導体装置の製造方法

【課題】 ゲート絶縁膜へのダメージを抑制してゲートリーク電流を低減させ、且つp型ポリシリコンに近い仕事関数のゲート電極を有する半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1上にゲート絶縁膜3を形成し、ゲート絶縁膜3上に450℃以下の温度でCVD法によりTiN膜4を形成し、このTiN膜4をエッチングしてゲート電極5を形成する。

(もっと読む)

半導体装置の製造方法

【課題】2以上のゲートパターン間に形成されるコンタクトホールのオープンマージン及びギャップフィルマージンを確保するのに適した半導体装置の製造方法を提供する。

【解決手段】基板上に、2個以上のゲートパターンを形成するステップと、該基板上にゲートスペーサ用の第1の絶縁膜を形成するステップと、該第1の絶縁膜上に前記ゲートパターンが埋め込まれるように第2の絶縁膜を形成するステップと、前記第2の絶縁膜を選択的に除去して、前記第1の絶縁膜を露出させるコンタクトホールを形成するステップと、該コンタクトホールにより露出した前記第1の絶縁膜上にゲートスペーサ用の第3の絶縁膜を形成するステップと、前記基板が露出するようにするために、前記コンタクトホールの底に形成された前記第1の絶縁膜及び第3の絶縁膜を選択的に除去するステップとを含む半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】 層間絶縁膜の埋め込み性を向上させ、短絡防止のマージンを向上させる。

【解決手段】 上部がゲート上部絶縁膜で覆われたゲートを半導体基板上に形成し、全面に絶縁膜を形成した後に全面エッチバックを行うことでゲート上部絶縁膜及びゲートの側面に上部の形状が垂直方向から5°〜30°傾斜したテーパー形状のサイドウォールを形成し、全面に第1の層間絶縁膜を形成し、第1の層間絶縁膜のみをCMPにより平坦化し、ゲート上部絶縁膜よりも第1の層間絶縁膜の方が研磨選択比が高い条件でCMPを行って、第1の層間絶縁膜、ゲート上部絶縁膜及びサイドウォールを平坦化し、全面に第2の層間絶縁膜を形成し、フォトリソグラフィにより第1の層間絶縁膜及び第2の層間絶縁膜にゲート側の側壁が平坦となったサイドウォールの上部にかかるようにコンタクトホールを形成し、コンタクトホールを導電物質で埋め込んでコンタクトパッドを形成する。

(もっと読む)

半導体装置

【課題】 ショットキー型電界効果トランジスターに於いて、殊にソース領域近傍のチャネル領域に対するゲート電極の制御性を高めて、素子の電流駆動能力の向上を図る。

【解決手段】 ゲート絶縁膜を異なる誘電率を持つ膜の積層とすることで、誘電率の高い材料のみで形成した場合と比べてゲート絶縁膜の幾何学的な意味の厚さを薄く形成することを可能とし、ゲート電極から出た電気力線のゲート絶縁膜の側面から外への漏れに起因する、殊にソース領域近傍のチャネル領域の電位に対するゲート電極の制御性の低下を抑制する事が可能となる。また、誘電率の高い材料よりなるゲート側壁絶縁膜12を設ける事に依り、異なる誘電率を持つ物質の界面に於ける電気力線の屈折に依って、ゲート電極から出た電気力線をソース領域近傍のチャネル領域に集める事が可能となり、ソース領域とチャネル領域との間に形成されるショットキー障壁を薄くし、その抵抗を低減する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 電流のリークが生じにくい半導体装置を提供する。

【解決手段】 半導体基板1に形成された素子分離膜2と、高電圧駆動トランジスタのゲート酸化膜3aと、ゲート酸化膜3a上に形成されたゲート電極4aと、半導体基板1に形成され、低電圧駆動トランジスタのソース及びドレインとして機能する不純物領域7bと、半導体基板1上、素子分離膜2a,2b上及びゲート電極4a上それぞれに形成された第1のエッチングストッパー膜9と、第1のエッチングストッパー膜9上に形成され、不純物領域7bの上方に位置する第2のエッチングストッパー膜10と、第1のエッチングストッパー膜9上、及び第2のエッチングストッパー膜10上に形成された絶縁膜11と、絶縁膜11に形成され、不純物領域7b上に位置する接続孔11bとを具備する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 電流のリークが生じにくい半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、第1のトランジスタのチャネル領域を他の領域から分離する素子分離膜2aと、ゲート酸化膜3a及びゲート電極4と、素子分離膜2a上に形成されたポリシリコンパターン4cと、ポリシリコンパターン4c上、及び素子分離膜2a上に形成されたマスク膜9と、第2のトランジスタのソース及びドレインとして機能する不純物領域7bと、ゲート電極4a上及び不純物領域7b上それぞれに形成された金属シリサイド膜8a,8bと、素子分離膜2a、及び不純物領域7b上に位置する金属シリサイド膜8b上それぞれに形成されたエッチングストッパー膜10と、エッチングストッパー膜10に設けられ、素子分離膜2a上のマスク膜9上に設けられた開口部10aとを具備する。

(もっと読む)

ステップゲートを有する半導体素子及びその製造方法

【課題】セルのしきい値電圧の低下を防止できる半導体素子及びその製造方法を提供すること。

【解決手段】第1活性領域101A及び第1活性領域101Aに比べて高い位置に形成された第2活性領域102とを有する半導体基板21を準備するステップと、第1活性領域101A及び第2活性領域102間の境界領域を面取処理するステップと、面取処理された境界領域を含む基板全面にゲート絶縁膜31を形成するステップと、境界地域上のゲート絶縁膜31上に、第1活性領域101Aの一部から第2活性領域102の一部までまたがりステップ構造を有するゲートパターン200を形成するステップと、ゲートパターン200の両側壁にゲートスペーサ34、35を形成するステップと、第1活性領域101Aに第1セル接合部36Aを、第2活性領域102に第2セル接合部36Bを形成するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 緻密な膜厚制御を必要とすることなくジャンクション・リークを防ぐことができ、より実効的なMIS型電界効果トランジスタの低抵抗化に必要な厚さの金属シリサイド層が形成可能な半導体装置及びその製造方法を提供する。

【解決手段】 P型のSi基板11表面に、チャネル領域12を隔ててN型のソース/ドレイン拡散層15が形成されている。ソース/ドレイン拡散層15は低濃度エクステンション領域151を有する。ゲート電極14は、ポリシリコン層141上に第1シリサイド層142を有する。ゲート電極14及び絶縁膜スペーサ16を隔ててソース/ドレイン拡散層15上に第2シリサイド層152が設けられている。この第2シリサイド層152は、第1シリサイド層142とは異なる金属を用いて形成されている。

(もっと読む)

861 - 880 / 992

[ Back to top ]