Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

941 - 960 / 992

半導体装置および半導体装置の製造方法

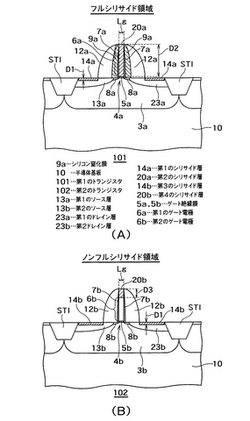

【課題】 ソースおよびドレインにおける接合リークを抑制し、膜厚が互いに異なるシリサイドをゲート電極に含むトランジスタを同一半導体基板上に備えた半導体装置を提供する。

【解決手段】 半導体基板10の表面に形成された第1のソース層13aおよび第1のドレイン層23aとこの上に形成された第1のシリサイド層14aと、半導体基板表面に設けられた第1のゲート絶縁膜5a上に形成され、第2のシリサイド層20aを有する第1のゲート電極6aと、前記第1のゲート電極の側壁に設けられたシリコン窒化膜9aとを含む第1のトランジスタ101および、半導体基板10の表面に形成された第2のソース層13bおよび第2のドレイン層23bと、この上に形成され、第1のシリサイド層14aと膜厚が同じである第3のシリサイド層14bと、半導体基板表面に設けられたゲート絶縁膜5b上に形成され、第2のシリサイド層20aと膜厚が異なる第4のシリサイド層20bを有する第2のゲート電極6bとを含む第2のトランジスタ102、を備えている。

(もっと読む)

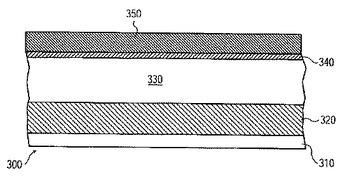

リンが注入されたポリシリコンのシート抵抗の減少

リンが注入されたポリシリコンのシート抵抗を減少するプロセスが存在する。一実施の形態において、MOSトランジスタ構造(300)が存在する。構造は、ゲート領域、ドレイン領域及びソース領域を有する。ゲート領域のシート抵抗を減少する方法(220)は、予め決定された温度で真性アモルファスシリコンをゲート領域に堆積する(221)。アモルファス化の種が、真性アモルファスシリコンに注入される(222)。その後、リンの種が、MOSトランジスタ構造のゲート領域に注入される(223)。この実施の形態の特徴は、アモルファス化の種としてのAr+の使用を含む。  (もっと読む)

(もっと読む)

半導体デバイス及び同デバイスを形成する方法

MOSFETの製造において、MOSFETに関する幾つかの構造的目的を果たす再酸化段階を提供することが知られている。しかしながら、より小型の集積回路用のドライブを収容するMOSFETのゲート絶縁層用の高誘電率材料を提供する必要性によって、ゲート絶縁層と基板との間のSiO2界面層の過剰な成長をもたらした。SiO2層の過剰成長は、MOSFET内の漏れ電流の増大につながる酸化膜換算膜厚(EOT)を生じる。更に電極としてポリシリコンを金属と置き換えることは、処理中の酸素曝露を妨げる。結果として、本発明は、MOSFETのゲート電極(32)の少なくとも側壁(34)を覆う酸素障壁層(40)の堆積段階と再酸化段階とを置き換え又は先行して行うことで、誘電界面及び金属ゲート電極への酸素拡散のための障壁を形成し、EOTの増大を防ぎ金属ゲート電極の完全性を保持する。 (もっと読む)

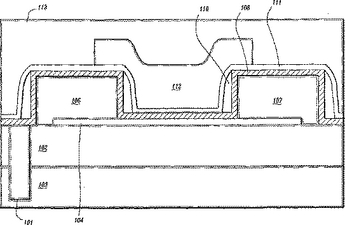

半導体装置

【課題】 高誘電率膜により構成されたゲート絶縁膜と、P型不純物を含む多結晶シリコン膜により構成されたゲート電極とを含む半導体装置において、閾値電圧の増加を抑制する。

【解決手段】 P型MOSFET120は、半導体基板(Nウェル102b)と、半導体基板上に形成され、Hf、Zr、およびランタノイド元素のいずれかからなる群から選択される第一の元素と、ならびにNとを含むシリケート化合物を含む高誘電率膜108により構成されたゲート絶縁膜と、ゲート絶縁膜上に形成されるとともに、P型不純物を含む多結晶シリコン膜114により構成されたゲート電極と、ゲート絶縁膜とゲート電極との間に形成され、第一の元素と多結晶シリコン膜114との反応を阻止するとともに、比誘電率が8以上の阻止酸化膜110と、を含む。

(もっと読む)

ヘテロバイポーラ・トランジスタ(HBT)およびその製作方法(BiCMOS技術におけるコレクタ形成方法)

【課題】デバイスのサブコレクタ上のシャロー・トレンチ分離領域の下部に埋め込み高融点金属シリサイド層を設けることによりコレクタ抵抗Rcを低下させる、高速BiCMOS用途用のヘテロバイポーラ・トランジスタ(HBT)、および、このようなHBTを製作する方法を提供する。

【解決手段】本発明のHBTは、少なくともサブコレクタ(13)を含む基板(12)と、サブコレクタ上に位置する埋め込み高融点金属シリサイド層(28)と、埋め込み高融点金属シリサイド層の表面上に位置するシャロー・トレンチ分離領域(30)とを含む。また、本発明の方法は、デバイスのサブコレクタ上のシャロー・トレンチ分離領域の下部に埋め込み高融点金属シリサイド層を形成するステップを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明の目的は、ゲート長が高精度に制御され、かつ、ショートチャネル効果を抑制する半導体装置及びその製造方法を提供することである。

【解決手段】 第1のゲート電極膜17aと、第1のゲート電極膜17aのゲート長よりも長いゲート長を具備する第2のゲート電極膜20とを有する2段型ゲート電極20aを形成することにより、ゲート長が高精度に制御される。また、エクステンション領域21は第2のゲート電極膜20をマスクにして不純物導入がされるため、ショートチャネル効果を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 半導体装置の性能を向上させる。

【解決手段】 LDMOSFETのゲート電極30およびn+型ソース領域53上にサリサイド工程により金属シリサイド膜64を形成し、n-型オフセットドレイン領域33、n型オフセットドレイン領域51およびn+型ドレイン領域52上にはこの金属シリサイド膜を形成しない。ゲート電極30のドレイン側の側壁上には、絶縁膜を介して、シリコン膜からなるサイドウォールスペーサが形成され、このサイドウォールスペーサによりフィールドプレート電極44が形成される。フィールドプレート電極44はゲート電極30上に延在しておらず、サリサイド工程ではゲート電極30の上面の全面に金属シリサイド膜64が形成される。

(もっと読む)

半導体装置の構造およびその製造方法

【課題】 自己整合的にコンタクトホールを形成する半導体装置において、ゲート電極の側面に形成する絶縁膜の耐圧を大きくする。

【解決手段】 シリコン基板1上に金属膜を含むゲート電極Aを形成し、その側面に側壁シリコン窒化膜13aを形成する。さらにその側面に第一シリコン酸化膜14、第一シリコン窒化膜15、第二シリコン酸化膜16、第二シリコン窒化膜17aを積層したサイドウォールBを形成する。このような構造とすることにより、隣接するサイドウォールBの間に自己整合的にコンタクトホールを形成するとき、金属膜の酸化を防止して、ゲート電極Aの抵抗上昇を抑えることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイド技術を用いた半導体装置では、低コストかつ短工程でMIS型トランジスタのゲート電極と拡散領域との短絡を防ぐことが困難であった。

【解決手段】ゲート部とソース・ドレイン部とを有する半導体素子であって、ゲート部は、ゲート電極の側部にサイドウォールを備える。サイドウォールの上端部がゲート電極の上端部よりも高く形成しており、サイドウォールのゲート電極に接する面は、ゲート電極上面に対してほぼ直角である。サリサイド技術を用いても、ゲート電極上に形成されたチタンと、サイドウォールおよびソース・ドレイン部上に形成されたチタンとは離間した状態となっており、シリサイドによるゲート電極とその他の部分との短絡を防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】従来の2層構造のサイドウォールスペーサとLDD構造のソース・ドレイン領域とサリサイド構造とを有するMIS型半導体装置は、ソース・ドレイン領域にてリーク電流が発生するという課題があった。

【解決手段】第1サイドウォールスペーサと第2サイドウォールスペーサとを備えるサイドウォール構造のゲート電極と、第1拡散領域と第2拡散領域とを備えるLDD構造のソース・ドレイン領域と、サリサイド構造とを有するMIS型半導体装置であって、MIS型半導体装置は半導体基板に形成する素子領域を設け、素子領域の周囲を囲むようにフィールド酸化膜を有し、素子領域とフィールド酸化膜との境界領域に、第1拡散領域もしくは第2拡散領域と接続する第3拡散領域を有する。

(もっと読む)

多層ゲートスタック

プラズマによりパターン形成された窒化層を形成するために窒化層をエッチングすることからなる半導体構造体を製造する方法。窒化層は半導体の基板上にあり、フォトレジスト層は窒化層上にあり、プラズマは、少なくとも圧力10ミリトルでCF4及びCHF3のガス混合物から形成される。 (もっと読む)

半導体装置の製造方法

【課題】 Coシリサイド電極をもつ半導体装置の製造プロセスを簡素化し、Coシリサイド膜及びキャップ層の厚さを制御可能とすることでコンタクトホールに於けるアスペクト比の減少を実現し、Coシリサイド膜を形成する際の未反応Coからなる残渣の発生を皆無にすると共にCo酸化物を容易に除去して清浄を維持できるようにする。

【解決手段】 Si基板21上にCo及びSiを同時に蒸着するか或いはCoを堆積した後に加熱するCoシリサイド膜22の形成に於いて、カルボキシル基をもつガス状物質に曝露しながら、或いは、曝露した後に加熱し、表面に在るCo及びSiのうち、Coはカルボン酸塩として揮発させると共にSiは酸化してSiO2 からなる保護膜であるキャップ層25とする工程が含まれてなることを基本とする。

(もっと読む)

エレベイテッドサリサイドソース/ドレイン領域の形成方法、および半導体素子

【課題】エレベイテッドサリサイドソース/ドレイン領域の形成方法及びT型素子分離膜を有する半導体素子を提供する。

る。

【解決手段】本発明に係るエレベイテッドサリサイドソース/ドレイン領域80の形成方法には、拡幅トレンチ領域の深さを調節することによってソース/ドレイン領域80を形成するためのイオン注入段階で、前記T型素子分離膜71のヘッド部を構成し、前記狭幅トレンチ領域の上端部から左右側に延長された前記拡幅トレンチ領域の下部81にも導電型不純物を注入可能にする。

(もっと読む)

半導体装置およびその製造方法

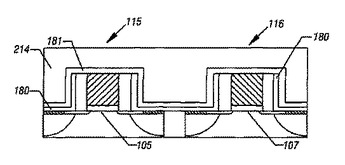

【課題】半導体装装置を構成する半導体素子の微細化にともない、電極の間の距離も縮小され、電極の間に設ける層間絶縁膜の中にボイドが発生していた。このボイドは、半導体装置の信頼性を悪化するため、大きな問題であった。

【解決手段】半導体基板11の上部に絶縁膜21を設け、この上部に第1の導電性材料14と第2の導電性材料15とを積層して設ける。絶縁性を有する被服層16を第1の導電性材料14の側端部に設け、これらにより電極10を構成する。第2の導電性材料15の側端部は、第1の導電性材料14の側端部より内側に設け、第1の導電性材料14と第2の導電性材料15とが接する面積は、第1の導電性材料14の上面部の面積よりも小さい。

(もっと読む)

半導体装置とその製造方法

【課題】 プラズマ処理によりシリコン表面に形成される、SiCを含む変質層を、シリコン表面の侵食を最小限に抑止しながら除去する。

【解決手段】 前記変質層を、酸素ラジカルに、前記半導体表面のSi原子に結合してSi原子と酸素原子との間の二重結合の形成を阻害するような元素の活性種を添加して改質し、形成された改質層をウェットエッチングにより除去する。

(もっと読む)

自己整合型ナノチューブ電界効果トランジスタおよびこれを製造する方法

【課題】 自己整合型カーボン・ナノチューブ電界効果トランジスタ半導体デバイスを提供する。

【解決手段】 基板(102)上に堆積したカーボン・ナノチューブ(104)と、カーボン・ナノチューブ(104)の第1の端部および第2の端部にそれぞれ形成されたソースおよびドレイン(106〜107)と、誘電体膜(111)によってカーボン・ナノチューブから分離された、実質的にカーボン・ナノチューブ(104)の一部の上に形成されたゲート(112)とを備える。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】 側壁絶縁膜の形成などのプロセスにおけるチャージングによるダメージを抑制する。

【解決手段】 不揮発性半導体記憶装置のメモリセルアレイ形成領域に複数のワード線を形成するための第1の導電膜と半導体装置形成領域に第2の導電膜を形成する。次に、第1のドライエッチングによってメモリセルアレイ形成領域におけるワード線が互いに離間して配置されるように、第1の導電膜に開口部を形成した後、開口部にワード線の側壁絶縁膜を形成する。次に、ウェットエッチングによって側壁絶縁膜におけるワード線の端部近傍領域に存在する部分を除去する。次に、第2のドライエッチングによって第1の導電膜におけるワード線の端部近傍領域に存在する部分を除去する。第1の導電膜における開口部の形成は、第1の導電膜における開口部形成後の残存部分が、メモリセルアレイ形成領域の外部領域に位置する半導体基板中の活性領域上にて、活性領域と電気的に接続されるように形成された第2の導電膜と接続されるように行なわれる。

(もっと読む)

高kゲート誘電体および金属ゲート電極を有する半導体デバイス

ゲート誘電体と、アルミナイドを含む金属ゲート電極とを有する半導体デバイスについて示した。  (もっと読む)

(もっと読む)

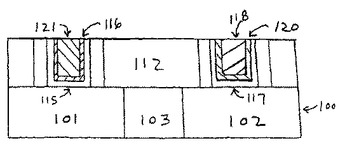

半導体基板内の分離溝に隣接するコンタクト用開口の形成方法

【課題】フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法を提供する。

【解決手段】トレンチ形成・埋め込み法によって半導体基板の中にフィールド分離マスを形成し、該フィールド分離マスに隣接した基板上に基板マスキング層を形成する工程であって、前記フィールド分離マスの上面はエッチングストップキャップによって覆われ、その側壁は前記マスキング層によって覆われる工程と、前記分離マス側壁の少なくとも一部を露出するために、分離マスから分けて前記基板マスキング層を除去する工程と、露出した分離マス側壁上にエッチングストップカバーを形成する工程と、前記分離マス及び該分離マスに隣接する基板領域上に絶縁層を形成する工程と、前記分離マスエッチングストップキャップ及びカバーに対して選択的に、前記分離マスに隣接する前記絶縁層を貫通するコンタクト用開口をエッチング開口する工程とからなる、フィールド分離マスに隣接する領域にコンタクト用開口を形成する半導体製造方法。

(もっと読む)

置換金属ゲート形成のための半導体構造の平坦化

窒化物および充填層を含む犠牲ゲート構造は、金属ゲート電極と置換される。金属ゲート電極は、充填層で被覆された窒化物層で再度被覆される。窒化物および充填層の置換によって、歪みが再導入され、エッチング停止層が提供される。  (もっと読む)

(もっと読む)

941 - 960 / 992

[ Back to top ]