Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

981 - 992 / 992

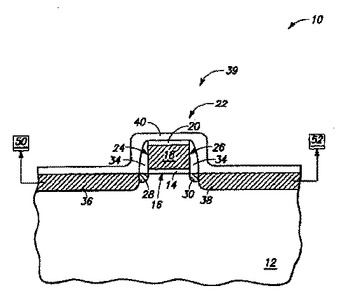

半導体装置及び半導体装置の製造方法

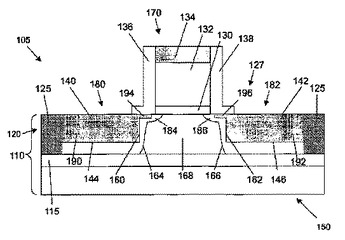

本発明は、半導体装置(105)及びこの装置の製造方法に関する。本発明の好ましい実施例は、シリコン半導体基板(110)、酸化膜層(115)及び活性層(120)を含む半導体装置(105)である。活性層では、絶縁領域(125)及び活性領域(127)が形成された。活性領域(127)は、ソース(180)、ドレイン(182)及び基体(168)を含む。ソース(180)及びドレイン(182)は、ソースエクステンション(184)及びドレインエクステンション(186)も含む。活性層(120)はゲート(170)を有する。ゲート(170)の両側にL字型側壁スペーサが位置する。ソース(180)及びドレイン(182)は、シリサイド領域(190、192)も含む。これらの領域の特徴は、側壁(136、138)の下に位置されたエクステンション(194、196)を有することである。これらのエクステンション(194、196)は、半導体装置(105)の性能を著しく改善するように、ソース(194)及びドレイン(196)の直列抵抗を大きく低減する。  (もっと読む)

(もっと読む)

集積回路技術における低応力の側壁スペーサ

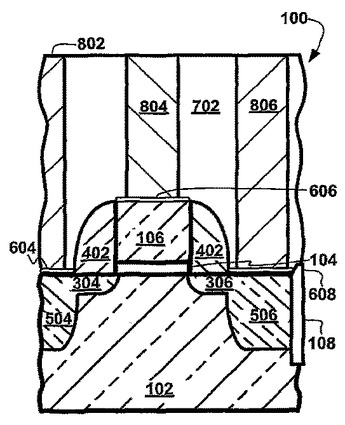

半導体基板(102)に集積回路の形成方法(900)を提供する。半導体基板(102)上にゲート絶縁膜(104)が形成され、このゲート絶縁膜(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(304)(306)が形成される。低出力プラズマ化学気相成長法プロセスを使用して、ゲート(106)の周りに側壁スペーサ(402)を形成する。ソース/ドレイン接合部(304)(306)およびゲート(106)に、シリサイド(604)(606)(608)を形成し、半導体基板(102)上に層間絶縁層(702)をたい積する。その後、層間絶縁層(702)中にシリサイド(604)(606)(608)へのコンタクト(802)(804)(806)が形成される。  (もっと読む)

(もっと読む)

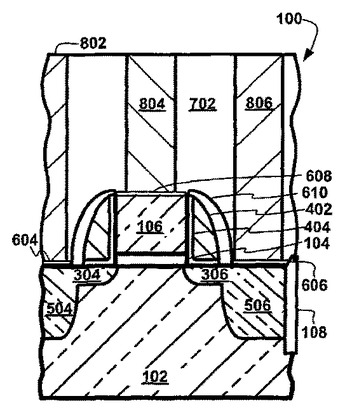

シリサイド成長ドーパント雪かき効果の使用による、デバイス中に階段接合の形成

トランジスタ(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に絶縁層(702)をたい積する。その後、絶縁層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

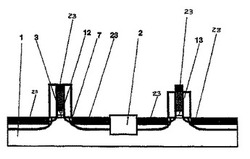

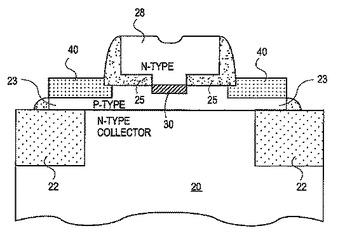

改善された外部ベース領域を備えたバイポーラ接合形トランジスタ及びその製造方法

バイポーラトランジスタ及びその製造方法に関する。第1のエピタキシャル層(23)上への第2の、より高濃度にドープされたエピタキシャル層の成長によって、外部ベース領域(40)が形成される。第2のエピタキシャル層は上にあるポリシリコンエミッタ台座(28)の下まで広がり、かつ、この台座(28)から絶縁される。  (もっと読む)

(もっと読む)

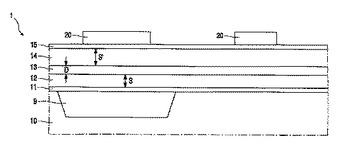

粒状半導体材料を有する応力半導体構造

【課題】 チャネル移動度の向上を利用して性能を改善した半導体デバイス構造およびその製造方法を提供する。

【解決手段】 半導体デバイス構造を製造する方法であって、基板を設けるステップと、基板上に電極を設けるステップと、電極内に開口を有するくぼみを形成するステップと、くぼみ内に細粒半導体材料を配置するステップと、開口を覆ってくぼみ内に細粒半導体材料を閉じこめるステップと、上述のステップの結果として得られる構造をアニーリングするステップと、

を含む。

(もっと読む)

部分的シリサイド化シリコン層を有する集積回路

この集積回路(1)は、シリサイド化部(122)及び非シリサイド化部(123)を有する第1のシリコン層(120)を有する抵抗素子などの電気的装置(2)と、例えばキャパシタ、電界効果トランジスタ又は不揮発性メモリゲート堆積部などの他の電気的装置(3)とを有する。他の電気的装置(3)は、誘電層厚さ(D)を有する誘電層(130)を有する。電気的装置(2)の非シリサイド化部(123)は、誘電層厚さ(D)を有する他の誘電層(131)により被覆され、シリサイド化部(122)は、他の誘電層(131)により被覆されない。このような集積回路(1)は、リソグラフィ工程数の少ない本発明による方法によって形成可能となる。

(もっと読む)

(もっと読む)

酸化物−窒化物スタックゲート誘電体

半導体構造体を作製する方法は、基板上に酸化物層を形成する段階と、酸化物層上に窒化ケイ素層を形成する段階と、各層をNO中でアニールする段階と、各層をアンモニア中でアニールする段階とを含む。酸化物層と窒化ケイ素層とを併せた等価酸化膜厚は、最大25オングストロームである。 (もっと読む)

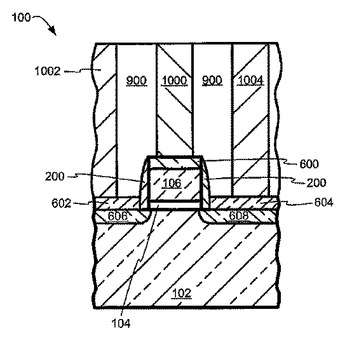

集積回路技術におけるシリサイド化スペーサ

集積回路(100)の形成方法(900)およびその構造を提供する。半導体基板(102)上にゲート誘電体(104)が形成され、ゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)に浅いソース/ドレイン接合部(304)(306)が形成される。ゲート(106)の周りに側壁スペーサ(402)を形成する。この側壁スペーサ(402)を使用して、半導体基板(102)中に深いソース/ドレイン接合部(504)(506)が形成される。浅いソース/ドレイン接合部および深いソース/ドレイン接合部(504)(506)を形成した後、側壁スペーサ(402)上にシリサイドスペーサ(610)を形成する。シリサイドスペーサ(610)に隣接する深いソース/ドレイン接合部(504)(506)上にシリサイド(604)(606)を形成し、半導体基板(102)上に誘電体層(702)をたい積する。その後、誘電体層(702)においてシリサイド(604)(606)へのコンタクトを形成する。  (もっと読む)

(もっと読む)

ジュウテリウム置換窒化珪素含有材料の作製方法

少なくとも1種のジュウテリウム置換窒素化合物と水素同位体を含まない1または2以上の珪素含有化合物からのジュウテリウム置換窒化珪素含有材料作製方法を提供する。適するジュウテリウム置換窒素化合物として例えばNH2D、NHD2及びND3を用い、適する珪素含有化合物として例えばSiCl4及びSi2Cl6を用いる。本発明に従って得られるジュウテリウム置換窒化珪素含有材料は例えばトランジスタ装置中へ組み入れることができ、これにより得られたトランジスタ装置をDRAMセル中に用い、さらに得られたDRAMセルを電子システム中に用いることができる。

(もっと読む)

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

表示装置及びその作製方法

【課題】 配線抵抗による電圧降下の影響や画素への信号の書き込み不良や階調不良などを防止し、より高画質のEL表示装置や液晶表示装置を代表とする表示装置を提供することを課題とする。

【解決手段】 本発明はEL表示装置や液晶表示装置を代表とする表示装置に用いられる電極や配線として、Cuを有する配線を設ける。また、該配線のCuを主成分とする導電膜は、マスクを用いたスパッタ法により形成する。このような構成により、電圧降下や信号のなまりを低減することができる。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

981 - 992 / 992

[ Back to top ]