Fターム[4M104EE09]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 絶縁膜の適用位置 (3,412) | 電極側部 (992)

Fターム[4M104EE09]に分類される特許

141 - 160 / 992

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

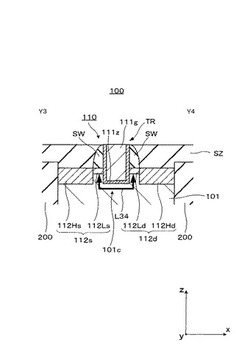

半導体装置、および、その製造方法

【課題】半導体素子の特性を向上させると共に、半導体素子の微細化を容易に実現する。

【解決手段】半導体素子101にてゲート電極111gが設けられる部分の表面を凹凸面に形成する。ここでは、凹凸面のうち凸部CVでは、一対のソース・ドレイン領域112s,112dの表面と同一の面を覆うようにゲート絶縁膜111zを形成し、そのゲート絶縁膜111zの上面にゲート電極111gを設ける。これに対して、凹部TRでは、一対のソース・ドレイン領域112s,112dの表面から内部へ向けて設けられた溝Mの面を覆うようにゲート絶縁膜111zを形成し、その溝Mの内部を埋め込むようにゲート電極111gを設ける。

(もっと読む)

半導体素子、半導体装置及びそれらの作製方法

【課題】チャネル長Lが短く微細化が可能な、酸化物半導体を用いたトップゲート型の半導体素子を提供することを課題とする。また、該半導体素子の作製方法を提供することを課題とする。

【解決手段】絶縁表面上に酸化物半導体層と、酸化物半導体層上にソース電極層及びドレイン電極層と、酸化物半導体層、前記ソース電極層、及び前記ドレイン電極層上にゲート絶縁層と、ゲート絶縁層上にゲート電極層とを有し、ソース電極層及びドレイン電極層は側壁を有し、側壁は前記酸化物半導体層の上面と接する半導体素子である。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を提供し得る半導体装置の製造方法を提供することにある。

【解決手段】第2の応力膜44に対する第2の絶縁膜48の選択比が第1の値である第1の条件でエッチングを行うことにより、第1のコンタクトホール60eを少なくとも第2の応力膜の途中まで開口し、第2のコンタクトホールを少なくとも第2の絶縁膜の途中まで開口するエッチング工程と、第2の応力膜に対する第2の絶縁膜の選択比が第1の値より大きい第2の値である第2の条件でエッチングを行うことにより、第1のコンタクトホールにより第2の応力膜44を貫き、第2のコンタクトホールにより第2の絶縁膜及び第1の絶縁膜40を貫くエッチング工程と、更なるエッチングを行い、第1のコンタクトホールをゲート配線20まで到達させ、第2のコンタクトホールをトランジスタのソース/ドレインまで到達させる第3のエッチング工程とを有している。

(もっと読む)

半導体装置

【課題】良質な半導体装置を提供することを目的としている。

【解決手段】素子分離領域間の凸部108を含むシリコン基板106と、凸部108上の絶縁部112と、絶縁部112上のシリコンフィン114と、上面が凸部108の上面よりも低く位置する素子分離領域内の素子分離層116と、シリコンフィン114に設けられたソース/ドレイン領域と、ソース/ドレイン領域104のシリコンフィン114の側面から外側に突き出た横方向エピ成長シリコン部118と、ゲート電極領域102内のゲート絶縁層122を介してシリコンフィン114上に設けられるゲート電極124と、ゲート電極124の側面に隣接する第1のスペーサ128と、ソース/ドレイン領域104内の凸部108の側面を覆う第2のスペーサ130とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】短チャネル効果の発生を抑制できる半導体装置及びその製造方法の提供。

【解決手段】本発明の半導体装置は、半導体基板1の活性領域上にゲート絶縁膜5aを介して形成されたゲート電極105と、ゲート電極105側面を覆う第1絶縁膜サイドウォール5bと、ゲート電極105を挟んで形成されたソース領域108S及びドレイン領域108Dにおいて、側面が第1絶縁膜サイドウォール5bに接して半導体基板1上面に形成されたシリコン層109と、第1絶縁膜サイドウォール5bを介してゲート電極105側面と対向し、底面がシリコン層109上面に接して形成された第2絶縁膜サイドウォール5dと、シリコン層109内下層部に設けられたLDD不純物層109aと、シリコン層109内上層部に設けられた高濃度不純物層109bと、LDD不純物層109aの下方、半導体基板1の表面側に形成されたポケット不純物層108aとを具備する。

(もっと読む)

電界効果トランジスタの金属ゲート構造

【課題】電界効果トランジスタの電気抵抗の小さい金属ゲート構造を提供する。

【解決手段】本発明は、集積回路製造に関するものであって、特に、低抵抗の金属ゲート電極を有する電界効果トランジスタに関するものである。電界効果トランジスタのゲート電極の例は、凹部326aを有し、かつ、第一抵抗を有する第一金属材料からなる下側部分326と、突起328aを有し、かつ、第二抵抗を有する第二金属材料からなる上側部分328とからなり、突起が凹部に延伸し、第二抵抗は第一抵抗より小さい材料で形成される。

(もっと読む)

シリコン層の形成方法、半導体装置の製造方法

【課題】シリコン層表面の溶解を防止しつつ、エピタキシャル成長により形成された凝集性異物を除去する。清浄な表面を有し、膜厚が均一なシリコン層を形成する。

【解決手段】シリコン基板上にエピタキシャル成長によりシリコン層を形成した後に、シリコン層の表面を酸化する。このシリコン層の表面を洗浄して、エピタキシャル成長時にシリコン層の表面に発生した異物を除去する。

(もっと読む)

半導体装置およびその作製方法

【課題】良好な特性を備えた、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびドレイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、ゲート絶縁層上のゲート電極と、を有し、ソース電極およびドレイン電極は、その側面が酸化された酸化領域を有する半導体装置である。なお、ソース電極およびドレイン電極の酸化領域は、300MHz以上300GHz以下の高周波電力、および、酸素とアルゴンの混合ガスを用いたプラズマ処理により形成されたものであることが望ましい。

(もっと読む)

半導体装置およびその作製方法

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】半導体材料を含む基板に設けられたチャネル形成領域と、不純物領域と、第1のゲート絶縁層と、第1のゲート電極と、第1のソース電極および第1のドレイン電極と、を有する第1のトランジスタと、半導体材料を含む基板上の酸化物半導体層と、第2のソース電極および第2のドレイン電極と、第2のゲート絶縁層と、第2のゲート電極と、を有する第2のトランジスタと、を有し、第2のソース電極および第2のドレイン電極は、その側面が酸化された酸化領域を有し、第1のゲート電極、第1のソース電極、または第1のドレイン電極のいずれかは、第2のゲート電極、第2のソース電極、または第2のドレイン電極のいずれかと電気的に接続されている半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】配線として用いられる金属シリサイド層の断線の発生を抑えつつ、微細化を可能にする半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板のタップ領域40、トランジスタ領域36、及びシリサイド配線領域38に形成された活性領域と、シリサイド配線領域38上からトランジスタ領域36上に亘って形成されたゲート電極21と、活性領域上に設けられた金属シリサイド層44aとを備えている。シリサイド配線領域38の少なくとも一部上におけるゲート電極21と金属シリサイド層44aとの距離は、トランジスタ領域36上におけるゲート電極と金属シリサイド層44aとの距離よりも小さい。

(もっと読む)

MOS型半導体装置

【課題】所望の位置に所望の厚さのゲート酸化膜を有する、高性能かつ長寿命のMOS型半導体を提供すること。

【解決手段】半導体基板と、該半導体基板上にゲート酸化膜を介して形成されたゲート電極とを含み、該ゲート酸化膜の両端部に接するように該半導体基板上にそれぞれ設けられた、該半導体基板の導電型とは異なる導電型の不純物を含む2つの不純物活性領域をそれぞれソース電極及びドレイン電極とする、MOS型半導体装置であって、該ゲート酸化膜を介して形成されたゲート電極は、それぞれが該半導体基板とゲート酸化膜を介して形成された構造を有する複数の領域からなり、各領域の該ゲート酸化膜の厚さが少なくとも2種類の異なる厚さで構成され、該各領域は互いに接合されている、ことを特徴とするMOS型半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】pチャネルトランジスタ及びnチャネルトランジスタの閾値電圧を共に低減できるCMISトランジスタを有する半導体装置を提供する。

【解決手段】pチャネルトランジスタは、半導体基板100における第1の領域上に形成された第1のゲート構造150Aと、第1のゲート構造150Aの側壁上に形成された第1のスペーサ構造とを有する。nチャネルトランジスタは、半導体基板100における第2の領域上に形成された第2のゲート構造150Bと、第2のゲート構造150Bの側壁上に形成された第2のスペーサ構造とを有する。第1のスペーサ構造における第1のゲート構造150Aの側壁との接触部分の含有酸素濃度は、第2のスペーサ構造における第2のゲート構造150Bの側壁との接触部分の含有酸素濃度よりも高い。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】微細化が進んだトランジスタにおいて、他の問題を生じさせずに抵抗を低減する。

【解決手段】シリサイド層9は、ソース・ドレイン領域8の表層及びソース・ドレイン拡張領域6に形成されている。シリサイド層9は、半導体基板1に垂直かつゲート幅方向に対して平行な断面でみたときに、ソース・ドレイン領域8の中央部からチャネル領域に近づくにつれて半導体基板1の内側(図中下側)に近づいており、かつチャネル領域側の端部がソース・ドレイン拡張領域6に延在している。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置、半導体チップ及び半導体装置の製造方法

【課題】製造工程中にピラー径の変動が小さいピラー型MOSトランジスタを備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板対して垂直に立設する第1のピラー及び第2のピラーの側面にゲート絶縁膜を介して形成されたゲート電極と、第1のピラーの先端部及び基端周囲領域に形成された上部拡散層及び下部拡散層と、を備え、第2のピラーのゲート電極と隣接する第1のピラーのゲート電極とは接続されており、第1のピラーのゲート電極には第2のピラーのゲート電極を介して電位が供給され、第1のピラーと、該第1のピラーに隣接する第2のピラーの少なくとも一部とは平面視して、第1のピラー及び第2のピラーの側面を構成する面のうち、熱酸化速度及び/又はエッチング速度が最大の面に対して45°の方向に沿って配置されていることを特徴とする。

(もっと読む)

自己整列グラフェン・トランジスタ

【課題】自己整列グラフェン・トランジスタを作製するスキームを提供する。

【解決手段】グラフェン電界効果トランジスタは、ゲート・スタックであってシード層とシード層の上に形成されたゲート酸化物とゲート酸化物の上に形成されたゲート金属とを含む該ゲート・スタック、絶縁層、およびシード層と絶縁層との間に転写されたグラフェン・シート、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの面積を小さくしてもフリッカノイズを低減できる半導体装置を提供する。

【解決手段】本発明の一態様の半導体装置は、シリコン基板1に形成された第1及び第2のP型低濃度不純物層3a,3bと、シリコン基板1に埋め込まれて形成され、第1及び第2のP型低濃度不純物層の相互間に位置する埋め込みチャネル層5と、埋め込みチャネル層の上方に位置するシリコン基板の表面上にゲート絶縁膜6を介して形成され、N型不純物が導入されたポリシリコン膜からなるゲート電極と、第1のP型低濃度不純物層3a内における深さが浅い領域に形成されたソース領域及びドレイン領域の一方のP型層13aと、第2のP型低濃度不純物層3b内における深さが浅い領域に形成されたソース領域及びドレイン領域の他方のP型層13bと、を具備することを特徴とする。

(もっと読む)

141 - 160 / 992

[ Back to top ]