Fターム[4M104EE18]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 材質 (4,070) | 有機物 (303)

Fターム[4M104EE18]に分類される特許

1 - 20 / 303

層選択レーザーアブレーションパターニング

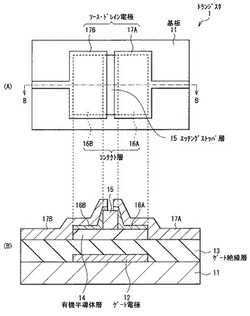

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

半導体装置の製造方法

【課題】SiC半導体基板の裏面電極は、低コンタクト抵抗を実現するために、ニッケル等のシリサイド形成用メタル膜を堆積後、PDAとして摂氏1000度程度の熱処理を必要とする。この熱処理を通常の熱処理やRTAで実行する場合には、ウエハの表面側がアルミニウム等の融点を超えるため、アルミニウム膜等の形成前に実施しなければならないという制約がある。また、既存の紫外線レーザを用いたレーザアニールでは、コンタクト抵抗を十分に下げられないという問題がある。

【解決手段】本願の一つの発明は、SiC基板の表面側にアルミニウム系メタル膜が形成された状態で、裏面にシリサイド形成用メタル膜を成膜し、この裏面に対してレーザビームによってシリサイド化処理を実行する半導体装置の製造方法であって、このレーザビームを、前記シリサイド形成用メタル膜を実質的に透過しない波長域に属する可視光とするものである。

(もっと読む)

窒化物半導体装置

【課題】電極のコンタクト抵抗や逆方向リーク電流を低減できる窒化物半導体装置を提供する。

【解決手段】窒化物半導体層103と、窒化物半導体層103よりもバンドギャップが大きい窒化物半導体層104との接合体が少なくとも1つ基板101上に積層されている。窒化物半導体層104の上面から窒化物半導体層103における窒化物半導体層104との界面よりも下側までの範囲に位置する部分の前記接合体の両側端にテーパ部108及び109が形成されている。テーパ部108の側面上には窒化物半導体層103とショットキー接触するようにアノード電極106が形成されており、テーパ部109の側面上には窒化物半導体層103とオーミック接触するようにカソード電極107が形成されている。各テーパ部108及び109の側面が基板101の主面に対してなす角度は、20度以上で且つ75度以下である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

電極及びそれを用いた有機電子デバイス

【課題】有機電子デバイスにおいて、仕事関数を制御することにより、電極から有機半導体への電荷注入障壁をより小さくすることが可能となる銀ナノ粒子を適用した電極及びそれを用いた有機電子デバイスを提供する。

【解決手段】平均粒径が30nm以下であり、沸点が100〜250℃の範囲内にある中短鎖アルキルアミンと沸点が100〜250℃の範囲内にある中短鎖アルキルジアミンを主成分とする保護分子により覆われた銀ナノ粒子を有機電子デバイス用電極として用いる。

(もっと読む)

炭化ケイ素デバイス用のエッジ終端構造およびエッジ終端構造を含む炭化ケイ素デバイスの製造方法

【課題】炭化ケイ素デバイスの改善されたエッジ終端構造を提供する。

【解決手段】炭化ケイ素半導体デバイス用のエッジ終端構造は、少なくとも炭化ケイ素ベース接合を部分的に取り囲んで、炭化ケイ素層中において、所定間隔で配置された複数の同心円のフローティングガードリング34を有すると共に、フローティングガードリング上に設けられた絶縁層、及びフローティングガードリング同士の間でかつ炭化ケイ素層の表面の近くに設けられた炭化ケイ素表面電荷補償領域38を有する。炭化ケイ素層上に窒化ケイ素層56が設けられ、窒化ケイ素層上に有機保護層66が設けられる。酸化膜層が窒化ケイ素層と炭化ケイ素層の表面との間に存在してもよい。エッジ終端構造の形成・製造方法を開示されている。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

ダイオード素子及び検出素子

【課題】従来の横型のダイオード素子は、表面二電極間における電流経路に半導体界面が現れるため、界面状態に起因する雑音が大きいという点を解決するダイオード素子、検出素子等を提供する。

【解決手段】ダイオード素子は、第一の導電型の低濃度キャリア層103と、第一の導電型の高濃度キャリア層102と、半導体表面上に形成されたショットキー電極104及びオーミック電極105と、を備える。低濃度キャリア層のキャリア濃度は、高濃度キャリア層のキャリア濃度より低く、オーミック電極の直下に第一の導電型の不純物導入領域106が形成される。ショットキー電極及びオーミック電極の間の半導体表面に、ショットキー電極とは電気的に接触しない第二の導電型の不純物導入領域107が形成され、第二の導電型の不純物導入領域が第一の導電型の不純物導入領域と接する。

(もっと読む)

有機トランジスタ及びその製造方法

【課題】ソース、ドレイン電極と有機半導体層の間の接触抵抗を低減して、短チャネル化により高速応答性能を向上させ、かつ、短チャネル化に伴うソース、ドレイン電極とゲート電極間の短絡の発生を回避可能とする。

【解決手段】絶縁性の基板と、基板上に相互間に間隔を設けて配置され、各々台状平面を形成する一対の絶縁性の台座2、3と、一方の台座が形成する台状平面上に設けられたソース電極4と、他方の台座が形成する台状平面上に設けられたドレイン電極5と、一対の台座の間の基板上に設けられたゲート電極6と、ソース電極及びドレイン電極の上面に接触させて配置された有機半導体層7とを備える。ゲート電極と有機半導体層の下面とはギャップ領域8を介在させて上下方向に対向し、ギャップ領域に面する台座の側面は、上側端縁に対して下側端縁がゲート電極から遠ざかる側に後退した形状を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、保護膜の境界面での膜厚を厚くし、はんだが金属膜の下方に侵入し難い半導体装置を提供することを目的とする。

【解決手段】基板10と、

該基板に積層された金属膜30と、

該金属膜に積層されたはんだ層40と、

前記基板に積層され、前記金属膜及び前記はんだ層に接するように形成されたポリイミドからなる保護膜50とを備え、

該保護膜は、前記金属膜と接する界面において、前記基板から離れるにつれて前記金属膜側に迫り出す形状を有することを特徴とする。

(もっと読む)

絶縁膜形成用印刷インキ組成物、該絶縁膜形成用印刷インキ組成物から形成された絶縁膜。

【課題】 良好な絶縁特性を有する絶縁膜の形成に使用される高精細印刷インキ組成物および該印刷インキ組成物から形成された絶縁膜を提供すること。

【解決手段】 少なくとも不揮発性成分と溶剤を含有する絶縁膜形成用印刷インキ組成物であって、反転オフセット印刷、剥離オフセット印刷、マイクロコンタクト印刷のいずれかに用いられ、ポリシロキサンが不揮発性成分の75重量%以上であることを特徴とする絶縁膜形成用印刷インキ組成物。

(もっと読む)

電極・配線用導電体

【課題】金属粒子の焼結体から構成された導電体を微細化された電極・配線とした場合でも腐蝕やマイグレーションの発生を長期間防止可能な電極・配線用導電体を提供する。

【解決手段】金属粒子の焼結体から構成された導電体薄膜上に、下記一般式(1)で表されるチオール化合物または下記一般式(2)で表されるスルフィド化合物から選択される少なくともいずれか一種の化合物を含有する金属イオン移動防止膜を設け、且つ、前記金属イオン移動防止膜中に凝集体構造が含まれてなる電極・配線用導電体とする。

Ar−SH…(1)[式(1)中、Arはベンゼン環を示し、置換基を有していてもよい。]

(A−R’−O−R−S)2…(2)[式(2)中、R’、Rはアルキレン基を示し、Aはフルオロアルキル基を示す。]

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

半導体装置

【課題】本発明は、金属膜の端部の応力により金属膜の端部直下の表面電極がダメージを受けることを防止できる半導体装置を提供することを目的とする。

【解決手段】本発明に係る半導体装置は、基板24と、該基板24の上に、アルミを含む材料で形成された表面電極26と、該表面電極26の上に、はんだ付け可能な材料で形成された金属膜28と、該表面電極26の上の部分と、該金属膜28の端部に重なる重畳部分30aとが一体的に形成されて該金属膜28の端部を固定する端部固定膜30と、を備えたことを特徴とする。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】炭化珪素ショットキーダイオードの製造において、ダイオードの順方向特性、特に障壁高さφBを安定させて、リーク電流のばらつきを低減させることが可能な半導体装置を提供する。

【解決手段】エピタキシャル層2上に乾式熱酸化によりシリコン酸化膜OX1を形成し、SiC基板1の裏面にオーミック電極3を形成し、その後、SiC基板1をアニールしてオーミック電極3とSiC基板1の裏面との間にオーミック接合を形成し、シリコン酸化膜OX1を除去した後、エピタキシャル層2上にショットキー電極4を形成する。その後、シンターを行い、ショットキー電極4とエピタキシャル層との間にショットキー接合を形成する。

(もっと読む)

半導体装置の製造方法と半導体装置

【課題】半導体基板の表面のAl層の表面が荒れることを抑制しつつ、リフトオフの後に溶解層が剥離せずに残ることを防止し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板12の表面にAl層14を形成し、Al層14の表面にTiN層16を形成し、TiN層16の表面の一部に絶縁層20を形成し、TiN層16と絶縁層20の表面に溶解層を形成し、溶解層の表面にレジスト層を形成し、溶解層とレジスト層の一部を除去して溶解層開口部を形成してTiN層16の一部を露出させ、レジスト層の表面、及び、露出したTiN層16の一部の表面にTi層30及びNi層40を形成し、アルカリ溶液によって溶解層を溶解させることにより、溶解層とともに、レジスト層とその表面に形成されたTi層及びNi層を除去する。

(もっと読む)

半導体装置の製造方法

【課題】電極パターンが基板支持台に直接押し付けられることによって生じる電極パターンへのダメージの発生を防止することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板40の表面S1上に電極パターン41が形成される。半導体基板40の表面S1上において電極パターン41を覆う絶縁膜43が形成される。成膜装置の基板支持台100上に、絶縁膜43が基板支持台100に接するように半導体基板40が取り付けられる。基板支持台100に取り付けられた半導体基板40の裏面上に成膜装置によって電極層44が堆積される。電極層44が堆積された後に、電極パターン41の少なくとも一部が露出するように絶縁膜43がパターニングされる。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

1 - 20 / 303

[ Back to top ]