Fターム[4M104FF04]の内容

Fターム[4M104FF04]に分類される特許

1 - 20 / 267

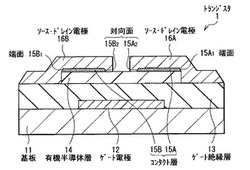

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

窒化物半導体装置

【課題】電極のコンタクト抵抗や逆方向リーク電流を低減できる窒化物半導体装置を提供する。

【解決手段】窒化物半導体層103と、窒化物半導体層103よりもバンドギャップが大きい窒化物半導体層104との接合体が少なくとも1つ基板101上に積層されている。窒化物半導体層104の上面から窒化物半導体層103における窒化物半導体層104との界面よりも下側までの範囲に位置する部分の前記接合体の両側端にテーパ部108及び109が形成されている。テーパ部108の側面上には窒化物半導体層103とショットキー接触するようにアノード電極106が形成されており、テーパ部109の側面上には窒化物半導体層103とオーミック接触するようにカソード電極107が形成されている。各テーパ部108及び109の側面が基板101の主面に対してなす角度は、20度以上で且つ75度以下である。

(もっと読む)

半導体装置とその製造方法

【課題】製造プロセスが容易であり、かつ、電流駆動能力の高い半導体基板およびその製造方法を提供することである。

【解決手段】本実施形態による半導体装置は、半導体基板を備える。第1導電型のFin型半導体層は、半導体基板上に形成されている。第1導電型のソース層および第1導電型のドレイン層は、Fin型半導体層の長手方向の両端に設けられている。ゲート絶縁膜は、Fin型半導体層の両側面に設けられている。ゲート電極は、Fin型半導体層の両側面にゲート絶縁膜を介して設けられている。第2導電型のパンチスルーストッパ層は、ゲート電極およびFin型半導体層の下に設けられている。パンチスルーストッパ層の不純物濃度は、ソース層およびドレイン層の下にある半導体基板の不純物濃度よりも高い。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】酸化物半導体層、及びチャネル保護層を覆うようにソース電極層、及びドレイン電極層となる導電膜を形成した後、酸化物半導体層、及びチャネル保護層と重畳する領域の導電膜を化学的機械研磨処理により除去する。ソース電極層、及びドレイン電極層となる導電膜の一部を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、チャネル保護層を有することにより、導電膜の化学的機械研磨処理時に当該酸化物半導体層に与える損傷、または膜減りを低減できる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置、及びその作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置を提供する。また、微細化された半導体装置を歩留まりよく提供する。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体膜と、酸化物半導体膜の側面に接して設けられ、かつ酸化物半導体膜よりも膜厚が大きいソース電極層及びドレイン電極層と、酸化物半導体膜、ソース電極層、及びドレイン電極層上に設けられたゲート絶縁膜と、酸化物半導体膜の上面と、ソース電極層及びドレイン電極層の上面との間に生じた段差により生じた凹部に設けられたゲート電極層と、を有する構造である。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】チャネル長方向の一方の側面においてソース電極層と接し、チャネル長方向の他方の側面においてドレイン電極層と接する酸化物半導体層を含むトランジスタとすることでソース電極層とドレイン電極層の間の電界を緩和して、短チャネル効果を抑制する。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極膜に注入したイオンがチャネル領域に達してMISFETの電気特性に影響を与えていた。

【解決手段】半導体基板の主面上にゲート絶縁膜を介して形成されるとともに、第1導電型となる不純物を含んだシリコンを主体とする第1ゲート電極膜と、前記第1ゲート電極膜上に形成されるとともに、酸素及び窒素のうち一方又は両方を含んだシリコンを主体とする介在層と、前記第1ゲート電極膜上に前記介在層を介して形成されるとともに、前記第1導電型となる不純物を含んだシリコンを主体とする第2ゲート電極膜と、を含む電界効果トランジスタを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

SiCエピタキシャルウエハおよびそれを用いたSiC半導体素子

【課題】高品質かつ高信頼性の素子を作製できるSiCエピタキシャルウエハ、およびそれを用いて得られるSiC半導体素子を提供すること

【解決手段】4°以下のオフ角を有するSiC基板2と、SiC基板2の主面4に形成され、その表面10に0.5nm以上の高さのステップバンチング9が形成されたSiCエピタキシャル層3とを含むSiCエピタキシャルウエハ1において、ステップバンチング9の線密度を40cm−1以下にする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

半導体装置

【課題】低オン抵抗であって、かつ、ノーマリーオフの電界効果型トランジスタを提供する。

【解決手段】基板10の上に形成された電子走行層11と、電子走行層11の上に、電子走行層11よりもバンドギャップの広い半導体により形成された電子供給層12と、電子供給層12の上に、電子供給層よりもバンドギャップの狭い半導体により形成されたバリア形成層13と、バリア形成層13の上に、不純物のドープされた半導体により形成された上部チャネル層14と、バリア形成層13及び上部チャネル層14を除去することにより形成されたバリア形成層13及び上部チャネル層14の側面と、側面に形成された絶縁膜20と、絶縁膜20を介し形成されたゲート電極21と、上部チャネル層14と接続されるソース電極22と、電子供給層12または電子走行層11と接続されるドレイン電極23と、を有する。

(もっと読む)

半導体装置

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、製造コストを低減し、さらにゲート電極およびゲートコンタクトの抵抗を低減した半導体装置およびその製造方法を提供することを目的とする。

【解決手段】本発明にかかる半導体装置は、ゲート電極7の少なくとも上層は、第2金属シリサイド膜としてのWSix膜72からなり、第1金属シリサイド膜としてのNiSi2膜18に含まれる第1金属(Ni)とシリコンとの結合エネルギーが、WSix膜72に含まれる第2金属(W)とのシリコンとの結合エネルギーよりも小さく、WSix膜72の組成MSix(Mは第2金属を示す)において、xが1.5以上2.0未満であることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】性能および製造安定性を向上させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、第1の面および第2の面を有する有機半導体部と、第1の面に隣接されたソース電極部と、第2の面に隣接されたドレイン電極部とを備える。ソース電極部およびドレイン電極部のうちの少なくとも一方は、有機半導体部よりも高導電性の有機半導体材料を含む高導電性電極部である。

(もっと読む)

1 - 20 / 267

[ Back to top ]