Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

21 - 40 / 1,113

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】Cu配線内における空孔の集中を抑制することでCu配線内でのボイドの形成を抑え、例えば2層間配線系におけるビア接続部等における、いわゆるストレスマイグレーションと呼ばれる断線等の配線不良の発生が抑制される半導体装置の製造方法を提供する。

【解決手段】ダマシン配線構造を有する半導体装置の製造方法において、配線形成後に被処理基板を加熱および除熱する熱サイクル工程を行う、半導体装置の製造方法が提供される。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

Ru含有酸素拡散バリア

【課題】メモリデバイス中の酸素拡散バリアとしてRuおよび/またはRuO2を選択的に形成する方法と、そのようなRu系拡散バリアを有するメモリデバイスを提供する。

【解決手段】MIMキャパシタ構造を形成する方法は、導電性の下部電極プラグ33を露出させるリセスを備えたベース構造を得る工程と、ベース構造材料に比較した下部電極プラグ上へのRu成長の培養時間の違いに基づいて、下部電極プラグ上にRu50を選択成長させる工程と、選択成長したRu50を酸化する工程と、酸化したRu50の上にRu含有下部電極60を堆積する工程と、Ru含有下部電極60の上に誘電体層70を形成する工程と、誘電体層70の上に導電性の上部電極71を形成する工程とを含む。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】容量素子上の配線層の設計自由度に優れた半導体装置を提供する。

【解決手段】半導体装置は、基板、層間絶縁層、第1トランジスタ、多層配線層、容量素子、金属配線、及び第1コンタクトを備える。基板1上には、層間絶縁層4、5が設けられている。第1トランジスタ3aは、半導体基板1に設けられており、層間絶縁層内に埋め込されている。第1トランジスタは、少なくともゲート電極32及び拡散層を有する。層間絶縁層上には、多層配線層が設けられている。容量素子19は、多層配線層内に設けられている。金属配線(ゲート裏打ち配線)30は、ゲート電極32の上面と接しており、層間絶縁層4内に埋設されている。第1コンタクト10aは、第1トランジスタ3aの拡散層に接続しており、層間絶縁層4内に埋設される。金属配線(ゲート裏打ち配線)30は、第1コンタクト10aと同じ材料で構成されている。

(もっと読む)

半導体装置の製造方法

【課題】所定の安定した特性を有するN−MISFETとP−MISFETとを備えた半導体装置を容易に実現できるようにする。

【解決手段】半導体装置の製造方法は、半導体基板101の上に高誘電体膜121と、第1の膜122と、犠牲導電膜123と、第2の膜124とを順次形成した後、第2の膜124におけるN−MISFET形成領域101Nに形成された部分を第1の薬液を用いて選択的に除去する。この後、第2の膜124に含まれる第2の金属元素を犠牲導電膜124におけるP−MISFET形成領域101Pに形成された部分に拡散させる。続いて、犠牲導電膜124及び第1の膜122におけるN−MISFET形成領域101Nに形成された部分を、それぞれ第2の薬液及び第3の薬液を用いて選択的に除去する。第3の膜125を形成した後、第3の膜125に含まれる第3の金属元素を高誘電体膜121中に拡散させる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、インジウムを含む酸化物半導体膜、ゲート電極層と重畳する酸化物半導体膜上に接する絶縁層が順に積層され、酸化物半導体膜及び絶縁層に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、絶縁層表面における塩素濃度を1×1019/cm3以下とし、かつインジウム濃度を2×1019/cm3以下とする。

(もっと読む)

炭化珪素半導体装置及びその製造方法

【課題】ショットキー電極形成前に酸洗浄を行ってもp型オーミック電極がその酸に曝されることなく、p型オーミック電極とショットキー電極との電気的接続が良好な炭化珪素半導体装置及びその製造方法を提供する。

【解決手段】本発明の炭化珪素半導体装置は、炭化珪素基板1と、基板1上に形成されたn型炭化珪素層2と、n型炭化珪素層2の表面近傍に形成された複数のp型不純物領域3と、p型不純物領域3上の一部に形成されたp型オーミック電極4と、p型不純物領域3上の一部に、p型オーミック電極4を覆うように形成された耐酸性のバリアメタル層5と、バリアメタル層5、p型不純物領域3、及びn型炭化珪素層2上に形成されたショットキー電極6と、ショットキー電極6上に形成された第1の電極と、炭化珪素基板1のn型炭化珪素層が形成されていない側に形成された第2の電極と、を備えたことを特徴とする。

(もっと読む)

表示装置用配線構造

【課題】450〜600℃程度の高温下に曝されてもヒロックが発生せず高温耐熱性に優れており、配線構造全体の電気抵抗(配線抵抗)も低く抑えられており、更にフッ酸耐性にも優れた表示装置用配線構造を提供する。

【解決手段】本発明の表示装置用配線構造は、基板側から順に、Ta、Nb、Re、Zr、W、Mo、V、Hf、Ti、CrおよびPtよりなる群(X群)から選択される少なくとも一種の元素と、希土類元素の少なくとも一種とを含むAl合金の第1層と;Ti、Mo、Al、Ta、Nb、Re、Zr、W、V、Hf、およびCrよりなる群(Y群)から選択される少なくとも一種の元素の窒化物、またはAl合金の窒化物の第2層と、が積層された表層構造を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】プラグが微細化しても埋め込み不良が生じることなく、低コストで形成することができ、さらに種々の半導体装置に適用可能であるプラグ及びその形成技術を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上に酸化シリコン膜を形成し、酸化シリコン膜にビアを形成し、ビア内側に密着層を形成し、密着層上にシリコン層を形成し、タングステンを含むガスをシリコン層と反応させることにより、ビアに埋め込まれたタングステン膜を形成する。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】中間層の形成時に、第2コイル46および第3コイル61によってターゲット53と基体11との間に磁力線M1が通るように磁場を発生させることによって、溝部12の内壁面に均一な厚みで中間層を成膜することが可能になる。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】溝部12を除いた基体11の一面11a、即ち溝部12の頂面にエッチングカバー層14を形成する。エッチングカバー層14は、例えば、Ta,Tiまたはこれらを含む合金から構成される。エッチングカバー層14の形成は、例えば、スパッタリング法を用いることが好ましい。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

半導体装置の製造方法

【課題】電気めっき装置のハードウェアトラブルを低減しながら、銅めっき膜の均一性を保つ。

【解決手段】自動分析器14は、電極16,17間に印加されている電圧を検出し、その電圧値が設定電圧範囲内であるか否かを判断する。検出した電圧値が、設定電圧範囲の下限値よりも低い場合、自動分析器14は、検出した電圧値に基づいて、基本液の不足量を算出し、バルブ11を制御して不足分の基本液を補充した後、めっき液タンク6内のめっき液が規定量を保つようにバルブ13の動作制御を行い、めっき液を廃液する。また、検出した電圧値が設定電圧範囲の上限値よりも高い場合、検出した電圧値に基づいて基本液の超過量を算出し、バルブ12を制御して基本液の濃度が規定範囲内となるように純水をめっき液タンク6に補充してめっき液を薄めた後、バルブ13を制御して規定量を保つようめっき液を廃液する。

(もっと読む)

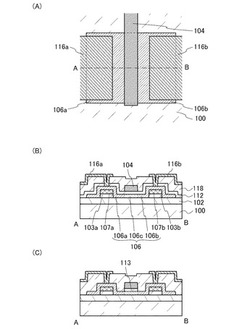

半導体装置および半導体装置の作製方法

【課題】半導体装置の特性を損なうことがない半導体装置およびその作製方法を提供する。

【解決手段】酸化物半導体層を含むトランジスタ(半導体装置)において、電極層を酸化物半導体層の下部に接して形成し、不純物を添加する処理により酸化物半導体層に自己整合的にチャネル形成領域と、チャネル形成領域を挟むように一対の低抵抗領域を形成する。また、電極層および低抵抗領域と電気的に接続する配線層を絶縁層の開口を介して設ける。

(もっと読む)

デバイスの製造方法および製造装置

【課題】スパッタリング法により、被処理基板の一面に形成されたチタンナイトライド膜上にタングステンシリサイド膜を形成する際に、タングステンシリサイド膜に含ませるシリコン原子の割合を微細制御することを可能にする、デバイスの製造方法を提供する。

【解決手段】被処理基板の一面103aに、チタンナイトライド膜109、タングステンシリサイド膜110、タングステン膜111の順に堆積してなるデバイスの製造方法であって、タングステンシリサイド膜110をスパッタリング法により形成する際に、タングステン原子からなるターゲット102と、シリコン原子を含むプロセスガスを少なくとも用いる。

(もっと読む)

半導体装置及びその製造方法

【課題】 エレクトロマイグレーション耐性及び信頼性に優れた半導体装置及びその製造方法を提供する。

【解決手段】 基板上に絶縁膜を形成する工程と、前記絶縁膜をエッチングして配線溝を形成する工程と、前記配線溝内に銅膜を形成し、銅配線を形成する工程と、前記銅配線及び前記絶縁膜の表面を平坦化する工程と、平坦化された前記銅配線及び絶縁膜上に金属膜を形成する工程と、酸素を含んだ雰囲気中で加熱を行うことにより前記銅配線上の前記金属膜と前記銅配線とを選択的に反応させて合金膜を形成するとともに前記絶縁膜上の前記金属膜を酸化して絶縁性の膜に変化させる工程と、前記合金膜及び前記絶縁性の膜上にブロック膜を形成する工程とを備えた半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法、半導体装置

【課題】微細な溝部の内部に隙間無く導電材料を埋め込み、導電性に優れた配線を得ることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】バリア層(バリアメタル)13を覆うようにライナー層14が形成されている。ライナー層14は、Ni(ニッケル)から構成される。ライナー層14は、このライナー層14の内側に形成されるCu(銅)からなる導電体15に対する濡れ性を高め、かつ、溝部12の内側の平滑性を高める。

(もっと読む)

21 - 40 / 1,113

[ Back to top ]