Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

101 - 120 / 1,113

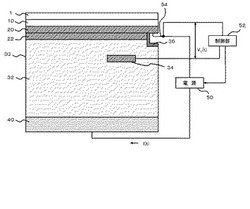

半導体装置の製造方法及びめっき装置

【課題】めっき膜の成膜が進んでも、被めっき面の表面電位と所望する表面電位との誤差が生じることを抑制できる半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、半導体基板1に形成されたシード膜20を、めっき液32に接触させる工程と、シード膜20にカソード電極54を接続し、シード膜20とめっき液32中のアノード電極40との間で電流を流すことにより、シード膜20上にめっき膜22を形成する工程と、を備え、めっき膜22を形成する工程において、めっき液20中に挿入された参照電極34とカソード電極54との間の電位差、またはカソード電極54とアノード電極40の電位差を、時間の経過と共に徐々に下げる工程を有する。

(もっと読む)

成膜方法およびリスパッタ方法、ならびに成膜装置

【課題】トレンチおよび/またはホールの間口のオーバーハングを抑制することができる成膜方法およびリスパッタリング方法を提供すること。

【解決手段】処理容器内にプラズマ生成ガスを導入しつつ誘導結合プラズマ生成機構により処理容器内に誘導結合プラズマを生成し、直流電源から金属ターゲットに直流電力を供給し、バイアス電源により載置台に高周波バイアスを印加して、載置台上の被処理基板に金属薄膜を堆積させる工程と、誘導結合プラズマ生成機構によるプラズマの生成と直流電源への給電を停止し、処理容器内にプラズマ生成ガスを導入しつつ載置台に高周波バイアスを印加して、処理容器内に容量結合プラズマを形成するとともにプラズマ生成ガスのイオンを被処理基板に引き込んで堆積された金属薄膜をリスパッタリングする工程とを有する。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】ドレイン電極とドレイン層とのコンタクト抵抗を低減できる半導体素子及び半導体素子の製造方法を提供する。

【解決手段】半導体素子は、第1導電型のドレイン層と、ドレイン層上に形成された第1導電型のドリフト層と、ドリフト層上に選択的に形成された第2導電型のベース層と、ベース層上に選択的に形成された第1導電型のソース層と、ゲート絶縁膜を介して、ドリフト層、ベース層及びソース層に跨って形成されたゲート電極と、ベース層及びソース層に電気的に接続されたソース電極と、ドリフト層を貫通して、底部の少なくとも一部がドレイン層にまで達する第1のトレンチ内に形成され、ドレイン層と電気的に接続されたドレイン電極と、を備え、底部には、凹凸が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高集積化を図ることができる半導体装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上に設けられ、相互に平行に延びる複数本の積層体であって、前記半導体基板上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ゲート電極上に設けられた絶縁膜と、を有する積層体と、前記ゲート電極の上端部の側面を覆い、前記ゲート電極における前記ゲート絶縁膜に接する部分の側面は覆わない絶縁側壁と、前記半導体基板上に設けられ、前記積層体を覆う層間絶縁膜と、前記層間絶縁膜内における前記積層体の相互間に設けられ、前記半導体基板に接続されたコンタクトと、を備える。

(もっと読む)

半導体装置の製造方法

【課題】高集積化を図ることができる半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板に第1の方向に延びる複数の溝を形成する工程と、前記溝の内面上及び前記半導体基板の上面上に絶縁膜を形成する工程と、前記絶縁膜上に、前記溝を埋めるように、第1の導電層を堆積する工程と、前記第1の導電層上に第2の導電層を堆積する工程と、前記第2の導電層上における前記溝の直上域の一部を含む領域にハードマスクを形成する工程と、前記ハードマスクをマスクとして前記第2の導電層をエッチングすることにより、前記ハードマスク及び前記第2の導電層を含む柱状体を形成する工程と、前記柱状体における前記溝の幅方向に面する2つの側面上に、電極加工側壁を形成する工程と、前記柱状体及び前記電極加工側壁をマスクとしてエッチングすることにより、前記第1の導電層における露出した部分の上部を除去し下部を残留させる工程と、前記電極加工側壁を除去する工程とを備える。

(もっと読む)

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】トランジスタのチャネル部が形成される領域にU字状の縦長溝を形成し、見かけ上のチャネル長に対してチャネル長を長くする方法は、溝を掘るためにフォトリソグラフィ工程を余分に行う必要があり、コストや歩留まりの観点で問題があった。

【解決手段】ゲート電極または絶縁表面を有する構造物を利用し、三次元形状のチャネル領域を形成することにより、チャネル長が、上面から見たチャネル長に対して3倍以上、好ましくは5倍以上、さらに好ましくは10倍以上の長さとする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】特性の良好な半導体装置を形成する。

【解決手段】本発明は、pチャネル型MISFETをpMIS形成領域1Aに有し、nチャネル型MISFETをnMIS形成領域1Bに有する半導体装置の製造方法であって、HfON膜5上にAl膜8aを形成する工程と、Al膜上にTiリッチなTiN膜7aを形成する工程と、を有する。さらに、nMIS形成領域1BのTiN膜およびAl膜を除去する工程と、nMIS形成領域1BのHfON膜5上およびpMIS形成領域1AのTiN膜7a上にLa膜8bを形成する工程と、La膜8b上にNリッチなTiN膜7bを形成する工程と、熱処理を施す工程とを有する。かかる工程によれば、pMIS形成領域1Aにおいては、HfAlON膜のN含有量を少なくでき、nMIS形成領域1Bにおいては、HfLaON膜のN含有量を多くできる。よって、eWFを改善できる。

(もっと読む)

表示装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】電極材料が拡散するのを抑制し、特性の向上を実現する。

【解決手段】半導体装置を、ゲート電極3とゲート絶縁膜2との間、Al含有オーミック電極4、5とAu配線9との間、及び、ゲート電極3の下方及びAl含有オーミック電極4、5の上方、のいずれかに設けられ、第1TaN層6A、Ta層6B、第2TaN層6Cを順に積層した構造を有する電極材料拡散抑制層6を備えるものとする。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】表示装置に含まれるTFTのゲート電極と、ソース電極及びドレイン電極との間の絶縁耐圧が低くなる場合がある。

【解決手段】表示装置であって、基板上に形成されるゲート電極と、前記ゲート電極上に、前記ゲート電極を覆うように形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体層と、前記半導体層上に形成されたソース配線と、前記半導体層上に形成されたドレイン配線と、を有し、前記半導体層は、前記ゲート電極の上方に形成されたチャネル層と、前記チャネル層の両側に、それぞれ前記ソース配線またはドレイン配線を介して分離して形成されたエッチング防止層と、を有する、ことを特徴とする。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、段差被覆性が良好でかつ再現性高くCo膜を成膜することができる成膜方法を提供すること。

【解決手段】処理容器1内に単一原料として気体状のCo4(CO)12を供給し、基板W上でCo4(CO)12を熱分解させて基板W上にCo膜を成膜する。このとき、成膜原料として固体原料であるCo2(CO)8を用い、これをCo2(CO)8の分解開始温度未満の温度で気化させ、これにより生成された気体状のCo2(CO)8をCo4(CO)12が安定に存在する温度にして気体状のCo4(CO)12に変化させ、処理容器1内に供給する。または、成膜原料として固体原料であるCo4(CO)12を用い、これを気化させて処理容器1内に供給する。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてコバルトカルボニルを用いてCo膜を成膜する場合に、下地との密着性を良好にすることができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、処理容器1内に気体状のコバルトカルボニルを供給し、基板W上でコバルトカルボニルを熱分解させて基板W上にCo膜を成膜するにあたり、基板WのCo膜の下地が、Co膜との界面近傍に混合層を形成する材料で構成されており、基板Wの加熱温度を190〜300℃とする。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてCo2(CO)8を用いてCo膜を成膜する場合に、段差被覆性が良好でかつ再現性高くCo膜を成膜することができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、成膜原料として固体原料であるCo2(CO)8を用い、これをCo2(CO)8の分解開始温度未満の温度で気化させて気体原料とし、これを基板Wに至るまでCo4(CO)12が生成されないようにして基板Wに供給し、前記基板上で熱分解によりCo膜を成膜する。

(もっと読む)

成膜方法および記憶媒体

【課題】成膜原料としてCo2(CO)8を用いてCo膜を成膜する場合に、Co膜の針状の異常成長を抑制することができる成膜方法を提供すること。

【解決手段】処理容器1内に基板Wを配置し、基板Wの温度を160〜300℃とし、処理容器1内に気体状のCo2(CO)8を供給し、基板W上でCo2(CO)8を熱分解させて基板W上にCo膜を成膜する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】GaN系の材料により形成されるHEMTの信頼性を高める。

【解決手段】基板10の上方に形成された窒化物半導体からなる半導体層21〜24と、半導体層21〜24の上方に、金を含む材料により形成された電極41と、電極41の上方に形成されたバリア膜61と、半導体層21〜24の上方に、シリコンの酸化膜、窒化膜、酸窒化物のいずれかを含む材料により形成された保護膜50と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極同士の間の突合わせ部を挟むように形成されたコンタクトプラグ同士が、当該突合わせ部の絶縁膜内に形成されたボイドを介してショートすることを防ぐ。

【解決手段】ゲート電極G2およびG5間の突合わせ部において対向するサイドウォールSW上には、ライナー絶縁膜6と層間絶縁膜7が形成されている。サイドウォールSW同士の間において、サイドウォールSWの側壁にそれぞれ形成されたライナー絶縁膜6を接触させてサイドウォールSW間を閉塞させることにより、層間絶縁膜7とライナー絶縁膜6の内部にボイドが発生することを防ぐ。

(もっと読む)

101 - 120 / 1,113

[ Back to top ]