Fターム[4M104FF18]の内容

Fターム[4M104FF18]に分類される特許

141 - 160 / 1,113

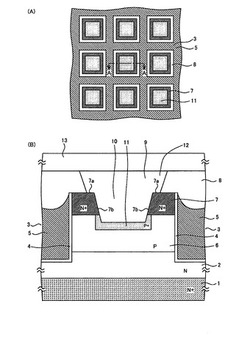

半導体装置及びその製造方法

【課題】微細化されたN+型ソース層とソース電極のコンタクト抵抗が低減されたパワーMOSトランジスタの実現を図る。

【解決手段】N型ドリフト層2の表面にP型ボディ層6を形成し、該P型ボディ層6の表面にN+型ソース層7を形成する。N+型ソース層7上を被覆する層間絶縁膜8に第1のコンタクトホール9を形成し、N+型ソース層7の一部を露出する。第1のコンタクトホール9の底面に露出したN+型ソース層7の表面からP型ボディ層6内まで第2のコンタクトホール10を形成する。第2のコンタクトホール10の底面に露出したP型ボディ層6の表面にP+型コンタクト層11を形成する。第1のコンタクトホール9の底面にフォトリソグラフィ工程のマスク合わせ精度のばらつき幅より小さい幅のN+型層7aを形成し、第1、第2のコンタクトホール9、10内をタングステン層12等で埋設する。

(もっと読む)

金属ゲート電極を有する半導体素子の製造方法

【課題】 収率が低下することなくCMOS集積回路の特性を最適可能な半導体素子の製造方法を提供する。

【解決手段】 半導体基板1の上の第1領域A内及び第2領域B内に各々形成された第1グルーブ15a及び第2グルーブ15bを有する層間絶縁膜15を形成する。次に、半導体基板1上に積層金属膜22を形成し、積層金属膜22上に非感光性を有する平坦化膜23を第1グルーブ15a及び第2グルーブ15bを充填するように形成する。第1領域A内の平坦化膜23を乾式エッチングによって選択的に除去し、第1領域A内の積層金属膜22を露出させ、第2領域B内の積層金属膜22を覆う平坦化膜パターン23pを形成する。これにより、第1領域A内の最上部金属膜を容易に除去することができるので、収率が低下することなく異なる仕事関数を有する第1金属ゲート電極及び第2金属ゲート電極を形成できる。

(もっと読む)

半導体装置の製造方法

【課題】 製造工程の増加を招くことなく、タングステン配線の低抵抗化できる半導体装置の製造方法を提供する。

【解決手段】 本発明は、基板表面に、微細形状を有する絶縁層を形成した後、この微細形状を含む絶縁層表面に、Ta膜またはTaN膜からなる下地層を形成する工程と、下地層の表面に、タングステンから膜なる配線層を形成する工程とを含む。

(もっと読む)

半導体装置およびその作製方法

【課題】新規な構造の半導体装置あるいはその作製方法を提供することを課題とする。例えば、高電圧若しくは大電流で駆動されるトランジスタの信頼性向上を図ることを課題とする。

【解決手段】トランジスタの信頼性向上を図るため、電界集中を緩和するバッファ層をドレイン電極層(またはソース電極層)と、酸化物半導体層との間に設け、バッファ層の端部をドレイン電極層(またはソース電極層)の側面から突出させた断面形状とする。バッファ層は、単層又は複数の層からなる積層で構成し、例えば窒素を含むIn−Ga−Zn−O膜、窒素を含むIn−Sn−O膜、SiOxを含むIn−Sn−O膜などを用いる。

(もっと読む)

半導体装置およびその製造方法

【課題】サリサイドプロセスにより金属シリサイド層を形成した半導体装置の信頼性を向上させる。

【解決手段】部分反応方式のサリサイドプロセスによりゲート電極8a、8b、n+型半導体領域9bおよびp+型半導体領域10bの表面に金属シリサイド層41を形成する。金属シリサイド層41を形成する際の第1の熱処理では、熱伝導型アニール装置を用いて半導体ウエハを熱処理し、第2の熱処理では、マイクロ波アニール装置を用いて半導体ウエハを熱処理することにより、第2の熱処理を低温化し、金属シリサイド層41の異常成長を防ぐ。これにより金属シリサイド層41の接合リーク電流を低減する。

(もっと読む)

半導体素子の製造方法

【課題】タングステン層の膜残りの発生を抑制する。

【解決手段】半導体基板1、コンタクトホール3を備えた絶縁膜2、絶縁膜2の表面およびコンタクトホール3の表面を被覆する被覆層4、並びに、コンタクトホール3を埋込むタングステン(W)層5を有するウエハに対し、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で高速でドライエッチングする工程と、ウエハを冷却せずに、W層5を被覆層4が露出しない範囲で、低速でドライエッチングする工程と、ウエハを冷却しつつ、被覆層4が露出するまで、W層5を低速でドライエッチングする工程と、ウエハを冷却しつつ、コンタクトホール3内のW層5を絶縁層2の高さまで低速でドライエッチングする工程と、を有する半導体素子の製造方法。

(もっと読む)

有機薄膜トランジスタの製造方法及び該方法で製造された有機薄膜トランジスタ

【課題】大面積の素子の製造が容易であり、ソース電極及びドレイン電極を形成する際にゲート絶縁層を損傷せず、有機絶縁材料が有する柔軟性を損なわない、有機薄膜トランジスタの製造方法を提供すること。

【解決手段】ゲート電極、及び該ゲート電極を被覆し、有機絶縁材料を含むゲート絶縁層を形成する工程;該ゲート絶縁層上に塗布法、無電解めっき法又は原子層堆積法を用いて導電性材料からなる第1導電層を成膜する工程;該第1導電層上にパターンニングされた第2導電層を形成する工程;該第2導電層で被覆されていない第1導電層の部分を除去して、第1導電層及び第2導電層からなるソース電極及びドレイン電極を形成する工程;及びソース電極、ドレイン電極、及び該ソース電極と該ドレイン電極に挟まれた領域のゲート絶縁層が被覆されるように、有機半導体層を形成する工程;を有する、有機薄膜トランジスタの製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】縦型トランジスタとしての機能が低下することなく、安定性の高い半導体装置を提供する。

【解決手段】活性領域T及び活性領域Tを区画する素子分離領域3が形成されて成る半導体基板1と、活性領域Tに設けられた凹部9内に形成され、上面が半導体基板1の主面からなる第1ピラー1Aと、活性領域T及び素子分離領域3に渡って形成され、第1ピラー1Aに隣接する第2ピラー2と、第1ピラー1A及び第2ピラー2の各側面を覆うように形成されたゲート電極層10と、第1ピラー1A上に形成されたエピタキシャル半導体層6と、を具備してなり、第2ピラー2が、活性領域T内において第1ピラー1Aから離間して形成された半導体凸部1Bと、素子分離領域3に埋設された埋め込み絶縁膜からなる絶縁体凸部3Aとから構成され、半導体凸部1Bの上面が埋め込み絶縁膜の一部によって被覆されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

積層構造のソース・ドレイン電極を有する有機薄膜トランジスタ

【課題】柔軟性及び耐久性に優れ、素子特性が優れ、しかも大面積化が容易なボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタを提供すること。

【解決手段】第1導電層及び第2導電層からなるソース・ドレイン電極を有するボトムゲート・ボトムコンタクト構造の有機薄膜トランジスタであって、第1導電層は、酸化タングステン、酸化銀、酸化銅、酸化亜鉛、銀塩、銀及び銅からなる群から選ばれる1種以上の材料を含み、該第2導電層は、Ag、Al、Au、Cd、Co、Cr、Cu、Fe、Mg、Mo、Ni、Pb、Pd、Pt、Sn、Ta、Ti、V、W、Zn、Zr、及びこれらの金属のいずれかを含む合金からなる群から選ばれる1種以上の材料を含む、有機薄膜トランジスタ。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

液晶表示装置及びその製造方法

【課題】製造に際して配線にヒロックが発生せず、かつエッチング形状の制御が容易な液晶表示装置を提供する。

【解決手段】液晶表示装置は、基板上にマトリクス配置された走査線と、信号線12と、前記走査線及び信号線に接続される薄膜トランジスタと、前記薄膜トランジスタに接続される画素電極27とを有する液晶表示装置において、前記走査線が下層からアルミニウム−ネオジム合金層211と高融点金属層212との積層構造からなり、前記信号線12が下層から高融点金属層231とアルミニウム−ネオジム合金層232と高融点金属層233との3層構造からなり、高融点金属の種類に応じて、ネオジム含有量を調整する。

(もっと読む)

半導体装置およびその製造方法

【課題】電極層の電気伝導度の向上と、電極層の表面へのC原子の析出の抑制とを両立させることができる半導体装置およびその製造方法をを提供する。

【解決手段】電極層16は、炭化珪素基板90上に接し、かつNi原子およびSi原子を有する。Ni原子の数はNi原子およびSi原子の総数の67%以上である。電極層16の少なくとも炭化珪素基板90に接する側はSiおよびNiの化合物を含む。電極層16の表面側においてC原子濃度はNi原子濃度よりも小さい。

(もっと読む)

配線構造

【課題】有機ELディスプレイや液晶ディスプレイなどの表示装置において、酸化物半導体層と、例えばソース電極やドレイン電極を構成する金属膜との安定した界面の形成が可能である配線構造を提供する。

【解決手段】基板の上に、基板側から順に、薄膜トランジスタの半導体層と、金属配線膜とを有しており、半導体層と金属配線膜との間にバリア層を有する配線構造であって、半導体層は酸化物半導体からなり、バリア層はTi酸化膜から構成されており、且つ、Ti酸化膜は半導体層と直接接続している。

(もっと読む)

銅の電着方法

【課題】特に半導体集積回路(IC)デバイス製造の分野において、約100nmより小さい、好適には約70nmより小さい、更に好適には約50nmより小さい、より好適には約35nmより小さい幅を有するトレンチ、バイアなどの開口部を充填する電着方法を提供する。

【解決手段】0.5mmol・l−1と50mmol・l−1との間に含まれる銅イオン濃度と、電着浴の体積あたり0.05%と10%との間に含まれる酸濃度とを有する電着浴中に基板を浸責し、銅の堆積物を電着する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】本発明は半導体装置に関する。

【解決手段】本発明は、半導体基板上のセル領域のセルトランジスタ上の層間膜を貫通してコンタクトプラグが形成され、周辺回路領域のトランジスタ上の層間膜を貫通してコンタクトプラグが形成されてなる半導体装置の製造方法であり、セルトランジスタ上の層間膜にコンタクトホールを形成し、その底部側にシリコン膜の下部導電プラグを形成する工程と、その上に金属膜を積層して積層構造のセルコンタクトプラグを形成する工程と、周辺回路用トランジスタ上の層間膜にコンタクトホールを形成し、その内部に金属膜を形成してコンタクトプラグを形成する工程とを具備し、前記セル領域のコンタクトホール内のシリコン膜上に金属膜を形成する工程と前記周辺回路領域のコンタクトホール内に金属膜を形成する工程を同時に行うことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極断線の確率を下げる。

【解決手段】半導体装置1の製造方法は、シリコン基板2の主面に絶縁体ピラー6を形成する工程と、絶縁体ピラー6の側面に保護膜12を形成する工程と、シリコン基板2の主面にシリコンピラー4を形成する工程と、シリコンピラー4の側面にゲート絶縁膜10を形成する工程と、それぞれシリコンピラー4及び絶縁体ピラー6の側面を覆い、互いに接する第1及び第2のゲート電極11,13を形成する工程とを備える。本製造方法によれば、ダミーピラーとしての絶縁体ピラー6の側面に保護膜12を形成しているので、チャネル用のシリコンピラー4をトランジスタとして加工する際にダミーピラーが削られてしまうことが防止される。したがって、ゲート電極断線の確率を下げることが可能になる。

(もっと読む)

成膜方法、成膜装置及び半導体装置の製造方法

【課題】熱CVD法によって、M(BH4)4(Mは、Zr又はHfを意味する)を原料としてM/Zr比が適正範囲内で良質なMBx膜(Mは前記と同じ意味を有し、xは1.8〜2.5の数を意味する)を成膜する。

【解決手段】ガス供給源19から、ガス供給配管15aを介してH2ガスを原料容器21内に供給する。原料容器21内では、導入されたH2ガスとの接触によって、固体原料のZr(BH4)4が気化する。そして、成膜ガスとしてのH2ガスとZr(BH4)4ガスの混合ガスが、ガス供給配管15c,15c1、シャワーヘッド11のガス拡散空間12及びガス吐出孔13を介して処理容器1内に導入され、ウエハW上の絶縁膜の表面を覆うように、ZrBx膜の薄膜が形成される。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタを用いて、高速動作が可能で、信頼性も高い半導体装置を歩留まりよく作製する。

【解決手段】絶縁膜上にマスクを形成し、該マスクを微細化する。微細化されたマスクを用いて凸部を有する絶縁層を形成し、これを用いて、微細なチャネル長(L)を有するトランジスタを形成する。また、トランジスタを作製する際に、微細化された凸部の上面と重なるゲート絶縁膜の表面に平坦化処理を行う。これにより、トランジスタの高速化を達成しつつ、信頼性を向上させることが可能となる。また、絶縁膜を凸部を有する形状とすることで、自己整合的にソース電極及びドレイン電極を形成することができ、製造工程の簡略化、また生産性を向上させることが可能となる。

(もっと読む)

141 - 160 / 1,113

[ Back to top ]