Fターム[4M104FF21]の内容

Fターム[4M104FF21]の下位に属するFターム

2以上の物質で孔埋め (943)

Fターム[4M104FF21]に分類される特許

21 - 40 / 232

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化する。

【解決手段】酸化物半導体層を含むトランジスタの作製工程において、酸化シリコン膜上に、酸化物半導体が結晶状態における化学量論的組成比に対し、酸素の含有量が過剰な領域が含まれている非晶質酸化物半導体層を形成し、該非晶質酸化物半導体層上に酸化アルミニウム膜を形成した後、加熱処理を行い該非晶質酸化物半導体層の少なくとも一部を結晶化させて、表面に概略垂直なc軸を有している結晶を含む酸化物半導体層を形成する。

(もっと読む)

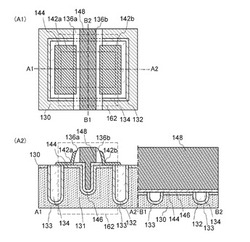

半導体装置

【課題】微細化が容易で、短チャネル効果が生じにくい半導体装置を提供する。

【解決手段】トランジスタのチャネル長方向の断面形状において、アスペクト比の大きいゲート電極上に半導体層を形成することで、トランジスタを微細化しても短チャネル効果が生じにくいチャネル長を確保できる。また、半導体層と重畳し、ゲート電極より下層に絶縁層を介して下部電極を設ける。下部電極と重畳する半導体層は、下部電極の電位(電界)により導電型が付与され、ソース領域及びドレイン領域が形成される。半導体層の、ゲート絶縁層を介してゲート電極と対向する領域は、ゲート電極がシールドとして機能し、下部電極の電界の影響を受けない。すなわち、不純物導入工程を用いることなく、自己整合によりチャネル形成領域、ソース領域及びドレイン領域を形成することができる。これにより、微細化が容易で、短チャネル効果が生じにくい半導体装置が実現できる。

(もっと読む)

薄膜の成膜方法

【課題】基板上への薄膜の成膜速度を上げ、かつトレンチやビアホールの底面に効率よく薄膜を成膜できる薄膜の形成方法を提供すること。

【解決手段】本発明の成膜方法は、開口幅又は開口径が3μm以下で、かつ、アスペクト比が1以上の段差であるトレンチ又はビアホールを有する基板上に薄膜を成膜する成膜方法であり、真空排気可能な処理室に、基板を支持する第1の電極と、前記基板に対向するように配置されターゲットを支持する第2の電極と、前記第2の電極の外側に配置されて当該第2の電極の内側にカスプ磁界を形成する複数のマグネットと、を備え、

前記処理室にNeを含む処理ガスを導入し、前記第1の電極と前記第2の電極の少なくとも一方にプラズマ形成用の高周波電力を供給すると共に、前記第2の電極上にカスプ磁場を生成してプラズマを発生させ、ターゲット物質をトレンチ又はビアホールを有する基板上に成膜する。

(もっと読む)

アモルファスシリコン膜の成膜方法および成膜装置

【課題】 表面ラフネスの精度をさらに改善でき、進展するコンタクトホールやラインなどの微細化に対応可能なアモルファスシリコンの成膜方法を提供すること。

【解決手段】 下地2を加熱し、加熱した下地2にアミノシラン系ガスを流し、下地2の表面にシード層3を形成する工程と、下地2を加熱し、加熱した下地2の表面のシード層3にアミノ基を含まないシラン系ガスを供給し、アミノ基を含まないシラン系ガスを熱分解させることで、シード層3上にアモルファスシリコン膜を形成する工程と、を備え、シード層3を形成する工程における下地の加熱温度を、アモルファスシリコン膜を形成する工程における前記下地の加熱温度よりも低くする。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】占有面積が小さく、高集積化、大記憶容量化が可能な半導体装置を提供する。

【解決手段】第1の制御ゲート、第2の制御ゲート及び記憶ゲートを有するトランジスタを用いる。記憶ゲートを導電体化させ、該記憶ゲートに特定の電位を供給した後、少なくとも該記憶ゲートの一部を絶縁体化させて電位を保持させる。情報の書き込みは、第1及び第2の制御ゲートの電位を記憶ゲートを導電体化させる電位とし、記憶ゲートに記憶させる情報の電位を供給し、第1または第2の制御ゲートのうち少なくとも一方の電位を記憶ゲートを絶縁体化させる電位とすることで行う。情報の読み出しは、第2の制御ゲートの電位を記憶ゲートを絶縁体化させる電位とし、トランジスタのソースまたはドレインの一方と接続された配線に電位を供給し、その後、第1の制御ゲートに読み出し用の電位を供給し、ソースまたはドレインの他方と接続されたビット線の電位を検出することで行う。

(もっと読む)

低抵抗材料のビーム誘起堆積

【課題】低抵抗率金属を堆積することができるビーム堆積方法を提供する。

【解決手段】ヘキサメチル二スズのようなメチル化又はエチル化金属などの低抵抗率の金属材料を堆積できる前駆体を試料表面に向けて導入し、ガリウム集束イオンビームを試料表面の所望の位置に照射して、その位置に40μΩ・cmと低い抵抗率のスズ膜を堆積する。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

ダイオードを含む半導体装置

【課題】ダイオードを含む半導体装置において、ダイオードの逆回復挙動とオン状態特性とのトレードオフを改善する。

【解決手段】半導体装置200は陰極216と陽極218を含む。陽極は第1のp型半導体陽極領域204と第2のp型半導体陽極領域206を含む。第1のp型半導体陽極領域204は陽極接触領域218に電気的に接続される。第2のp型半導体陽極領域206は、第2のp型陽極領域と陽極接触領域218間を電気的に接続または切断するように構成された、MOSFET228等のスイッチを介し陽極接触領域218に電気的に接続される。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

成膜装置

【課題】 埋め込み工程におけるスループットを向上でき、埋め込み工程が多用される半導体集積回路装置であっても、優れた生産能力を発揮することが可能な成膜装置を提供すること。

【解決手段】 アミノシラン系ガスを供給する供給機構122、及びアミノ基を含まないシラン系ガスを供給する供給機構121を備え、アミノシラン系ガスを供給して前記導電体に達する開孔を有した絶縁膜の表面、及び前記開孔の底の表面にシード層を形成する処理、及びアミノ基を含まないシラン系ガスを供給してシード層上にシリコン膜を形成する処理を、一つの処理室内101において順次実行する。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース・ドレイン領域とコンタクトプラグの接続部分の電気抵抗が低減され、かつ短チャネル効果の発生が抑えられたトランジスタを有する、n型およびp型トランジスタを含む半導体装置、およびその半導体装置の製造方法を提供すること。

【解決手段】不純物高濃度領域を有する半導体装置を提供する。前記不純物高濃度領域は、第1のソース・ドレイン領域内の前記第1のソース・ドレイン領域と前記第1のコンタクトプラグとの界面近傍に形成される。前記不純物高濃度領域の前記第1のコンタクトプラグの底面の長手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅の少なくとも一方は、前記第1のコンタクトプラグの前記底面の短手方向の前記第1のコンタクトプラグの前記底面の輪郭からの前記不純物高濃度領域の輪郭の広がり幅よりも大きい。

(もっと読む)

薄膜トランジスタとその製造方法、薄膜トランジスタアレイとその製造方法、及び、ディスプレイ装置

【課題】製造工程において半導体膜の膜質を低下させることなくその性能を維持し、少ない工程数によって、かつ、製造上の歩留まり及びスループットの優れた構造を有する薄膜トランジスタ及びその製造方法等を提供する。

【解決手段】薄膜トランジスタ100は、酸化物半導体膜120を有し、当該酸化物半導体膜120は、各薄膜半導体毎に、ゲート電極160下及び隣接された薄膜トランジスタ間とにそれぞれ形成された第1領域121及び122と、ソース電極140及びドレイン電極150下であって第1領域121の前記水平方向におけるそれぞれの両端に並設されており、ソース電極140及びドレイン電極150にそれぞれ電気的に接続され、かつ、非駆動時に前記第1領域121及び122より低抵抗である第2領域123及び124と、を有している。

(もっと読む)

トップゲート型薄膜トランジスタ及びこれを備えた表示装置

【課題】酸化物半導体層のチャネル領域の、水素拡散による低抵抗化を抑制するトップゲート型酸化物半導体TFT及びこれを備えた表示装置を提供する。

【解決手段】基板の上に、ソース電極層と、ドレイン電極層と、酸化物半導体層と、ゲート絶縁層と、In、Ga、Zn、Snの少なくとも1種類の元素を含むアモルファス酸化物半導体からなるゲート電極層と、水素を含む保護層と、を有し、ゲート絶縁層は酸化物半導体層のチャネル領域の上に形成され、ゲート電極層はゲート絶縁層の上に形成され、保護層はゲート電極層の上に形成されていることを特徴とするトップゲート型薄膜トランジスタ。

(もっと読む)

半導体装置

【課題】2DEGをチャンネルとして用いる半導体装置において、不純物イオンの侵入による悪影響を排除する。

【解決手段】第1の半導体層である電子走行層11上に、第2の半導体層である電子供給層12が形成されている。これらの界面(ヘテロ接合界面)における電子走行層11側に、2次元電子ガス(2DEG)層13が形成される。ソース電極14からドレイン電極15の間の2DEG層13が形成された領域がこの半導体装置10におけるチャンネル領域となる。このチャンネル領域上の絶縁層17上において、第1のフィールドプレート18が形成されている。すなわち、第1のフィールドプレート18は、2つの主電極のうちの一方から他方に達するチャンネル領域上を覆うように形成されている。

(もっと読む)

スパッタリング方法

【課題】 1μm以上の開口径を有する高アスペクト比のTSVホールHがパターニング形成された処理対象物に対して、被覆性よく成膜できるスパッタリング方法を提供する。

【解決手段】 真空チャンバ1内に処理対象物と、処理対象物に形成しようとする金属膜に応じて作製されたターゲット2とを対向配置し、処理対象物の全面に亘って垂直な磁場が作用するように垂直磁場を発生させ、この真空チャンバ内にスパッタガスを導入し、ターゲットに所定の電力を投入して真空チャンバ内にプラズマを形成してターゲットをスパッタリングし、処理対象物に高周波バイアス電力を投入してターゲットからのスパッタ粒子やプラズマ中で電子で電離したイオンを引き込むようにしたものにおいて、前記バイアス電力を、200〜600Wの範囲とする。

(もっと読む)

配線構造物及びその製造方法

【課題】短時間で、配線母体の内部に、種々のトポロジーの貫通配線や連結配線を埋め込むことが可能な配線構造物を提供する。

【解決手段】配線母体11と、配線母体11の内部に設けられた複数の穴部の内部にそれぞれ配置された、配線子連続体(Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1n)からなる複数の貫通配線部とを備える。複数の配線子連続体のそれぞれをなす複数の配線子Qi1,Qi2,Qi3,……,Qin-1,Qin;Qi+11,Qi+12,Qi+13,……,Qi+1n-1,Qi+1nのそれぞれは、コア部と、コア部を被覆し、コア部より融点の低い導電体からなるシェル部Qi,shell,Qi+1,shellを有する。複数の配線子は、それぞれのシェル部を互いに溶融することにより金属学的に接合される。

(もっと読む)

化合物半導体装置の製造方法及び化合物半導体装置

【課題】リフトオフ法を用いずに、簡易な手法で化合物半導体装置のゲート電極、ソース電極、及びドレイン電極を各種パターンに欠陥を生ぜしめることなく形成する。

【解決手段】AlGaN/GaN・HEMTを製造する際に、化合物半導体層上に保護絶縁膜8を形成し、保護絶縁膜8に開口を形成し、開口を埋め込む導電材料を保護絶縁膜8上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてゲート電極15(又はソース電極45及びドレイン46)を形成し、その後、保護絶縁膜8上に保護絶縁膜16を形成し、保護絶縁膜8,16に開口を形成し、開口を埋め込む導電材料を保護絶縁膜16上に形成し、導電材料上の開口上方に相当する部位にマスクを形成し、マスクを用いて導電材料をエッチングしてソース電極22及びドレイン23(又はゲート電極53)を形成する。

(もっと読む)

21 - 40 / 232

[ Back to top ]