Fターム[4M104FF21]の内容

Fターム[4M104FF21]の下位に属するFターム

2以上の物質で孔埋め (943)

Fターム[4M104FF21]に分類される特許

41 - 60 / 232

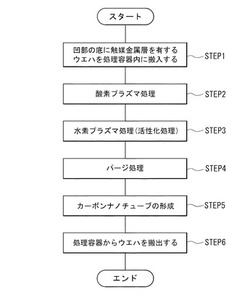

カーボンナノチューブの形成方法及びカーボンナノチューブ成膜装置

【課題】被処理体上のビアホールや配線用溝等の開口部に高密度にカーボンナノチューブ膜を埋め込むことができるカーボンナノチューブの形成方法を提供する。

【解決手段】表面に1又は複数の開口部を有し、当該開口部底面に触媒金属層が形成された被処理体を準備し(STEP1)、触媒金属層に酸素プラズマ処理を施し(STEP2)、酸素プラズマ処理後の触媒金属層に水素含有プラズマ処理を施して、触媒金属層の表面を活性化し(STEP3)、その後、触媒金属層の上にプラズマCVDによりカーボンナノチューブを成長させて、被処理体の開口部内をカーボンナノチューブで充填する(STEP5)。

(もっと読む)

電界効果トランジスタを形成するための方法および電界効果トランジスタ・デバイス

半導体装置及びその製造方法

【課題】シェアードコンタクトを備えた半導体装置において、コンタクトホールの開口不良やコンタクト抵抗の増大を防止しつつ、接合リーク電流の発生に起因する歩留まりの低下を防止する。

【解決手段】半導体基板100におけるゲート電極103の両側にソース/ドレイン領域106が形成されている。シェアードコンタクトは、ソース/ドレイン領域106とは接続し且つゲート電極103とは接続しない下層コンタクト113と、下層コンタクト113及びゲート電極103の双方に接続する上層コンタクト118とを有する。

(もっと読む)

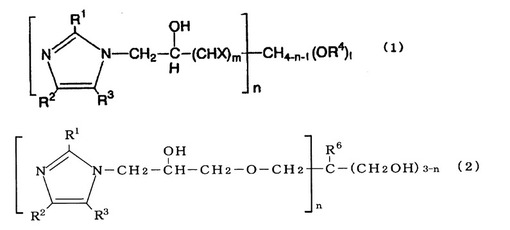

無電解めっき前処理剤

【課題】スルーホールへのめっき性に優れる無電解めっき前処理剤を提供する。

【解決手段】下記一般式(1)及び(2)で表されるイミダゾールアルコール化合物の1種又は2種以上と、パラジウム化合物とを含有する無電解めっき前処理剤。 (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】特性を劣化させることなく、微細化することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、主表面を有する半導体基板SBと、主表面に互いに間隔をおいて形成されたソース領域SRおよびドレイン領域DRと、ソース領域SRとドレイン領域DRとに挟まれる主表面上に形成されたゲート電極層GEと、ソース領域SRの表面に接するように形成された第1導電層PL1と、ドレイン領域DRの表面に接するように形成された第2導電層PL2とを備え、第1導電層PL1とソース領域SRとの接触領域CR1からゲート電極層GEの下側を通って第2導電層PL2とドレイン領域DRとの接触領域CR2まで延びるように溝REが主表面に形成されている。

(もっと読む)

高導電性のソース/ドレイン接点を有するIII族窒化物トランジスタ及びその製造方法

【課題】III族窒化物トランジスタのドレイン及びソース接点と、下位のドレイン及びソース領域の各々との間の抵抗を低減させる。

【解決手段】ゲート、ソース、及びドレイン領域上に延在するフィールド誘電体240にトレンチをエッチングする工程と、ゲート、ソース、及びドレイン領域上にゲート誘電体270を形成する工程と、ゲート誘電体上270にブランケット拡散バリア272を形成する工程と、ソース及びドレイン領域からブランケット拡散バリア272を除去する工程と、ゲート誘電体270をソース及びドレイン領域から除去し、ソース及びドレイン領域をほぼ露出させる工程とを含む。次いで、ソース及びドレイン領域に接点金属290を堆積することにより、オーミック接点を形成する。

(もっと読む)

電極構造体及びその製造方法、並びに半導体装置

【課題】精度良く形成された小型化された電極を備えた電極構造体及びその製造方法、並びに半導体装置を提供する。

【解決手段】第1の層間絶縁膜13に、第1の方向に延在する複数の第1の溝16を形成し、第1の溝16の対向する2つの側面及び底面を覆うように第1の導電膜32を形成し、第1の導電膜32が形成された複数の第1の溝16を第1の絶縁膜19で充填し、第1の層間絶縁膜13、第1の絶縁膜19、及び第1の導電膜32の上面に、第2の方向に延在する複数の開口部を有したハードマスク層33を形成し、異方性エッチング法により、複数の開口部から露出された部分の第1の絶縁膜19及び第1の導電膜32を除去することで、第1の溝16に第1の導電膜32よりなる電極を形成すると共に、第1の層間絶縁膜13に第1の溝16と交差する第2の溝17を複数形成し、ハードマスク層33を除去した後、第2の溝17を第2の絶縁膜21で充填する。

(もっと読む)

半導体発光装置

【課題】局所的な電流集中を防止して均一な発光分布を得ることができる半導体発光装置を提供する。

【解決手段】半導体発光装置は、支持基板と、支持基板上に設けられた光反射性を有する反射電極と、反射電極上に設けられた発光層を含むAlGaInP系半導体膜と、半導体膜上に設けられた表面電極と、を含む。表面電極は、半導体膜上に分散配置された複数の電極片からなるオーミック電極を含む。反射電極は、オーミック電極を構成する電極片の各々を挟んだ両側において電極片に沿うように設けられた線状のライン電極および複数の島状のドット電極からなる。ライン電極とドット電極との距離をa、オーミック電極とドット電極の水平距離をb、互いに隣接するドット電極間の距離をcとしたときに、b>a且つ0.8(a2+2ab)1/2<c<2.4(a2+2ab)1/2を満たすように表面電極および反射電極が配設される。

(もっと読む)

金属及びシリコンの交互層を含むコンタクト構造体並びに関連デバイスの形成方法

半導体デバイスを形成する方法であって、この方法は、半導体層を準備するステップと、半導体層上に第1の金属の第1の層を準備するステップとを含む。第1の金属の第1の層上に第2の層を準備することができる。第2の層は、シリコン層及び第2の金属の層を含むことができ、第1の金属及び第2の金属は異なり得る。第1の金属はチタンとすることができ、第2の金属はニッケルとすることができる。関連するデバイス、構造体、及び他の方法もまた説明される。 (もっと読む)

シリコン層の形成方法、半導体装置の製造方法

【課題】シリコン層表面の溶解を防止しつつ、エピタキシャル成長により形成された凝集性異物を除去する。清浄な表面を有し、膜厚が均一なシリコン層を形成する。

【解決手段】シリコン基板上にエピタキシャル成長によりシリコン層を形成した後に、シリコン層の表面を酸化する。このシリコン層の表面を洗浄して、エピタキシャル成長時にシリコン層の表面に発生した異物を除去する。

(もっと読む)

半導体装置の製造方法

【課題】炭化ケイ素を材料とする半導体ウェハから半導体装置を製造する方法において、表面電極と半導体基板とのショットキー接合、裏面電極と半導体基板とのオーミック接合を確保することと、製造工程を簡略化する。

【解決手段】半導体ウェハの表面に表面Mo電極を形成した後で、半導体ウェハの裏面に裏面Ni系電極を形成し、形成した表面Mo電極および裏面Ni系電極を同時にシンター処理する。表面Mo電極は、900℃以上のシンター処理を行っても、半導体基板とのショットキー接合を確保できる。裏面Ni系電極が半導体基板とオーミック接合するために必要な高温(例えば900℃以上)で、表面電極と裏面電極のシンター処理を同時に行うことができるため、製造工程が簡略化される。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

カーボン・ナノチューブを選択的に成長させる方法

【課題】1つ以上のカーボン・ナノチューブを選択的に成長させる方法を提供する。

【解決手段】本方法は、上面を有する絶縁層を基板上に形成するステップと、絶縁層内にビアを形成するステップと、ビアの側壁及び底面を含め、絶縁層上に活性金属層を形成するステップと、ビアの内部での1つ以上のカーボン・ナノチューブの選択的な成長を可能にするために、イオン・ビームを用いて上面の部分にある活性金属層を除去するステップとを含む。

(もっと読む)

薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置

【課題】薄膜トランジスタ、その製造方法及びそれを含む有機電界発光表示装置を提供する。

【解決手段】薄膜トランジスタは、基板と、上記基板上に位置するバッファ層と、上記バッファ層上に位置する半導体層と、上記半導体層上に直接接触して位置するソース/ドレイン電極と、上記基板全面にわたって位置するゲート絶縁膜と、上記ゲート絶縁膜上に位置し、上記半導体層に対応するように位置するゲート電極と、を含み、上記ソース/ドレイン電極は1つまたは多数のホールを有する。

(もっと読む)

III族窒化物半導体デバイス及びその製造方法

III族窒化物トランジスタ・デバイスを形成する方法は、III族窒化物半導体層上に保護層を形成するステップと、III族窒化物半導体の一部を露出するように保護層を貫通するビアホールを形成するステップと、保護層上にマスキングゲートを形成するステップとを含む。マスキングゲートは、ビアホールの幅より大きい幅を有する上部を含み、ビアホールの中に延びる下部を有する。この方法はさらに、マスキングゲートを注入マスクとして用いて、III族窒化物層内にソース/ドレイン領域を注入するステップを含む。 (もっと読む)

半導体装置およびその作製方法

【課題】高開口率な表示装置を提供する。

【解決手段】薄膜トランジスタと、保持容量とが設けられた画素と、走査線と、走査線に直交して設けられた信号線と、を有し、走査線の上方には、薄膜トランジスタのソース領域、ドレイン領域、及びチャネル形成領域が形成される部分と保持容量の下部電極となる部分とを有する半導体膜が設けられ、半導体膜上には絶縁膜が設けられ、半導体膜のチャネル形成領域となる部分の上方には、絶縁膜を介して走査線と電気的に接続されたゲート電極が設けられ、半導体膜の下部電極となる部分の上方には、絶縁膜を介して保持容量の上部電極が設けられ、半導体膜は、基板に平行であり、ゲート電極は、保持容量の上部電極より半導体膜を基準に高い場所に設けられ、ゲート電極及び上部電極の上方には、信号線が設けられている表示装置。

(もっと読む)

薄膜トランジスタを備えた表示素子及びその製造方法

【課題】工程を単純化することのできる酸化物薄膜トランジスタを備えた表示素子及びその製造方法を提供する。

【解決手段】表示素子は、第1基板120及び第2基板140と、第1基板の画素領域に形成され、ゲート電極121、ゲート絶縁層126、酸化物半導体層122、並びにソース電極123及びドレイン電極124からなる薄膜トランジスタと、第1基板のゲートパッド領域に形成されたゲートパッド118、及び第1基板のデータパッド領域に形成されたデータパッド119と、ゲートパッド領域のゲート絶縁層上に形成され、コンタクトホールを介してゲート電極に接続する金属層155と、第1基板の全体にわたって形成された保護層128と、画素領域の保護層に形成された画素電極と、ゲートパッド領域に形成された第1透明導電層129a及びデータパッド領域に形成された第2透明導電層129bと、基板間に形成された液晶層130とから構成される。

(もっと読む)

半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器

【課題】生産性に優れた半導体装置の製造方法、半導体装置、アクティブマトリクス装置、電気光学装置および電子機器を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板7の一方の面側に、トランジスタ4のゲート絶縁体層44を形成する第1の工程と、ゲート絶縁体層44上に、厚さ方向に貫通する貫通部91を備える絶縁体層9を形成する第2の工程と、貫通部91内の底部付近のゲート絶縁体層44上、および、貫通部91の周囲の絶縁体層9上に、気相成膜法により同時にかつ互いに接触しないようにそれぞれ電極を形成し、ゲート絶縁体層44上に形成された電極を用いて、ゲート電極45を形成するとともに、絶縁体層9上に形成された電極を用いて、画素電極6を形成する第3の工程とを有する。また、平面視で、貫通部91の開口部の縁が、当該貫通部91の底部の縁より内側に位置する。

(もっと読む)

現像液耐性に優れた表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】低温での熱処理を適用した場合でも十分に低い電気抵抗を示すと共に、直接接続された透明画素電極とのコンタクト抵抗が十分に低減され、かつ現像液耐性に優れた表示装置用Al合金膜を提供する。

【解決手段】表示装置の基板上で透明導電膜と直接接続されるAl合金膜であって、上記Al合金膜は、グループAに属するNiおよび/またはCoの元素を2.0原子%以下(0原子%を含まない)、並びにグループBに属する少なくとも一種の元素を0.05〜2.5原子%含み、上記グループBの元素はGd、Nd、La、Y、Sc、Pr、Dy、Ce、Ho、Er、Tb、Pm、Tm、Yb、Lu、Hf、Zr、Zn、Mg、Ti、Mn、およびGeから構成されている。

(もっと読む)

41 - 60 / 232

[ Back to top ]