Fターム[4M104FF21]の内容

Fターム[4M104FF21]の下位に属するFターム

2以上の物質で孔埋め (943)

Fターム[4M104FF21]に分類される特許

61 - 80 / 232

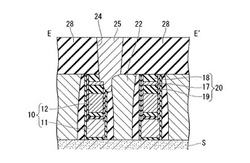

半導体装置の製造方法および半導体装置

【課題】ゲート電極部と容量コンタクトプラグとのショートを防止する。

【解決手段】複数のゲート電極部10と該ゲート電極部10間を接続する配線部との上に、耐エッチング膜17を備えたゲートハードマスク20を形成後、前記配線部上の前記耐エッチング膜17を除去する。これにより、CMP処理を経てコンタクトプラグ22を形成し、さらに、エッチングにより容量コンタクトホール24を開口して容量コンタクトプラグ25を形成した場合に、ゲート電極部10と容量コンタクトプラグ25とのショートを防止することができる。

(もっと読む)

半導体装置とその製造方法、電気光学装置とその製造方法、回路基板とその製造方法、及び電子機器

【課題】フォトリソグラフィー法及びエッチング法を用いることなく導電層間を接続することができる半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、基板上に第1導電層と層間絶縁膜と第2導電層とを順に積層形成する導電層工程と、前記第2導電層の表面から物理的加工を施すことで、前記第2導電層と前記層間絶縁膜とを貫通して前記第1導電層に達する凹部を形成するコンタクトホール形成工程と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体装置

【課題】半導体膜の厚みを適当な範囲に制御することによって、大きいドレイン電流を有するとともに、所望の電気的特性を備える半導体装置を提供する。

【解決手段】半導体装置は、主表面1aを有するガラス基板1と、主表面1a上に設けられ、チャネル領域11と、チャネル領域11の両側に位置するソース領域9およびドレイン領域13とが形成されたポリシリコン膜7と、ポリシリコン膜7に接触するように設けられたゲート絶縁膜17と、ゲート絶縁膜17を介してチャネル領域11に向い合う位置に設けられたゲート電極21とを備える。ポリシリコン膜7は、50nmを超え150nm以下の厚みを有する。ソース領域9およびドレイン領域13は、ポリシリコン膜7の頂面7aからポリシリコン膜7の底面7cにまで達して形成されている。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

薄膜トランジスタの製造方法及び電気光学装置の製造方法

【課題】活性層としてIn−Ga−Zn−O系ホモロガス酸化物半導体を用い、エッチングストッパー層を形成することなく活性層のダメージを抑制するとともに、ソース・ドレイン電極の低抵抗化を図ることが可能な薄膜トランジスタの製造方法及び電気光学装置の製造方法を提供する。

【解決手段】In、Ga、及びZnを含む酸化物半導体膜16を形成する工程と、前記酸化物半導体膜を活性層18にパターン加工する工程と、前記酸化物半導体膜を500℃以上で熱処理する工程と、前記酸化物半導体膜がパターン加工され、かつ、熱処理した活性層を覆うように金属膜を形成する工程と、前記金属膜をエッチングしてパターン加工することにより前記活性層と接触するソース電極20A及びドレイン電極20Bの少なくとも一方を形成する工程と、を含むことを特徴とする薄膜トランジスタの製造方法。

(もっと読む)

高アスペクト比プラグの充填方法

【課題】高アスペクト比を有するプラグを充填する方法を提供する。

【解決手段】高アスペクト比を有するプラグを充填する本発明の方法においては、核形成層を、バイアの側壁上ではなく、バイアの底に形成する。プラグ充填はバイアの底からトップへの方向であり、側壁から内側へではない。得られるプラグは、無ボイドであり、継ぎ目無しである。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】積層構造のゲート電極をもつ薄膜トランジスタにおいて、ゲート電極上の絶縁層のステップカバレージの低下を防止し、かつ、前記第1金属層のヒロック(hillock)の生成を防止する。

【解決手段】基板上に第1金属層43と第2金属層45を連続して蒸着し、さらに所定幅(W1)を持つ感光膜47を形成する(図5(a))。感光膜47をマスクとして第2金属層45を等方性のウェットエッチング方法で感光膜の幅(W1)よりも1μm乃至4μm程度小さな幅(W2)にパターニングする(図5(b))。次に、感光膜47をマスクとして第1金属層43を異方性エッチング方法で幅(W1)を持つようにパターニングして積層構造のゲート電極を形成する(図5(c))。1μm<W1−W2<4μmの関係にあればステップカバレージの低下とヒロックの両方を防止できる。

(もっと読む)

半導体装置

【課題】ゲート電極とのコンタクトのためのコンタクトホールの形成時に、ゲート電極が深く掘り下げられることを防止できる半導体装置を提供すること。

【解決手段】ゲートトレンチ6を有するエピタキシャル層3に、ボディ領域5、ドレイン領域4、ソース領域9およびボディコンタクト領域10を形成する。ゲートトレンチ6には、ゲート電極8を埋設する。エピタキシャル層3には、層間絶縁膜11を積層する。ゲート電極8と層間絶縁膜11との間には、エピタキシャル層3とはエッチングレートの異なる材料からなるエッチングストッパ層14を介在させる。そして、エッチングにより、ゲート電極8およびボディコンタクト領域10それぞれとのコンタクトのための、ゲートコンタクトホール13およびソースコンタクトホール15を同時に形成する。ゲートコンタクトホール13は、平面視でエッチングストッパ層14と重なるように形成する。

(もっと読む)

微細空間への金属充填方法

【課題】空隙やボイドなどを生じることなく、微細空間を硬化金属によって満たし得る方法を提供すること、微細隙間で冷却された硬化金属の凹面化を回避し得る方法を提供すること、及び、工程の簡素化、歩留りの向上などに寄与し得る方法を提供すること。

【解決手段】処理対象である対象物2に存在する微細空間21に溶融金属4を充填し硬化させるに当たって、微細空間21の開口する開口面からその内部に溶融金属4を充填した後、微細空間21内の充填溶融金属41を、大気圧を超える強制外力F1を印加した状態で冷却し硬化させる工程を含む。

(もっと読む)

ジピリジル系レベリング剤によるマイクロエレクトロニクスにおける銅の電子沈積

【課題】半導体集積回路デバイス基板におけるビア構造をメタライズするための方法を提供する。

【解決手段】半導体集積回路デバイス基板は、前面、背面、ビア構造を備え、ビア構造は、基板の前面に開口部、基板の前面を内向きに伸びる側壁部、および底部を備え、前記方法は以下からなる:

半導体集積回路デバイス基板に、(a)銅イオン源、および(b)レベラー化合物からなる電解銅沈積組成物を接触させて、前記レベラー化合物はジピリジル化合物およびアルキル化剤の反応生成物からなり;

電流を電解銅沈積組成物に供給し銅金属をビア構造の底部および側壁部に沈積し、これによって銅充填ビア構造を得る。

(もっと読む)

表示装置用Al合金膜、表示装置およびスパッタリングターゲット

【課題】表示デバイスに用いられる薄膜トランジスタ基板の配線構造において、Al合金膜と透明画素電極を直接コンタクトさせることができるとともに、薄膜トランジスタの製造プロセス中に用いられるアミン系剥離液に対する腐食性を改善できるAl合金膜を開発し、それを備えた表示デバイスを提供する。

【解決手段】Geを0.2〜2.0原子%、および元素群X(Ag、In、Sn、Ni、Co、Cu)より選択される少なくとも1種の元素を含むと共に、希土類元素と高融点金属群(Ti、Ta、V、Nb、Mo、W、Cr、Zr、Hf)からなる元素群Qより選択される少なくとも1種の元素を0.02〜1原子%含み、かつ、粒径が100nmを超える析出物が10−6cm2あたり1個以下であるところに特徴を有するAl合金膜と、該Al合金膜を備えた表示装置。

(もっと読む)

Ti膜の成膜方法および成膜装置、ならびに記憶媒体

【課題】CVDによりTi膜を成膜する際に、より低抵抗でかつ抵抗のばらつきが小さいTi膜を成膜することができ、プラズマダメージを小さくすることができるTi膜の成膜方法を提供すること。

【解決手段】チャンバ内にシリコンウエハを配置し、TiCl4ガスおよびH2ガスを含む処理ガスを導入しつつチャンバ内にプラズマを生成し、そのプラズマにより処理ガスの反応を促進してシリコンウエハ上にTi膜を成膜するにあたり、チャンバ内にシリコンウエハが配置された状態でTiCl4ガスを導入した後、チャンバ内にプラズマを生成する。

(もっと読む)

半導体装置の製造方法

【課題】容易にコンタクト抵抗を低減することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に多結晶シリコン膜を形成し、その後、この多結晶シリコン膜の表面をエッチングする。そして、エッチングされた多結晶シリコン膜をシリサイド化して、シリサイド膜12を形成する。更に、シリサイド膜12に接するプラグ23s、23d及び23gを層間絶縁膜21内に形成する。

(もっと読む)

半導体装置およびフォトマスク

【課題】シェアードコンタクトホールの開口不良を抑制できる半導体装置およびフォトマスクを提供する。

【解決手段】シェアードコンタクトホールSC1、SC2は、ゲート電極層GE1、GE2とドレイン領域PIRとの双方に達している。平面視において、ゲート電極層GE1、GE2の一方側壁E2が、一方側壁E1の仮想延長線E1aよりも他方側壁E4側にずれて位置している。平面視において、ゲート電極層GE1、GE2のシェアードコンタクトホールSC1、SC2が達する部分の線幅D1の中心線(C2−C2)が、ゲート電極層GE1、GE2のチャネル形成領域CHN1、CHN2上に位置する部分の線幅D2の中心線(C1−C1)に対してずれて位置している。

(もっと読む)

半導体装置

【課題】 2層の電極構造を有するディスクリート型バイポーラトランジスタでは、2層目のベース電極下方に1層目のエミッタ電極およびベース電極が配置される。1層目の電極は2層目の電極よりその厚みが薄く、第2ベース電極下方の動作領域(エミッタ領域)から1層目のエミッタ電極を経由して、2層目のエミッタ電極へ流れる電流経路は、ほぼ真上に電流が引き上げられる第2エミッタ電極下方の電流経路と比べて抵抗が高くなり、チップ内の電流密度が不均一になる問題があった。

【解決手段】 第1ベース電極および第1エミッタ電極を全て短冊状に形成し、交互に平行して配置し、第2エミッタ電極の面積を第2ベース電極の面積より拡張する。これにより、エミッタ領域から第1エミッタ電極を介して第2エミッタ電極まで略真上に引き上げられる電流経路が増加するので、チップ全体の電流密度が不均一になることを回避できる。

(もっと読む)

半導体装置

【課題】 構造を複雑化させることなく、サージ電流によるスイッチング素子の破壊を抑制することのできる半導体装置を提供すること。

【解決手段】 半導体装置1において、活性層5に第1ディープトレンチ6を形成する。アクティブ領域9には、ボディ領域11とドリフト領域12とを形成する。ボディ領域11の表層部には、ソース領域13を形成する。ドリフト領域12の表層部には、ドレイン領域15を形成する。また、フィールド領域10には、第2ディープトレンチ20を形成する。第2ディープトレンチ20の内側面を1対のシリコン酸化膜21で被覆し、その内部をポリシリコン22で埋め尽くす。そして、第1、第2ディープトレンチ6,20間の第1半導体領域23をソース領域13に電気的に接続する。また、第2ディープトレンチ20外の第2半導体領域28をドレイン領域15に電気的に接続する。

(もっと読む)

半導体装置およびその製造方法

【課題】非対称トランジスタの接合リークを抑制する。

【解決手段】半導体装置100は、シリコン基板101の上部に設けられたゲート電極115と、ゲート電極115の異なる側方においてシリコン基板101に設けられた第一不純物拡散領域103および第二不純物拡散領域105とを有するMOSFET110を含む。MOSFET110は、第一不純物拡散領域103の上部にエクステンション領域107を有するとともに第二不純物拡散領域105の上部にエクステンション領域107を有さず、第一不純物拡散領域103上に第一シリサイド層109を有するとともに、ゲート電極115側端部の近傍において第二不純物拡散領域105上にシリサイド層を有しない。

(もっと読む)

半導体素子の製造方法

【課題】半導体基板の損傷を最大限抑制して素子の漏洩電流発生が防止できる半導体素子の製造方法を提供する。

【解決手段】第1のコンタクトホールと、無結晶のポリシリコン膜及びPMD膜26を順次に形成してイオンを注入した後、金属配線を形成することによって、第1のコンタクトホールを用いてコーディングするので、その他のコーディング領域が別に必要でなくチップ面積を縮小することができ、PMDの蒸着前に第1のコンタクトホールを形成するので、半導体基板20の損傷を減らして漏洩電流が減少し、通常のROMコーディングとは反対にOFF特性で反対タイプのイオン注入によりON特性を有するようにし、金属配線の蒸着時に金属配線層の下部にポリシリコン膜が形成されて金属配線の断絶が最小化できる。

(もっと読む)

61 - 80 / 232

[ Back to top ]