Fターム[4M104FF21]の内容

Fターム[4M104FF21]の下位に属するFターム

2以上の物質で孔埋め (943)

Fターム[4M104FF21]に分類される特許

81 - 100 / 232

パターン形成方法

【課題】煩雑な工程を要せずに、アスペクト比の高い所望の形状のパターンを形成することのできるパターン形成方法、このパターン形成方法を用いた電子装置または光学装置の製造方法、並びに、このパターン形成方法を用いた電子装置または光学装置の製造装置を提供する。

【解決手段】誘電率及び/又は磁化率が異なる2以上の物質からなるネガパターンに電場及び/又は磁場を印加して電気力線及び/又は磁力線の疎密差を前記ネガパターンの近傍に発生させ、前記電気力線及び/又は磁力線の疎密差に沿って少なくとも1以上の流動性のある物質を移動させて所望のポジパターンを形成する方法であって、前記ネガパターンの内部に前記流動性のある物質の少なくとも一部が進入することでポジパターンを形成し、その後少なくとも1以上の流動性のある物質の少なくとも一部を固化形成する。

(もっと読む)

積層トレンチコンタクトを形成する方法および当該方法によって形成される構造

【解決手段】 マイクロ電子デバイスを形成する方法および対応して形成される構造を説明する。当該方法は、基板のソース/ドレインコンタクト上に配設されている第1のコンタクト金属と、第1のコンタクト金属の上面に配設されている第2のコンタクト金属とを含む構造を形成する段階を備えるとしてよい。第2のコンタクト金属は、基板上に配設されている金属ゲートの上面に配設されているILDの内部に配設されている。 (もっと読む)

半導体装置の製造方法

【課題】縦型炉を使った半導体装置の製造において、シリコンウェハ裏面を保護することで、工程中でのウェハの汚染を抑制し、又ウェハのデチャックを容易にする。

【解決手段】シリコン基板の一の面は半導体素子を形成するものである。他の面に酸化膜を形成する工程と、第1の膜を、一の面を覆うように、また他の面の酸化膜を覆うように成膜する工程と、第1の膜を、パターニングし、マスクパターンを形成する工程と、一の面に、素子分離領域を形成する工程と、他の面において、第1の膜を除去する工程と、一の面においてゲート絶縁膜28Gを形成する工程と、一の面においてゲート絶縁膜28Gを介してゲート電極29Gを形成する工程と、ゲート電極29Gの両側にソース・ドレイン領域21c,21dを形成し、トランジスタを形成する工程と、他の面に前記酸化膜を維持したまま、半導体基板上方に配線層を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】ソース/ドレイン拡散層に形成されるシリサイド層のスパイクやコンタクトの突き抜けを抑制して、接合リークの発生を低減するとともに、シリサイド層を低抵抗化した半導体装置およびその製造方法を提供する。

【解決手段】半導体装置1は、半導体基板10の上に形成されたトランジスタを有する。トランジスタのゲート電極は、ポリシリコン電極14とその上に形成されたシリサイド層32から構成される。さらに、低濃度ドーピング領域16、高濃度ドーピング領域からなるソース/ドレイン拡散層20、ソース/ドレイン拡散層20上のシリサイド層30を備える。シリサイド層30の表面は、半導体基板10の表面よりも上方に位置している。また、シリサイド層30はシリサイド化反応抑制金属を含み、シリサイド層30の表面から所定の深さに至る領域において、シリサイド層30の表面から基板側へ向かってシリサイド化反応抑制金属の濃度が高くなる濃度プロファイルを有する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】 簡便に形成可能であり、リーク電流の発生を抑制できる薄膜トランジスタ及び薄膜トランジスタの製造方法を提供する。

【解決手段】 薄膜トランジスタ22は、ソース領域及びドレイン領域の一方である第1領域と、他方である第2領域と、を有した半導体層25と、ゲート絶縁層27と、ゲート絶縁層上に形成され、第1領域から外れて位置し、第2領域に重ねられた開口部30aを有した環状のゲート電極30と、層間絶縁膜31と、半導体層の第1領域に接続された第1電極と、半導体層の第2領域に接続された第2電極と、を備えている。

(もっと読む)

無電解めっき方法

【課題】絶縁体又は半導体の表面に、超臨界流体又は亜臨界流体を使用するとともに誘導共析現象を利用して短時間で厚いめっき層を無電解めっきで得られるようにした無電解めっき方法を提供すること。

【解決手段】絶縁体としてのガラス基板試料22の表面に無電解めっきする際に、無電解めっき液19中に金属粉末を分散させた状態で超臨界流体ないしは亜臨界流体を使用して無電解めっきを行う。そうすると、誘導共析現象を利用して短時間で均質な厚いめっき層が得られる。本発明の無電解めっき方法では、金属粉末として平均粒径は1nm以上100μm以下のものを使用でき、半導体素子内の微細金属配線形成方法であるダマシン法ないしデュアルダマシン法にも適用可能である。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

水性酸浴および銅を電解析出するための方法

特に、ブラインドマイクロビア(BMV)およびトレンチにおいて非常に均一な銅析出を生成させるために、銅を電解析出するための水性酸浴が提供され、前記浴は、少なくとも1種の銅イオン源、少なくとも1種の酸イオン源、少なくとも1種の光沢剤化合物および少なくとも1種のレベラー化合物を含み、少なくとも1種のレベラー化合物は、合成によって製造される非官能基化ペプチドおよび合成によって製造される官能基化ペプチドおよび合成によって製造される官能基化アミノ酸を含む群から選択される。  (もっと読む)

(もっと読む)

貴金属膜の成膜装置及び貴金属膜の成膜方法

【課題】基板に形成されたホールの内部にスパッタリングにより成膜した貴金属膜の厚みを、ホールの両サイドで対称なものとすることができ、したがって、貴金属膜に断線等の不具合が生じる虞がなく、信頼性をより向上させることができる貴金属膜の成膜装置及び貴金属膜の成膜方法を提供する。

【解決手段】本発明の貴金属膜の成膜装置は、基板23に形成されたホールの内部に貴金属膜をスパッタリングにより成膜する装置であり、ターゲット24と、このターゲット24に対向配置されるステージ22と、ターゲット24にスパッタリング電力Pt(W)を印加する電源26とを備え、ターゲットの直径Tと、ターゲット24とステージ22上の基板23との距離Lとの比L/Tを、0.5以上かつ1.5以下の範囲で変更可能とした。

(もっと読む)

半導体装置の製造方法および半導体製造装置

【課題】半導体装置におけるナノスケールの微細構造物を用いた配線部分に金属をボイドなく埋め込み、電気的な不良を抑制して半導体装置の歩留りを向上させる。

【解決手段】半導体基板上に形成された絶縁膜に設けられたヴィアホール又はトレンチに金属めっき膜を埋め込む工程において、まず、最初のめっき液の容積、補充しためっき液量、処理したウェーハ枚数、流した電流値及び排出しためっき液量の各データを収集する。次いで、取得した電流値に基づいてめっき処理の累積電荷量を算出する。また、全めっき液の容積を算出する。そして、取得した、全めっき液の容積、排出しためっき液量および累積電荷量に基づいて、めっき液に含まれる抑制剤の分解物量を算出する。分解物量が予め設定された閾値以下である場合にのみ半導体基板のめっき処理を実施する。

(もっと読む)

ナノ構造処理のための導電性補助層の形成及び選択的除去

一又は複数のナノ構造の作成方法が開示されており、当該方法は:基板の上部表面上に導電層を形成すること;導電層上に触媒のパターン層を形成すること;触媒層上に一又は複数のナノ構造を成長させること;及び一又は複数のナノ構造の間及び周囲の導電層を選択的に除去することを含んでなる。デバイスもまた開示されており、該デバイスは、基板、ここで基板は一又は複数の絶縁領域によって隔てられた一又は複数の露出金属島を含んでなる;一又は複数の露出金属島又は絶縁領域の少なくともいくつかを覆う基板上に配された導電性補助層;導電性補助層上に配された触媒層;及び触媒層上に配された一又は複数のナノ構造を含んでなる。 (もっと読む)

半導体装置の製造方法

【課題】デュアルストレスライナを介して開口部を形成する際に、オーバーエッチングよるダメージの影響を少なくして製造歩留まりを向上させる。

【解決手段】基板100にNFET101、PFET103、及び配線102を形成し、全面に伸張応力誘起層105を形成し、NFET101上に伸張応力誘起層105が残るようにエッチングし、全面に圧縮応力誘起層301を形成し、PFET103上及び配線上102の圧縮応力誘起層301の厚さを部分的に減少させ、全面に絶縁膜502を形成し、絶縁膜502、伸張応力誘起層105、及び圧縮応力誘起層301をエッチングして、NFET101、PFET103、及び配線102に通じる開口部501を形成する。

(もっと読む)

エッチング方法及び半導体装置の製造方法

【課題】白金族の膜を加工性良く安価にエッチングできるエッチング方法及び半導体装置の製造方法を提供する。

【解決手段】過マンガン酸塩を含む、pHが12.6〜15.8の溶液で、白金族の膜をエッチングすることを特徴とするエッチング方法が提供される。

(もっと読む)

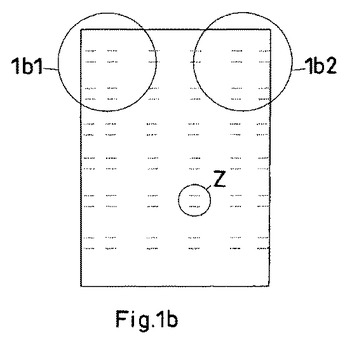

パワーMOSトランジスタ

【課題】 エレクトロマイグレーションの制約を受け難く、配線抵抗が小さくトランジスタの電力損失が少ない、パッド配置の制約の少ないパワーMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成されたソース領域2およびドレイン領域3が格子状に形成されたゲート4を挟んで互いに隣接するMOSトランジスタにおいて、半導体基板1上に順次形成された3層のメタル配線5、6、7とを有する。メタル配線は、ソース領域及びドレイン領域に電気的に接続され、ドレイン領域を第3層メタル配線7に接続する場合、ソース領域を第2層メタル配線6及び第1層メタル配線5に接続する。第3層メタル配線7のドレイン配線は、半導体基板1の全領域を覆うように配置され、第1層及び第2層メタル配線5、6のソース配線は第1層及び第2層メタル配線の全領域を覆うように配置される。

(もっと読む)

スパッタリング装置

【課題】傾斜したマルチカソードの各々でスパッタされた中性原子を用いることでウェハー表面のパターン化された孔または溝でより良い側壁および底部のカバレッジを形成できるスパッタリング装置を提供する。

【解決手段】ウェハーホルダ12がその中心軸周りに回転するようにされて底壁に設けられ、かつウェハーホルダ上に配置されたウェハーに対して少なくとも2つの傾斜されたカソード11a〜11dが上壁に設けられる反応容器10を備え、カソードの各々はrf発生器から整合回路を介してrf電流が供給され、ガス導入部とガス排出部を含む圧力制御機構を備える。

(もっと読む)

半導体装置および、その製造方法

【課題】LDDサイドウォール形成時に、NMOS/PMOS境界領域の2重エッチングによる不具合を克服する。

【解決手段】NMOS/PMOS境界領域にゲートレベル配線を形成し、LDDサイドウォール形成時に2重エッチングされるゲートレベル配線の最上層に、サイドウォール絶縁膜層とエッチング選択比のとれる膜107をハードマスクとして形成しておくことで、ゲートレベル配線に接続するプラグコンタクト112形成時にゲート電極のオーバーエッチによる堆積物の付着を防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】ソースドレイン領域のサイズが増大することがない局所配線構造を備えた半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成されたゲート電極22及び半導体基板11におけるゲート電極22の両側方にそれぞれ形成された第1のソースドレイン領域29A及び第2のソースドレイン領域29Bを有するトランジスタ12と、半導体基板11の上における第1のソースドレイン領域29Aを挟んでゲート電極22と反対側に形成されたゲート配線42と、ゲート配線42と第1のソースドレイン領域29Aとを接続する局所配線構造60とを備えている。局所配線構造60は、第1のソースドレイン領域29A及びゲート配線42の上面に跨って形成されたSiGe層61によって構成されている。

(もっと読む)

素子の接合構造

【課題】アモルファスSi−TFTに関し、Al−Ni系合金からなる電極配線層を半導体層に直接接合可能とする素子の接合技術を提供する。

【解決手段】本発明は、半導体層とAl−Ni系合金からなる電極配線層と透明電極層とを備え、前記半導体層と前記電極配線層とが直接接合された部分を有する素子の接合構造において、電極配線層に直接接合された半導体層は、1.0×1021atoms/cm3〜1.0×1022atoms/cm3のリンと、5×1017atoms/cm3〜1×1021atoms/cm3の窒素を含有したアモルファスSiであることを特徴とする。

(もっと読む)

半導体装置、電気光学装置、電子機器、半導体装置の製造方法及び電気光学装置の製造方法

【課題】半導体装置の特性の向上、特に、配線の低抵抗化、また、配線材料の半導体装置を構成する半導体層への拡散の低減を図る。

【解決手段】半導体装置を、基板上に形成された半導体膜(13)と、半導体膜上にゲート絶縁膜を介して形成され、第1導電性材料よりなるゲート電極部(G)と、ゲート電極部と同一層に、ゲート電極部と電気的に接続されるよう配置され、前記前記第1導電性材料とは異なる第2導電性材料を含有する配線部(GL)と、を有するよう構成する。ゲート電極部と配線部とを異なる材料で構成することで、ゲート電極部および配線部の構成材料を最適化できる。例えば、チャネル領域上のゲート電極(G)部を拡散し難いNi配線で構成し、チャネル領域とは重ならないゲート配線(GL)部は、抵抗の低いAg配線を用い、配線の低抵抗化を図る。

(もっと読む)

半導体装置、半導体装置の製造方法および電気光学装置

【課題】ゲート電極の形状を改良して、インパクトイオン化の原因となるドレイン端での電界集中を防止可能な薄膜トランジスタを備えた半導体装置、この半導体装置の製造方法、および当該半導体装置を素子基板として用いた電気光学装置を提供すること。

【解決手段】半導体装置10xの薄膜トランジスタ30nにおいて、ゲート電極3nは、その表面を酸化してなるシリコン酸化膜3sにより覆われて、エッジ部分3w、3x、3y、3zが丸みを有しているため、ゲート電極3nには、電界の集中するエッジ部分がない。このため、ゲート電極3nのエッジ部分に対してゲート絶縁層2を介して対向するチャネル領域130nのドレイン端では、電界が集中しないので、インパクトイオン化が発生しにくい。それ故、下地絶縁層12上に形成された薄膜トランジスタ30nであっても、良好な電流−ゲート電圧特性を有する。

(もっと読む)

81 - 100 / 232

[ Back to top ]