Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

581 - 590 / 590

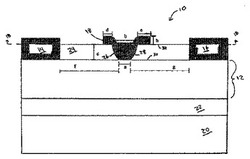

ナノワイヤ半導体デバイス

半導体デバイスはナノワイヤ(16)を使用して製造される。ナノワイヤ(16)に沿う伝導を制御するために導電ゲート(22)が使用されても良い。この場合、一方の接点がドレイン(12)であり、他方がソース(18)である。ナノワイヤ(16)は、基板(2)中の或いは特に基板(2)上の表面層(3)中のトレンチまたは貫通穴(8)内で成長されても良い。ゲート(22)はナノワイヤ(16)の一端にだけ設けられても良い。ナノワイヤ(16)は、その全長にわたって同じ材料から成ることができ、あるいは、異なる材料を使用することができ、特に、ゲート(22)の近傍およびゲート(22)とトレンチの底部との間で異なる材料を使用できる。  (もっと読む)

(もっと読む)

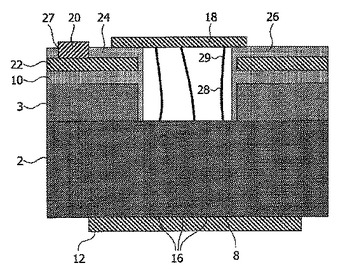

半導体構造(調整可能半導体デバイス)

【課題】下方に配置された基板とは異なる極性を有する不連続な非平面状サブコレクタを含む半導体構造を形成する方法を提供する。

【解決手段】この構造は、サブコレクタの上方の活性領域(コレクタ)、活性領域の上方のベース、およびベースの上方のエミッタを含む。不連続なサブコレクタの不連続部分間の距離は、半導体構造の動作特性を調整する。調整可能な動作特性は、絶縁破壊電圧、電流利得遮断周波数、電力利得遮断周波数、通過周波数、電流密度、静電容量範囲、ノイズ注入、少数キャリヤ注入、ならびにトリガ電圧および保持電圧を含む。

(もっと読む)

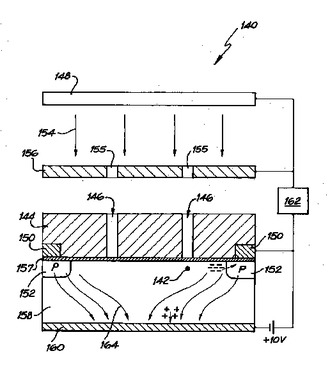

注入され計数されたドーパントイオン

本発明は、実質的に真性な半導体の基板(158)の領域に注入された、計数された数のドーパントイオン(142)を有する汎用タイプの半導体装置に関する。基板(158)の一つ以上のドープされた表面領域は、金属化され、電極(150)が形成される。計数された数のドーパントイオン(142)が、実質的に真性な半導体の領域に注入される。

【その他】

原文には、請求項11及び請求項11Aが存在する。請求項11Aは、オンライン手続上、請求項11内に記載した。

(もっと読む)

(もっと読む)

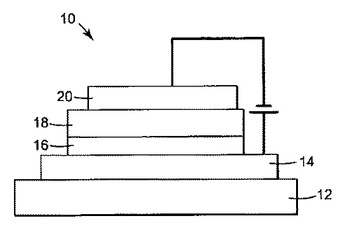

真性半導体とオーミック接触部の間にPドープ半導体を備えた有機ショットキーダイオード

有機ショットキーダイオードは多結晶有機半導体層を含み、その層の一方の側面に整流接触部を有する。上記多結晶有機半導体層のもう一方の側面に非晶質のドープ半導体層が配置され、これが上記半導体層とオーミック接触層の間のバッファとして働く。  (もっと読む)

(もっと読む)

ドープされたゲート誘電体を有するトランジスタ

トランジスタおよびその製造方法。ゲート誘電体材料を堆積する前に半導体基材をドープする。別個のアニール工程、または、トランジスタを製造するために使用される後続のアニール工程の間を用いて、ドーパント種を、基材のドープされた領域から、ゲート誘電体内に出力拡散して、ドープされたゲート誘電体を生成する。ドーパント種は、ゲート誘電体の原子構造における各空孔を埋め、その結果、トランジスタの動作速度が上昇し、電力消費が低減され、電圧安定性が改善される。  (もっと読む)

(もっと読む)

電極規定層を包含する窒化ガリウム材料デバイスおよびその形成方法

窒化ガリウム材料デバイスおよびその形成方法を提供する。該デバイスは、電極規定層を包含する。電極規定層は典型的にはその内部に形成されたビアを有し、該ビア内に電極が(少なくとも部分的に)形成される。したがって、ビアは、電極の寸法を(少なくとも部分的に)規定する。いくつかの場合において、電極規定層は、窒化ガリウム材料領域上に形成された不動態化層である。 (もっと読む)

モノリシック集積型エンハンスメントモードおよびデプリーションモードFETおよびその製造方法

【課題】 製造コストを低減し品質の均一性および安定性を高めたモノリシック集積型エンハンスメントモード/デプリーションモードFETデバイスを提供する。

【解決手段】 単一の半導体多層構造でデプリーションモード(Dモード)FETをエンハンスメントモード(Eモード)FETとモノリシックに集積回路化する。上記多層構造にはチャネル層を設け、その上に障壁層をオーバーレイし、さらにその上にオームコンタクト層をオーバーレイする。これらDモードFETおよびEモードFETのソースコンタクトおよびドレーンコンタクトをオームコンタクト層に接続する。またDモードFETおよびEモードFETのゲートコンタクトを障壁層に接続する。障壁層の中のEモードゲートコンタクトの下に非晶質化領域を設ける。この非晶質化領域が障壁層との間の埋込みEモードSchottkyコンタクトを構成する。代わりに実施例ではDモードFETのゲートコンタクトを障壁層にオーバーレイした第1の層に接続し、その第1の層の中にDモード非晶質化領域を形成する。

(もっと読む)

PN接合ダイオード装置及びその製造方法

【課題】より小型が可能なPN接合ダイオード装置及びその製造方法を提供することにある。

【解決手段】PN接合ダイオードのカソード電極22及びアノード電極23を共に、シリコン基板10の一方の主面に形成することにより、カソード電極22及びアノード電極23とをリードフレーム26に、ワイヤー等で接続することなく、接着することを可能にする。

(もっと読む)

半導体装置およびその製造方法

【課題】SiC基板を用い、オン抵抗のさらなる低減が図られた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、研磨等により厚さが200μm以下にされ、( 0 0 0−1)C面を上面とするSiC基板11aと、SiC基板11aの上面上に順に設けられた半導体からなるエピタキシャル成長層12,ショットキー電極14及び上部電極16と、Si面であるSiC基板11aの裏面上に順に設けられたオーミック電極15及び下部電極17とを備えている。SiC基板11aが従来の基板よりも薄いため、動作時のオン抵抗が大きく低減されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

581 - 590 / 590

[ Back to top ]