Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

81 - 100 / 590

半導体装置およびその製造方法

【課題】 高周波特性を確保し、サイズを小型化し、かつ製造が容易な、正孔の蓄積を解消できる、耐圧性に優れた、半導体装置等を提供する。

【解決手段】 ヘテロ接合電界効果トランジスタ(HFET:Hetero-junction Field Effect Transistor)であって、非導電性基板1上に位置する、チャネルとなる二次元電子ガス(2DEG:2 Dimensional Electron Gas)を形成する再成長層7(5,6)と、再成長層に接して位置する、ソース電極11、ゲート電極13およびドレイン電極15を備え、ソース電極11が、ゲート電極13に比べて、非導電性基板1から遠い位置に位置することを特徴とする。

(もっと読む)

半導体装置

【課題】記憶内容に対する保持特性の改善を図ることが可能な半導体装置を提供する。また、半導体装置における消費電力の低減を図る。

【解決手段】チャネル形成領域に、トランジスタのオフ電流を十分に小さくすることができるワイドギャップ半導体材料(例えば、酸化物半導体材料)を用い、且つ、ゲート電極用のトレンチと、素子分離用のトレンチを有するトレンチ構造のトランジスタとする。トランジスタのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわたって情報を保持することが可能となる。また、ゲート電極用のトレンチを有することで、ソース電極とドレイン電極との距離を狭くしても該トレンチの深さを適宜設定することで、短チャネル効果の発現を抑制することができる。

(もっと読む)

窒化物系半導体デバイス及びその製造方法

【課題】大電流かつ高耐圧な窒化物系半導体デバイスを提供する。

【解決手段】基板10と、基板10の上方に形成された電子走行層30と、電子走行層30上に形成された、電子走行層30とバンドギャップエネルギーの異なる電子供給層40と、電子供給層40上に形成されたドレイン電極80と、ドレイン電極80に流れる電流を制御するゲート電極70と、ゲート電極70をはさんでドレイン電極80の反対側に形成されたソース電極90とを備え、ゲート電極70とドレイン電極80との間の電子走行層30の表面には、2次元電子ガスの濃度が他の領域より低い複数の低濃度領域32が、互いに離れて形成されている、窒化物系半導体デバイス100。

(もっと読む)

半導体装置

【課題】リーク電流を抑制した半導体装置を提供する。

【解決手段】一態様に係る半導体装置は、第1導電型の半導体層、複数のトレンチ、絶縁層、導電層、第1半導体拡散層、及びアノード電極を有する。半導体層は、半導体基板上に形成され第1の不純物濃度よりも小さい第2の不純物濃度を有する。複数のトレンチは、半導体層の上面から下方に延びるように半導体層中に形成されている。導電層は、絶縁層を介してトレンチを埋めるように形成され且つ半導体層の上面から第1の位置まで下方に延びる。第1半導体拡散層は、複数のトレンチの間に位置する半導体層の上面から第2の位置に達し且つ第2の不純物濃度より小さい第3の不純物濃度を有する。アノード電極は、第1半導体拡散層とショットキー接合されている。半導体層の上面から第2の位置までの長さは、半導体層の上面から第1の位置までの長さの1/2以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】素子面積を増加させずに順電圧降下を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1半導体領域と、第1電極と、第2半導体領域と、絶縁領域と、第2電極と、を備える。第1半導体領域は、第1部分と、第1主面上において第1主面に直交する第1方向に延在した第2部分と、を有する第1導電形の半導体領域である。第1電極は、第2部分と対向して設けられた金属領域である第3部分と、第3部分と、第2部分と、をむすぶ第2方向に延在し、かつ第1方向に延在する第4部分と、を有する。第2半導体領域は、第2部分と、第3部分と、のあいだに設けられ、第1半導体領域よりも不純物濃度の低い第1濃度領域を有し、第3部分とショットキー接合した第1導電形の半導体領域である。絶縁領域は、第4部分と、第2半導体領域と、のあいだに設けられる。第2電極は、第1部分と導通する。

(もっと読む)

半導体素子及び半導体素子形成方法

【課題】ゲルマニウムをチャネル材料とする金属/ゲルマニウムからなるソース/ドレイン構造を有する半導体素子を提供する。

【解決手段】半導体と金属とが接合してソース/ドレイン構造を形成する半導体素子において、ゲルマニウム(Ge)を3価元素(又は5価元素)でドーピングしたp型ゲルマニウム(又はn型ゲルマニウム)をチャネル2の材料とし、当該p型ゲルマニウム(又はn型ゲルマニウム)の任意の結晶面における原子配置と同一の原子配置である結晶面を有する金属3を、前記同一の原子配置である結晶面で接合して界面を形成し、当該形成された界面を用いたソース/ドレイン構造を有する。

(もっと読む)

半導体装置

【課題】順方向電圧の低減及びリーク電流の低減を図る半導体装置を提供する。

【解決手段】本実施形態に係る半導体装置は、第1導電形の第1半導体層と、第2導電形の領域であって、前記第1半導体層の第1主面の側に離間して設けられた複数の第2半導体領域と、第2導電形の領域であって、前記第1半導体層の前記第1主面の側に前記複数の第2半導体領域を囲むように設けられた第3半導体領域と、前記第1半導体層及び前記複数の第2半導体領域の上に設けられた第1電極と、を備える。前記第1半導体層は、第1部分と、前記第1部分よりも比抵抗が低く、前記第1部分と前記第1主面とのあいだであって、前記複数の第2半導体領域のあいだ、及び前記第3半導体領域の外側に設けられた第2部分と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗が低く、高いアバランシェ耐量を有する半導体装置およびその製造方法を提供することである。

【解決手段】実施形態の半導体装置は、第1半導体層と、複数のベース領域と、ソース領域と、トレンチ内に、ゲート絶縁膜を介して設けられたゲート電極と、トレンチ内において、ゲート電極の下にフィールドプレート絶縁膜を介して設けられたフィールドプレート電極と、第1主電極と、第2主電極と、を備える。フィールドプレート絶縁膜の一部の厚さは、ゲート絶縁膜の厚さよりも厚く、一対のトレンチ内に設けられたフィールドプレート絶縁膜の一部どうしの間の第1半導体層の幅は、一対のトレンチ内に設けられたゲート絶縁膜どうしの間のベース領域の幅よりも狭く、第1半導体層と、フィールドプレート絶縁膜の一部と、の界面の直上には、ソース領域が形成されていない。

(もっと読む)

ショットキーバリアダイオード

【課題】ジャンクションバリアショットキー構造をもつダイオードにおいて、ショットキー接合部の逆サージ耐量を改善することが可能なショットキーバリアダイオードを提供する。

【解決手段】ガードリング層15に隣接した第二半導体層161と、この第二半導体層161に隣接する第二半導体層162との間に跨るように、基板11の中心領域Acにおいて第三絶縁層23が形成されている。即ち、第二半導体層161と第二半導体層162との間で、基板11の一面(一方の主面)11aに露呈された第一半導体層13を覆うように第三絶縁層23が形成される。これによって、第三絶縁層23は、第二半導体層161と第二半導体層162との間で基板11の一面11aに露呈された第一半導体層13と、金属層14との間を電気的に絶縁する。

(もっと読む)

高耐圧半導体装置

【課題】高耐圧半導体装置の大型化を招くことなく、従来の高耐圧半導体装置900の場合よりも「気中放電による逆耐圧の低下」を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタルからなる第1電極層層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118と、半導体層110の表面上において第1電極層128を取り囲む領域に形成された絶縁層124とを備え、第2ガードリング層118が絶縁層124の外周近傍まで形成されている高耐圧半導体装置100。

(もっと読む)

窒化ガリウム半導体素子

【課題】高出力の窒化ガリウムショットキー・ダイオード素子を提供する。

【解決手段】1〜6μmの厚さを有するn+型ドープしたGaNダイオードから製造した窒化ガリウムベースの半導体ショットキー・ダイオードをサファイア基板の上に配設する。1μmを超える厚さを有するn−型ドープしたGaNダイオードを、複数の細長形の指にパターン化した前記n+型ドープGaNダイオード上に配設し、金属層をn−型ドープGaN層上に配設し、それとの間にショットキー接合を形成する。細長形の指の層厚、長さおよび幅は、降伏電圧が500Vを超え、電流容量が1アンペアを超え、かつ順方向電圧が3V未満である素子を得るように最適化される。

(もっと読む)

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

窒化物半導体ダイオード

【課題】 従来と同じチップ面積でありながら従来よりも素子抵抗が低く、順方向電流が大きくとれる窒化物半導体ダイオードを提供する。

【解決手段】 窒化物半導体上のショットキー電極形成領域において、ショットキー電極と窒化物半導体層の表面とが接する境界の長さの合計が、前記ショットキー電極形成領域の外周長よりも長くなるように形成する。また、10倍長いことが望ましい。例えば、ショットキー電極を同心環状とすることで、上記課題を解決することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキーバリアダイオードの逆リーク電流を低減させる。

【解決手段】禁制帯幅の異なるGaN膜3a、3bとバリア膜4a、4bとを交互に積層して形成したヘテロ接合体5a、5bを有する積層体6と、積層体6の一方の側壁にショットキー接続された第1電極8と、もう一方の側壁に接して形成された第2電極10とを有する半導体装置において、第1電極8とバリア膜4a、4bとの間に酸化膜12を設ける。これにより、バリア膜4a、4bの加工に起因してバリア膜4a、4bに残留する欠陥にを介して逆リーク電流が流れることを防ぐ。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】オン電流を確保しつつ、オフ電流を低減した薄膜トランジスタを有する表示装置を提供することを目的とする。

【解決手段】ゲート電極GTと、ゲート電極GTの上側に形成される結晶化された第1の半導体層MSと、第1の半導体層MSの上側に形成される、ソース電極STおよびドレイン電極DTと、第1の半導体層MSの側方から延伸して、ソース電極ST及びドレイン電極DTのうちの一方と第1の半導体層MSとの間に介在する第2の半導体層SLと、を有する表示装置であって、第2の半導体層SLは、第1の半導体層MSと接触して結晶化されて形成される第1部分SLaと、第1部分SLaよりも結晶性が低い第2部分SLbを有する、ことを特徴とする表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ボディ浮遊効果を抑制することが可能な半導体装置及びその製造方法を提供する。

【解決手段】シリコン基板1と、シリコン基板1上に形成された埋め込み絶縁層2と、埋め込み絶縁層2上に形成された半導体層3とを備えるSOI構造の半導体装置であって、半導体層3は、第1導電型のボディ領域4、第2導電型のソース領域5及び第2導電型のドレイン領域6を有し、ソース領域5とドレイン領域6との間のボディ領域4上にゲート酸化膜7を介してゲート電極8が形成され、ソース領域5は、第2導電型のエクステンション層52と、エクステンション層52と側面で接するシリサイド層51を備え、シリサイド層51とボディ領域4との境界部分に生じる空乏層の領域に結晶欠陥領域12が形成されている。

(もっと読む)

半導体整流装置

【課題】少数キャリアが注入される電圧を低下させ、十分なサージ電流耐性を有するワイドバンドギャップ半導体を用いた半導体整流装置を提供する。

【解決手段】ワイドギャップ半導体の第1導電型の半導体基板と、半導体基板の上面に形成され、半導体基板より低不純物濃度のワイドギャップ半導体の第1導電型の半導体層と、半導体層表面に形成されるワイドギャップ半導体の第1導電型の第1の半導体領域と、第1の半導体領域の周囲に形成されるワイドギャップ半導体の第2導電型の第2の半導体領域と、第1の半導体領域に挟まれ、接合深さが第2の半導体領域の接合深さよりも深いワイドギャップ半導体の第2導電型の第3の半導体領域と、第1、第2および第3の半導体領域上に形成される第1の電極と、半導体基板の下面に形成される第2の電極と、を備えることを特徴とする半導体整流装置。

(もっと読む)

半導体装置の製造方法

【課題】信頼性と電気的特性の確保を両立した半導体装置を提供する。

【解決手段】同一の半導体基板1上に形成されたパワーMOSFETと保護回路を備える。パワーMOSFETがトレンチゲート縦型PチャネルMOSFETであって、そのゲート電極6の導電型をP型とする。また、保護回路がプレーナゲート横型オフセットPチャネルMOSFETを備え、そのゲート電極10の導電型をN型とする。これらゲート電極6とゲート電極10は別工程で形成される。

(もっと読む)

ドリフト領域とドリフト制御領域とを有する半導体素子

【課題】低いオン抵抗を有するドリフト経路/ドリフト領域を有する、パワー半導体素子を提供する。

【解決手段】半導体基材内に第1の伝導型のドリフト領域2と、半導体基材内にドリフト領域2に隣接して配置され半導体材料からなるドリフト制御領域3と、ドリフト領域2とドリフト制御領域3の間に配置された蓄積誘電体4と、基材領域8と、基材領域8から分離され蓄積誘電体4に隣接するドレイン領域5と、基材領域8によりドリフト領域2から分離されるソース領域9と、ゲート誘電体16により半導体基材から絶縁されソース領域9からドリフト領域2に到るまで基材領域8に隣接して伸びたゲート電極15と、ドレイン領域5と接したドレイン電極11と、ドレイン領域5と相補的にドープされた半導体領域27とを含み、半導体領域27はドレイン電極11とドリフト領域2の間に配置されドレイン電極11に隣接する。

(もっと読む)

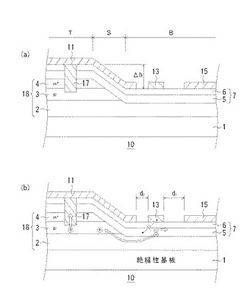

化合物半導体装置及びその製造方法

【課題】イオン注入を用いることなく2次元正孔ガスの所期の濃度分布を容易且つ確実に得て、電界集中のなだらかな緩和を実現する高信頼性の窒化物半導体装置を得る。

【解決手段】n−GaN基板1のN面上に形成されたn−GaN層2と、n−GaN層上に形成されたAlGaNからなるJTE構造10と、n−GaN層2上に形成されたアノード電極4とを有しており、n−GaN層2のJTE構造10との界面に、アノード電極4から離間するほど正孔濃度が低くなるように、2次元正孔ガスが生成される。

(もっと読む)

81 - 100 / 590

[ Back to top ]