Fターム[4M104FF31]の内容

Fターム[4M104FF31]の下位に属するFターム

電極下の複数導電型部(ガードリングを除く) (230)

Fターム[4M104FF31]に分類される特許

101 - 120 / 590

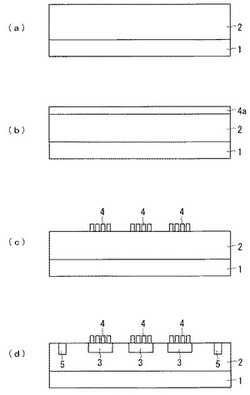

炭化珪素ジャンクションバリアショットキーダイオードおよびその製造方法

【課題】炭化珪素ジャンクションバリアショットキーダイオードの製造において、ハードマスクを使用せずに、pウェル上に選択的にp+領域を形成し、また金属電極とp+領域とコンタクト抵抗を低減する。

【解決手段】n型のエピタキシャル層2の上部全体に高温イオン注入によってp+領域4aを形成し、当該p+領域4aを選択的にエッチングしてp+領域4a下のn型領域を部分的に露出させることにより、そのn型領域の上面より上方へ突出したp+半導体凸部4を形成する。アノード電極は、上記のn型領域の露出した部分およびp+半導体凸部4を覆うように形成される。

(もっと読む)

化合物半導体装置

【課題】高耐圧特性と低オン抵抗特性とを両立した化合物半導体装置を実現する。

【解決手段】化合物半導体装置を、キャリア走行層2及びキャリア供給層3を含む窒化物半導体積層構造4と、窒化物半導体積層構造の上方に設けられたソース電極5及びドレイン電極6と、窒化物半導体積層構造の上方のソース電極とドレイン電極との間に設けられたゲート電極7と、ゲート電極とドレイン電極との間に少なくとも一部が設けられたフィールドプレート8と、窒化物半導体積層構造の上方に形成された複数の絶縁膜9、10とを備えるものとし、フィールドプレートとドレイン電極との間でゲート電極の近傍よりも複数の絶縁膜の界面の数を少なくする。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】耐圧特性の低下やゲートリーク電流の増加を生じることなく、低抵抗で高速動作可能なヘテロ接合電界効果型トランジスタおよびその製造方法を提供する。

【解決手段】ヘテロ接合FETの製造方法に関し、(a)チャネル層3及びチャネル層3上に形成されたバリア層4を窒化物半導体層として準備する工程と、(b)窒化物半導体層上に不純物拡散源としてZnO膜9を形成する工程と、(c)ZnO膜9上のドレイン電極6及びソース電極5を形成すべき領域以外に酸化膜10を形成する工程と、(d)窒化物半導体層に対して熱処理を行い、酸化膜10が形成されていない領域の下部のチャネル層3及びバリア層4に選択的に、ZnO膜9からZn及びOを拡散させる工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート動作に関与する結晶表面における表面電荷蓄積を大幅に低減し、ピンチオフ特性が得られる、高性能のInN系FETを提供すること。

【解決手段】チャネル層としてInN系半導体を含む電界効果トランジスタである半導体装置であって、InN系半導体でなるチャネル層2の表面(c面)に、段差を形成して窒化物半導体の六方晶結晶のa面もしくはm面でなる側壁面2aを形成し、この側壁面2aにゲート電極6が配置され、ゲート電極6を挟むようにソース電極3とドレイン電極4がc面上に形成されている。

(もっと読む)

半導体基板、半導体装置、および半導体基板の製造方法

【課題】GaN系半導体は、面方位が(111)のシリコン基板上にエピタキシャル成長される。GaNの格子定数と、とシリコン(111)面の格子定数の差が、約17%と大きいのでめ、成長されたGaNには1010cm−2を超える転位が導入される。転位により、GaNを用いたトランジスタのリーク電流が増大する。また、トランジスタの移動度が低下する。

【解決手段】シリコン基板と、シリコン基板の(150)面上に、エピタキシャル成長された窒化物半導体層と、を備える半導体基板を提供する。

(もっと読む)

半導体装置

【課題】 オン抵抗の増大を抑制しつつ、耐圧の低下を抑制する技術を提供する。

【解決手段】 ノーマリオフ型の半導体装置100は、ヘテロ接合を構成する半導体層16と、第1リセス部8と、第1リセス部8よりも浅い第2リセス部4と、ゲート部5を備えている。半導体層16は、第1半導体層12と、第1半導体層12上に設けられているとともに第1半導体層12よりもバンドギャップが広い第2半導体層14を有している。第2リセス部4は、第2半導体層14を貫通していない。第2リセス部4の下方に位置する第2チャネル部C2は、第1リセス部8の下方に位置する第1チャネル部C1よりも電流経路20の上流側に配置されている上流側第2チャネル部C2uを有する。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

ダイオードを含む半導体装置

【課題】ダイオードを含む半導体装置において、ダイオードの逆回復挙動とオン状態特性とのトレードオフを改善する。

【解決手段】半導体装置200は陰極216と陽極218を含む。陽極は第1のp型半導体陽極領域204と第2のp型半導体陽極領域206を含む。第1のp型半導体陽極領域204は陽極接触領域218に電気的に接続される。第2のp型半導体陽極領域206は、第2のp型陽極領域と陽極接触領域218間を電気的に接続または切断するように構成された、MOSFET228等のスイッチを介し陽極接触領域218に電気的に接続される。

(もっと読む)

半導体装置

【課題】本発明は、高電界での耐圧を確保でき、かつ絶縁破壊を抑制できる終端構造を有する半導体装置の提供を目的とする。

【解決手段】本発明にかかる半導体装置は、ドリフト領域2表面において、平面視でSBD電極5を囲むように形成された、リセス構造3と、リセス構造3底面内に形成され、SBD電極5と接続された、ガードリング注入層4と、リセス構造3に沿って、少なくともリセス構造3を覆って形成された、保護膜7と、保護膜7に沿って、保護膜7上に形成された、半絶縁膜20とを備え、半絶縁膜20は、リセス構造3が囲む領域の内側においてSBD電極5と接続される接続部21と、リセス構造3が囲む領域の外側においてドリフト領域2と接続される接続部22とを備える。

(もっと読む)

チャネルエッチ型薄膜トランジスタとその製造方法

【課題】半導体層の膜厚均一性を向上させたチャネルエッチ型TFTとその製造方法を提供する。

【解決手段】酸化物半導体からなるチャネル層4を形成した後、該チャネル層4の上にIn、Zn、Gaを含む酸化物からなり、上記酸化物半導体よりもエッチングレートが速く、抵抗率が3.38×107Ωcm以下である犠牲層5を形成し、その上にソース電極6及びドレイン電極7を形成して、該ソース電極6とドレイン電極7の間に露出した犠牲層5をウェットエッチング除去することにより、半導体層膜厚の均一性を向上させ、TFT特性とその均一性と、をより向上させることができる。

(もっと読む)

MOSトランジスタおよびその製造方法

【課題】ドレイン端側においてゲート絶縁膜の膜厚を増大させる構成のMOSトランジスタにおいて、オン抵抗を低減し、耐圧を向上させる。

【解決手段】高電圧トランジスタ10のゲート電極構造をチャネル領域CHを第1の膜厚で覆う第1のゲート絶縁膜12G1と、第1の膜厚よりも大きい第2の膜厚で覆う第2のゲート絶縁膜12G2とし、第1のゲート絶縁膜12G1上の第1のゲート電極13G1と、第2のゲート絶縁膜12G2上の第2のゲート電極13G2の構成とする。更に、第1のゲート電極13G1と前記第2のゲート電極13G2とは、前記第1のゲート絶縁膜12G1から延在する絶縁膜12HKで隔てられる。

(もっと読む)

超高速リカバリダイオード

【課題】ソフトリカバリ特性を維持する逆回復電荷を低減した高速リカバリダイオードを提供する。

【解決手段】整流装置100は、第1の極性の基板と、基板に結合された第1の極性の低濃度ドープ層180と、低濃度ドープ層と共に配置された金属層140とを備える。超高速リカバリダイオードは、互いに離間され、低濃度ドープ層内に形成され、第2の極性のドーピングを備える複数のウェル150を含む。複数のウェルは金属層130に接続する。超高速リカバリダイオードは、複数のウェルのウェル間に位置し、低濃度ドープ層より高濃度に第1の極性がドープされた複数の領域160をさらに含む。

(もっと読む)

ショットキーダイオードおよびその製造方法

【課題】 強誘電体層を有し、逆方向バイアス電圧印加時のリーク電流を低減させ、順方向バイアス電圧印加時の電圧降下を小さくすることができるショットキーダイオードを提供する。

【解決手段】 ショットキーダイオード1は、支持基板11を備え、さらに、支持基板11の表面上に形成された絶縁膜12と、絶縁膜12上に形成された密着層13と、密着層13上に形成されたショットキー金属層14と、ショットキー金属層14の表面上に、ショットキー金属層14とショットキー接触されるように形成され、Mnが添加された第一の誘電体層15と、第一の誘電体層15の表面上に形成され、Mnなどの添加物が添加されていない第二の誘電体層16と、第二の誘電体層16上に、第二の誘電体層16とオーミック接触するように形成されたオーミック金属層17を備えている。

(もっと読む)

異種材料接合型ダイオード及びその製造方法

【課題】電流電圧特性を維持しつつ、アノード電極6の剥離に対する機械的強度を向上させる。

【解決手段】異種材料接合型ダイオードは、半導体基体1と、半導体基体1の上に形成された第1導電型のドリフト領域2と、ドリフト領域2の主表面に接合された、ドリフト領域2とは異なる種類の材料からなるアノード電極6と、半導体基体1に接続されたカソード電極7とを備える。ドリフト領域2とアノード電極6との接合によりダイオードが形成されている。アノード電極6の主表面のうち、ドリフト領域2に接している側の主表面に、嵌合構造(3、G1)が形成されている。

(もっと読む)

半導体装置

【課題】電流コラプスの発生を抑制できるIII族窒化物半導体トランジスタおよびその製造方法を提供する。

【解決手段】FET1では、第1窒化物半導体層103の上に第2窒化物半導体層104が設けられ、少なくとも一部が第2窒化物半導体層104に接するようにソース電極106およびドレイン電極107が設けられている。第2窒化物半導体層104の上面においてソース電極106とドレイン電極107との間に位置するように凹部110aが形成されており、ゲート電極108が凹部110aの開口を覆うように凹部110aの上方に設けられている。

(もっと読む)

酸化膜電界効果トランジスタおよびその製造方法

【課題】デバイス特性のばらつきを抑制しつつ、耐久性を向上可能なSiC系酸化膜電界効果トランジスタ、およびデバイス特性のばらつきを抑制することが可能なSiC系酸化膜電界効果トランジスタの製造方法を提供する。

【解決手段】MOSFET1は、n+SiC基板10と、n−SiC層20と、pウェル21と、n+ソース領域22と、絶縁層35とを備えている。一方のpウェル211および他方のpウェル212においては、pウェル21の中に配置される第1n+ソース領域221と、pウェル21の内部からpウェル21の外部にまで延在する第2n+ソース領域222とが、チャネル領域29を挟んで互いに対向するように配置されている。絶縁層35の厚みは、pウェル21の内部に位置するチャネル領域29上よりも、ウインドウ領域28上において大きくなっている。

(もっと読む)

半導体素子およびその製造方法

【課題】異種基板上に高品質半導体結晶からなる島状のGaN系半導体層を基板の湾曲を抑えて成長させることができ、しかもGaN系半導体層が極めて厚くてもクラックなどの発生を抑えることができ、大面積の半導体素子を容易に実現することができる半導体素子およびその製造方法を提供する。

【解決手段】半導体素子は、GaN系半導体と異なる物質からなる基板11と、基板11上に直接または間接的に設けられ、一つまたは複数のストライプ状の開口12aを有する成長マスク12と、成長マスク12を用いて基板11上に(0001)面方位に成長された一つまたは複数の島状のGaN系半導体層13とを有する。成長マスク12のストライプ状の開口12aはGaN系半導体層13の〈1−100〉方向に平行な方向に延在している。

(もっと読む)

パワー半導体デバイスおよびその製造方法

【課題】改善されたパワーデバイスに加えてそれらの製造方法,パッケージ化の実施例を提供する。1実施例としては、シールドされたゲートトレンチMOSFETにおいて、多くの電荷調整技術と寄生容量を低減する他の技術とを組み合わせて、改善された電圧性能,速いスイッチング速度および低いオン抵抗を有するパワーデバイスを提供する。

【解決手段】シールドポリ311の上にゲートポリ310を含み、垂直方向電荷制御のために、ゲートトレンチ302より深い位置にある非ゲートトレンチを含み、電荷制御トレンチ301は、トレンチの最上部でソース金属に接続する導電材料の単層を有し得るが、独立してバイアスがかけられ、多重に積み重ねられたポリ電極313を使用する。また、デュアルゲート構造を用いることによってゲートとドレインとの間の容量Cgdを低減する。

(もっと読む)

半導体装置の製造方法

【課題】トレンチMOSゲート構造とこの構造を取り囲む第2トレンチの底部に形成する絶縁膜を厚膜化する半導体装置の製造方法を提供すること。

【解決手段】n型基板表面に、離間する複数の第1トレンチと、より幅が広く第1トレンチを囲む第2トレンチとを形成する第1工程と、第1、第2トレンチの内面にゲート酸化膜を形成する第2工程と、第1トレンチ幅の二分の一以上の厚さの導電材料を堆積する第3工程と、ゲート酸化膜を停止層として導電材料を除去する第4工程と、ゲート酸化膜より厚い絶縁膜を形成する第5工程と、CMPで絶縁膜表面を研磨しn型基板と第1トレンチ表面の導電材料を露出させる第6工程と、前記露出したn型基板表面とショットキー接合をなす電極膜を形成する第7工程と、第2トレンチ内部の厚い絶縁膜上で前記電極膜の外周部を除去する第8工程とを有する半導体装置の製造方法。

(もっと読む)

101 - 120 / 590

[ Back to top ]