Fターム[4M104FF37]の内容

Fターム[4M104FF37]に分類される特許

1 - 20 / 21

半導体装置

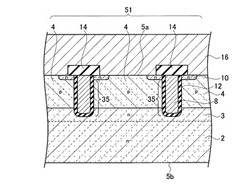

【課題】接合終端領域における電界を緩和し、高耐圧化可能な半導体装置を提供する。

【解決手段】第1導電型の不純物を有する第1半導体領域と、第1半導体領域上に配置された、第1導電型と異なる第2導電型の第2半導体領域とを有する半導体基体には、コレクタ電極若しくはドレイン電極を有するスイッチング素子が形成された素子領域と、上方から見て半導体基体の最外周部に形成された、第2半導体領域の上面から第1半導体領域に達する終端トレンチと、終端トレンチの側壁および底面に形成された絶縁膜と、絶縁膜を介して溝の内側に埋め込まれた電極とを有し、溝の内側に埋め込まれた電極が第1半導体領域又はコレクタ領域若しくはドレイン電極と接続された等電位リングである。

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

SiC半導体素子の製造方法

【課題】薄板化に伴うSiC基板の反りを修正するSiC半導体素子の製造方法の提供を目的とする。

【解決手段】本発明の半導体素子の製造方法は、(a)表面側に素子活性領域が形成されたSiC基板1を準備する工程と、(b)SiC基板1の表面を平坦面に固定し、裏面を研削する工程と、(c)SiC基板1の表面を平坦面に固定したまま、研削によるSiC基板の反りを相殺する応力を付与する内部応力層を、SiC基板内部に形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、簡素な製造工程でありながら、ボイドを発生させずにトランジスタセルの高密度化を実現する半導体装置の製造方法を提供することを目的とする。

【解決手段】半導体層60にトレンチ型のゲート90が形成され、該ゲート90の両側に拡散層50が形成されたトランジスタセルを複数含むセル部61と、該セル部61を囲むガードリング部62とを有する半導体装置の製造方法であって、

前記ゲート90及び前記拡散層50が形成された前記半導体層60の表面に、層間絶縁膜120を形成する工程と、

前記セル部61に形成された前記層間絶縁膜120を、エッチバックにより薄膜化する工程と、

前記層間絶縁膜120の前記拡散層50上の位置に、孔状又は溝状のコンタクト部130を形成する工程と、

前記層間絶縁膜120上に、金属膜140を形成する工程と、を含むことを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】製造が容易で、かつ高い耐圧を確保しながら低損失化を図ることができる半導体装置を提供すること、およびその半導体装置を製造するための製造方法を提供する。

【解決手段】半導体装置としてのショットキーダイオード10は、半導体からなる基板11と、基板11上に形成されたn型層12とを備えている。n型層12は基板11側の表面である第1の面12Aとは反対側の表面である第2の面12Bから第1の面12Aに向けて延びるように形成された溝13を有している。溝13の底部である底壁13Aに接触する位置には絶縁体としての酸化物層14が配置されており、かつ溝13の側壁13Bに接触するようにn型層12とショットキー接触可能な金属膜15が溝13を埋めるように形成されている。さらに、n型層12の第2の面12Bに接触するようにアノード電極16が配置されている。

(もっと読む)

半導体装置

【課題】IGBTとセットでFWダイオードとして使用される単体のショットキ・バリア・ダイオードにおいては、半田層を介して、表面のアノード電極をメタル・クリップに接続するケースが多い。この場合、アルミニウム系アノード電極上のポリイミド系ファイナル・パッシベーション膜の開口上にUBM層を設けるが、UBM層およびポリイミド系膜がともに、引っ張り応力を有するため、下地のアルミニウム系膜に両引っ張り応力によるクラックが発生する。

【解決手段】本願発明は、半導体基板の主面に設けられたSBDの活性領域および、その端部から外側の周辺部に設けられたPSG膜被覆領域を有するSBD素子において、アノード電極を構成するアルミニウム系メタル膜上に相補的に設けられた有機系ファイナル・パッシベーション膜とUBM層の境界部分をPSG膜被覆領域に設けたものである。

(もっと読む)

半導体装置の製造方法

【課題】保護素子としてSBDを搭載したMOSFETにおいては、SBDの特性を確保するためアルミニウム・ソース電極下のアルミニウム拡散バリア・メタル膜として、TiW(タングステンを主要な成分とする合金)膜が使用される。しかし、本願発明者らが検討したところによると、タングステン系バリア・メタル膜はTiN等のチタン系バリア・メタル膜と比べて、バリア性が低い柱状粒塊を呈するため、比較的容易にシリコン基板中にアルミニウム・スパイクが発生することが明らかとなった。

【解決手段】本願発明は、アルミニウム系メタル層と下層のシリコン系半導体層の間のバリア・メタル層として、タングステン系バリア・メタル膜をスパッタリング成膜によって形成する際、その下層をウエハ側にバイアスを印加したイオン化スパッタにより成膜し、上層をウエハ側にバイアスを印加しないスパッタにより成膜するものである。

(もっと読む)

半導体装置

【課題】パワー半導体装置における高耐圧化と小型化とを両立できる半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ガードリングによるターミネーション領域を有する高耐圧パワー半導体装置であって、能動領域は第1のバリアメタル層を介して第1の電極と接合され、前記ガードリングは第2のバリアメタル層を介して第2の電極と接合され、チャネルストッパは第3のバリアメタル層を介して第3の電極と接合されている。前記バリアメタル層は各々に間隔をあけて配設され、前記ターミネーション領域を横断する方向において、前記各バリアメタル層(第1乃至第3のバリアメタル層)の幅は接合する前記各電極(第1乃至第3の電極)の幅よりも広く、かつ前記各バリアメタル層の一部が前記接合する各電極の前記横断する方向における両側からはみ出していることを特徴とする。

(もっと読む)

半導体装置、電力変換装置及び半導体装置の製造方法

【課題】RCスナバ回路の抵抗Rの値を任意に設計可能な半導体スナバ回路を用いた半導体装置、電力変換装置、半導体装置の製造方法を提供する。

【解決手段】ユニポーラ動作をする還流ダイオード100と、還流ダイオード100に並列接続され、キャパシタ210及び抵抗220をモノリシックに集積化した半導体スナバ回路200とを備える半導体装置において、抵抗220が、半導体スナバ回路200の基材となる半導体基体の一部に形成され、半導体基体の比抵抗よりも高い比抵抗を有する高抵抗層を含む。

(もっと読む)

半導体装置

【課題】ガードリングを越えて半導体チップ内に水分が浸入した場合でも、半導体チップ上の1つの電極と他の1つの電極との短絡を抑制すること。

【解決手段】半導体チップ10と、半導体チップ10上に配置された電極パッド14、16と半導体チップ10の外周との間に配置された導電性のガードリング18と、ガードリング18の一部領域を排することで、ガードリング18を互いに絶縁された複数の単位領域に分割するための、複数のガードリング絶縁部60と、を有する半導体装置。

(もっと読む)

JBSの製造方法

【課題】N型ショットキー接合界面にPtまたはAuが到達してしまうおそれを低減する。

【解決手段】N+型半導体基板1上のN−型エピタキシャル層2に複数のトレンチ2aを形成し、トレンチ2aの側面2a1および底面2a2を介してP型不純物を導入して拡散させることにより、ガードリング部4とP型層5とを形成し、トレンチ2aの側面2a1上および底面2a2上に酸化膜3を形成し、酸化膜3のうち、トレンチ2aの底面2a2に隣接する部分に開口2bを形成し、半導体チップの表面全体にPtまたはAu7を蒸着し、蒸着されたPtまたはAu7の上からポリシリコン8を堆積させてトレンチ2aの内部にポリシリコン8を充填し、トレンチ2aの底面2a2の開口3bを介してPtまたはAu7をトレンチ2aの底面2a2の下方に拡散させる。

(もっと読む)

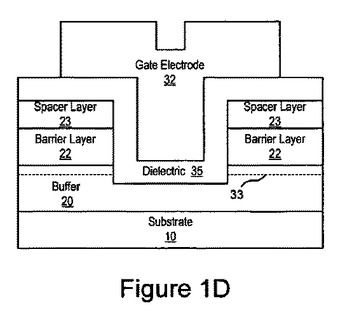

常時オフ半導体デバイスおよびその作製方法

常時オフ半導体デバイスが提供される。III族窒化物バッファ層が提供される。III族窒化物バリア層がIII族窒化物バッファ層上に設けられる。非伝導性スペーサ層がIII族窒化物バリア層上に設けられる。III族窒化物バリア層およびスペーサ層がエッチングされてトレンチを形成する。トレンチはバリア層を貫いて延びてバッファ層の一部を露出させる。誘電体層がスペーサ層上およびトレンチ内に形成され、ゲート電極が誘電体層上に形成される。半導体デバイスの形成に関連する方法も提供される。  (もっと読む)

(もっと読む)

半導体装置

【課題】高耐圧を得ることのできる窒化物半導体を用いたショットキーバリアダイオードを含む半導体装置を提供する。

【解決手段】半導体装置は、n+型半導体基板1と、n+型半導体基板1の上面上に設けられたn−型ドリフト領域2と、n−型ドリフト領域2の上面上に設けられ、n−型ドリフト領域2とショットキー接合Aを形成するアノード電極3と、n+型半導体基板1に電気的に接続されたカソード電極4とを備える。半導体装置は、n−型ドリフト領域2の表面に選択的に設けられたトレンチ5を備え、トレンチ5は、アノード電極3により埋め込まれている。

(もっと読む)

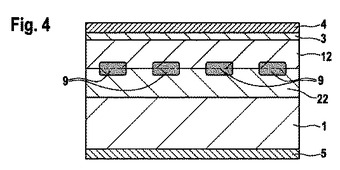

半導体装置および同半導体装置の製造方法

本発明は、高濃度nドープシリコン基板(1)と第1のn型シリコンエピタキシャル層(22)とから成る半導体装置であって、第1のn型シリコンエピタキシャル層(22)は高濃度nドープシリコン基板(1)に直に接しており、pドープSiGe層(3)が第2のn型シリコンエピタキシャル層(12)に接し、ヘテロ接合ダイオードを形成しており、ヘテロ接合ダイオードは第1のn型シリコンエピタキシャル層(22)の上にあり、ヘテロ接合ダイオードにおいてpn接合はpドープSiGe層(3)の内部にある。第1のn型シリコンエピタキシャル層(22)は第2のn型シリコンエピタキシャル層(12)よりも高いドーパント濃度を有している。2つのn型シリコンエピタキシャル層の間には少なくとも1つのpドープエミッタウェル(9)があって、埋め込みエミッタを形成しており、第1のn型シリコンエピタキシャル層(22)と第2のn型シリコンエピタキシャル層(12)とへのpn接合が形成されており、少なくとも1つのエミッタウェル(9)は2つのエピタキシャル層によって完全に包囲されている。  (もっと読む)

(もっと読む)

ショットキーバリアダイオード、検波回路、及び製造方法

【課題】高周波の信号に応じて精度よく動作するショットキーバリアダイオードを提供する。

【解決手段】半導体材料に不純物が添加された高濃度不純物層と、高濃度不純物層の上面に形成され、半導体材料に添加される不純物の濃度が高濃度不純物層より低い低濃度不純物層と、金属材料で形成され、低濃度不純物層と接触して設けられたアノード端子と、高濃度不純物層の上面において低濃度不純物層の周囲を囲むように設けられ、高濃度不純物層とオーミック接触するガードリングと、ガードリングと接触するカソード電極とを備えるショットキーバリアダイオードを提供する。

(もっと読む)

電界緩和機能を有するIII族窒化物電力半導体

素子の耐圧性を改善するために、ゲートの周囲の電界を緩和する電界緩和機能を含むIII族窒化物電力半導体素子。 (もっと読む)

半導体装置

【課題】 ドレイン電極から「ゲート電極下とドレイン領域との境界部分」への電界を多少でも抑えて、更なる高耐圧化を可能とした半導体装置を提供する。

【解決手段】 LOCOSオフセット構造のMOSトランジスタ100をシリコン基板1に有する半導体装置であって、ソース電極21はゲート電極11の上方まで延ばされ、かつ第2ドレインプラグ33のうちの少なくともゲート電極11側を包囲するように形成されている。このような構成であれば、第2ドレインプラグ33のソース電極21によって包囲された部分の電界はソース電位に引き付けられ、包囲された部分から「ゲート電極11下とドレイン領域5との境界部分」への電界がある程度抑えられる。

(もっと読む)

半導体素子

【課題】 発振のS/N比を向上させ、安定した波形の低周波発振を可能とする半導体素子を提供する。

【解決手段】 低周波発振半導体素子10は、半導体基板1と、半導体基板1の裏面に接して配置された裏面電極4と、半導体基板1の表面に接し、平面的に見て裏面電極4と重なるように形成されたパッド電極2とを備えている。パッド電極2の垂直真下の領域Aに存在する半導体基板1の表面のエッチピット密度が0または3×104/cm2以上6×104/cm2以下である。

(もっと読む)

双方向フォトサイリスタチップ、光点弧カプラ、および、ソリッドステートリレー

【課題】転流特性の向上を図る。

【解決手段】 双方向フォトサイリスタチップ31の2つの動作チャンネルCH1,CH2が、交差しないように、互いに分離して配置されている。そして、N型シリコン基板上における左側のPゲート拡散領域23と右側のPゲート拡散領域23'との間であって、CH1とCH2との間に、リンがドープされた酸素ドープ半絶縁多結晶シリコン膜35aでなるチャネル分離領域29が形成されている。したがって、上記N型シリコン基板の表面におけるチャネル分離領域29近傍のシリコン界面準位(Qss)が増大し、N型シリコン基板内の少数キャリアである正孔が上記領域において消滅する。その結果、CH1がオフした時点でCH2側に逆位相の電圧が印加された場合に光入射が無いにも拘わらずCH2がオンする転流失敗を防止することができ、転流特性を向上できる。

(もっと読む)

半導体装置およびその製造方法

【課題】

従来のアルミ配線の場合、上述の横応力がアルミ配線にかかり、次第にアルミ配線が傾く。さらに、大きな応力を受けると配線が根元からスライドし、クラックが入るなどして、期待する特性を得られなくなることがある。

【解決手段】

第1の厚さを有する周辺部及び第1の厚さよりも薄い第2の厚さを有する配線形成部を有し、底面が同一である半導体基板10と、半導体基板10の配線形成部上に形成されたアルミ配線層と、を有し、配線形成部が前記周辺部に隣接して配置されている半導体装置である。

(もっと読む)

1 - 20 / 21

[ Back to top ]